鉛酸電池內部結構與工作原理詳細介紹

2009-11-24 17:43:39 45035

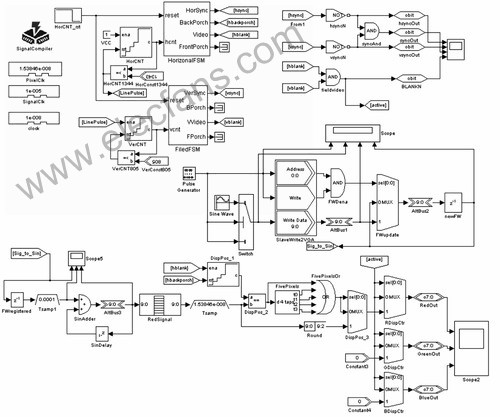

45035 表。 這4類路徑中,我們最為關心是②的同步時序路徑,也就是FPGA內部的時序邏輯。 時序模型 典型的時序模型如下圖所示,一個完整的時序路徑包括源時鐘路徑、數據路徑和目的時鐘路徑,也可以表示為觸發器+組合邏輯+觸發器的模型。 該

2020-11-17 16:41:52 3687

3687

在高速系統中FPGA時序約束不止包括內部時鐘約束,還應包括完整的IO時序約束和時序例外約束才能實現PCB板級的時序收斂。因此,FPGA時序約束中IO口時序約束也是一個重點。只有約束正確才能在高速情況下保證FPGA和外部器件通信正確。

2022-09-27 09:56:09 2396

2396 在FPGA設計中,時序約束的設置對于電路性能和可靠性都至關重要。在上一篇的文章中,已經詳細介紹了FPGA時序約束的基礎知識。

2023-06-06 18:27:13 12758

12758

在FPGA設計中,時序約束對于電路性能和可靠性非常重要。在上一篇的文章中,已經詳細介紹了FPGA時序約束的主時鐘約束。

2023-06-12 17:29:21 4240

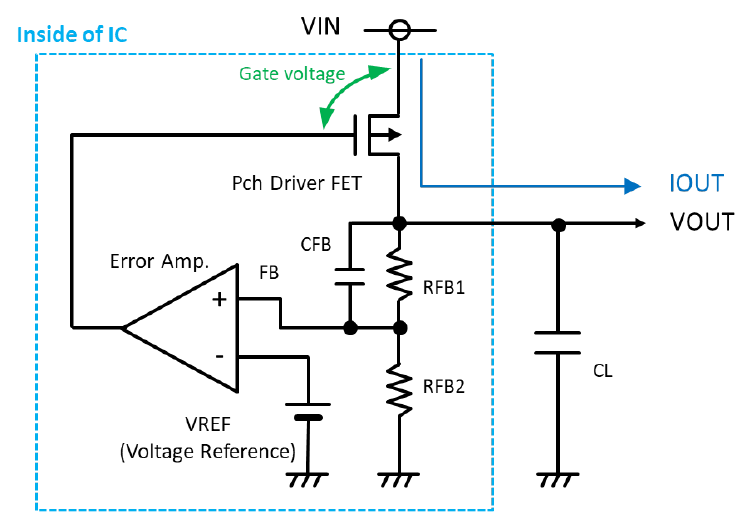

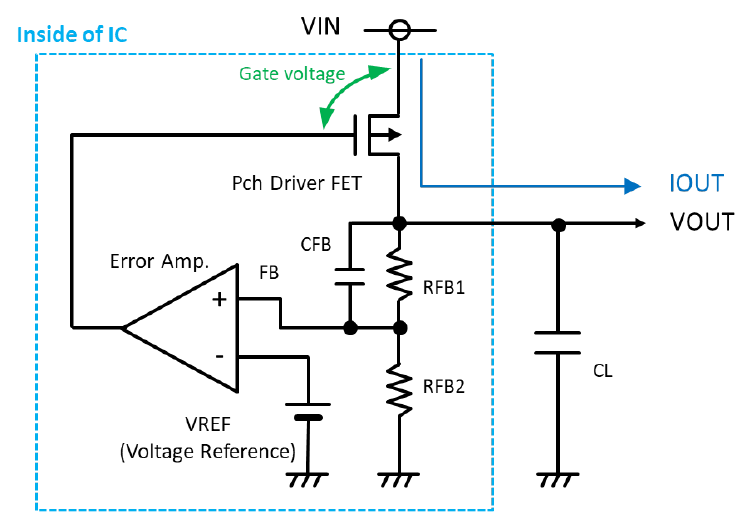

4240 為了進一步理解線性型電壓穩壓器的工作原理,首先考慮IC內部的各模塊構成和作用。

2023-12-05 10:28:57 3348

3348

LDO(Low Dropout Regulator)是一種低壓差線性穩壓器,它能夠提供穩定的輸出電壓,同時具有較低的功耗和噪聲。本文將詳細介紹LDO的內部結構和工作原理,包括其電路組成、工作原理

2023-12-14 14:37:54 4802

4802 在數字IC/FPGA設計的過程中,對PPA的優化是無處不在的,也是芯片設計工程師的使命所在。此節主要將介紹performance性能的優化,如何對時序路徑進行優化,提高工作時鐘頻率。

2025-12-09 10:33:20 2967

2967

結果當然是要求系統時序滿足設計者提出的要求。

下面舉一個最簡單的例子來說明時序分析的基本概念。

假設信號需要從輸入到輸出在FPGA 內部經過一些邏輯延時和路徑延時。我們的系統要求這個信號在 FPGA 內部

2024-06-17 17:07:28

FPGA中幾個基本的重要的時序分析參數介紹(fmax\tsu\th\tco\tpd)今天無聊,翻開書偶看到介紹時序部分的東西,覺得其中幾個參數縮寫所代表的含義應該記住,故寫如下文章……FPGA中

2012-04-09 09:41:41

FPGA中的I_O時序優化設計在數字系統的同步接口設計中, 可編程邏輯器件的輸入輸出往往需要和周圍新片對接,此時IPO接口的時序問題顯得尤為重要。介紹了幾種FPGA中的IPO時序優化設計的方案, 切實有效的解決了IPO接口中的時序同步問題。

2012-08-12 11:57:59

模塊,這些模塊間利用金屬連線互相連接或連接到I/O模塊。FPGA的邏輯是通過向內部靜態存儲單元加載編程數據來實現的,存儲在存儲器單元中的值決定了邏輯單元的邏輯功能以及個模塊之間或模塊與I/O間的連接

2012-07-19 21:19:16

的FPGA都是基于SRAM工藝的,需要在使用時外接一個片外存儲器以保存程序。上電時,FPGA將外部存儲器中的數據讀入片內RAM,完成配置后,進入工作狀態;掉電后FPGA恢復為白片,內部邏輯消失。這樣

2023-05-30 20:53:24

模塊,這些模塊間利用金屬連線互相連接或連接到I/O模塊。FPGA的邏輯是通過向內部靜態存儲單元加載編程數據來實現的,存儲在存儲器單元中的值決定了邏輯單元的邏輯功能以及各模塊之間或模塊與I/O間的聯接

2012-03-16 10:05:11

主要是針對初級的FPGA愛好者對 FPGA入門知識進行簡單的總結,FPGA入門需要了解FPGA的工作原理、基本特點、以及FPGA芯片的構成和功能模塊等各個方面。希望通過閱讀筆者的這篇FPGA入門知識介紹文章可以對想要了解FPGA的您有所幫助。

2014-08-16 10:32:45

VGA驅動接口時序設計之1概述本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 第六章第8節中我們給出

2015-07-26 21:56:45

-name LCD_CLK -source[get_ports {vga_clk}]這個虛擬時鐘將會在FPGA內部對tx_data的reg2pin進行時序分析時作為latch時鐘。實際對于一般的reg2reg

2015-07-30 22:07:42

的約束,來控制這些內部的時序延時,使得前面給出的兩個基本公式得到滿足。但是,FPGA并不知道這兩個公式中FPGA外部的路徑延時參數,所以我們下一步的數據路徑約束要做的就是把這些參數告訴FPGA

2015-08-02 19:26:19

直接就連接到了驅動FPGA內部模塊的時序產生時鐘信號,所以它的偏斜其實就是PLL輸出的這個時鐘信號到引腳的延時值。因為這個路徑其實也應該算在了reg2pin的時序路徑中,如果不做約束系統不會對其進行

2015-08-06 21:49:33

開發板,熱銷中!SANXIN-B01 Verilog教程-郝旭帥團隊電子版FPGA工程師就業班,線上直播課開啟!VGA(Video Graphics Array)視頻圖形陣列是 IBM 于1987年提出

2023-03-22 16:51:57

machineASM)。計數器的時序電路如下: 圖12 :計數器(自加一)電路結構 思考 :分析計數器(自加一)工作原理? 寄存器(Register)用于寄存一組二值代碼,它被廣泛地用于各類數字系統和數字計算機中

2023-02-22 17:00:37

最近要用FPGA做一個驅動CRT顯示器的程序,場頻要求比較高,大于vesa標準的85Hz,甚至要150Hz,但是時序標準找不到呀,故現求助各路大神了!!菜鳥在這先謝過了!

2014-03-25 11:27:28

VGA顯示原理與VGA時序實現

2012-08-15 16:57:38

fpga的工作原理一.查找表(Look-Up-Table)的原理與結構 采用這種結構的PLD芯片我們也可以稱之為FPGA:如altera的ACEX,APEX系列,xilinx

2008-05-20 09:46:10

vesa標準Intellectual Property? Copyright 1994, 1995, 1996, 1998 – 2004 Video Electronics Standards

2008-08-08 13:20:34

AD7147內部校準邏輯電路的工作原理是什么?是否其在做環境補償時,是有一個內部的標準電容作為參考?

2023-12-12 08:24:29

的菊花鏈特性允許多個ADC和一個串行接口連接。由于在電力繼電保護產品中以并行接口連接設計為主,所以下面將以并行接口的連接方式介紹其工作原理。 圖2 AD7656并行接口模式時的轉換時序圖首先,通過

2011-01-02 13:55:52

VGA。請問假如我將VGA的時序已經做好了,按照VESA標準,那么發給ADV7343,ADV7343能否將其轉換為模擬VGA視頻信號?(7343能否支持VESA標準?)

進一步補充,使用ADV7343的SD通道產生CVBS,HD通道產生VGA視頻是否可行?

2023-12-13 07:34:00

要實現VGA信號轉成HD/3G SDI(smpte 292M/smpte 424M)

需要一個IC,輸入VGA信號,輸出smpte 292M格式, 然后再用SDI發射器傳輸.

由于VESA

2023-12-25 06:52:39

輸出、VGA輸出、千兆以太網通信、SD卡(與VGA復用IO)功能,模塊上還集成了Arm CMSIS DAP調試器,用于調試編寫到FPGA內部的Cortex-M0軟核。開發板功能和接口介紹模塊插在EG4S20上的正面視圖模塊背面視圖原作者:語雀

2022-07-20 15:24:01

串口通訊是什么?RS-232標準有何作用呢?RS-232電平和TTL電平的區別在哪?USB/TTL轉232模塊的工作原理是什么?

2022-02-16 07:38:11

RS-232的標準是什么?RS232電平與TTL電平的區別是什么?USB/TTL轉232模塊的工作原理是什么?

2022-02-18 07:06:31

這幾天在用FPGA做貪吃蛇的游戲,有關于VGA顯示的模塊,下面分享關于VGA顯示控制的說明:下面有兩個模塊:640*480與800*600,學習VGA的同學可以對比兩個模塊和附件中的VGA時序圖分析

2012-10-14 18:44:13

的標準。例如,微軟Windows系列產品的開機畫面仍然使用VGA顯示模式,這也說明其在顯示標準中的重要性和兼容性。VGA最早指的是顯示器640X480這種顯示模式。(而今天的VGA其實已經不僅僅局限于

2016-04-08 09:55:22

,本實例需要用戶自己準備好一臺VGA顯示器和相應的VGA線,VGA線用于連接SF-SP6開發板的J1插座和顯示器。FPGA內部產生ColorBar以及VGA時序用于驅動顯示器顯示。Vga的驅動大體

2016-04-11 09:51:49

xilinx_fpga結構及工作原理介紹

2012-08-02 22:59:43

下:實現過程:1.將VGA接口接到轉接板,用杜邦線連接攝像頭和開發板,連接準確保證引腳對齊。 2.打開工程編譯后進行引腳分配,引腳分配如下:3.在VIVADO中生成比特流文件后,通過下載器下載到FPGA中

2021-07-30 15:34:58

、B7~B0、3.3V、GND信號。對于用戶來說,只需正確的連接這些信號并給出正確的VGA標準信號即可。該模塊使用2*17雙排針接口,其中左上方為1腳 下圖為模塊接口信號的時序要求: 僅在BLK有效期

2017-06-19 16:41:44

再來看看VGA的行、列同步時序列同步時序行同步時序VGA 中定義行時序和列時序都需要同步脈沖(a 段)、顯示后沿(b 段)、顯示時序段(c 段)和顯示前沿(d 段)四部分。VGA 工業標準顯示模式要求

2019-12-27 22:10:57

418108031105行12401920282000了解了VGA的基本驅動原理,我們還要回來看看實際驅動電路的工作原理。由于FPGA接口都是數字信號,無法直接輸出VGA色彩信號所需的0-0.7V模擬電壓

2016-12-03 17:51:32

連接SF-CY4開發板的J1插座和顯示器。FPGA內部產生ColorBar以及VGA時序用于驅動顯示器顯示。圖8.58 VGA實例功能框圖VGA的驅動大體如圖8.59所示。圖8.59 VGA驅動功能框圖本實例模塊劃分如圖8.60所示。圖8.60 VGA實例模塊層次 `

2018-05-07 18:25:31

。本文采用FPGA+MCU方案,利用了Cyclone系列的FPGA高達上百兆的工作頻率特性為圖像數據處理提供了良好的實時性,其內部集成的數字鎖相環為系統的工作時鐘提供的良好的穩定性,其內部嵌入的存儲器可以

2019-07-17 07:12:48

,成為電腦顯卡上應用最為廣泛的接口類型,絕大多數的顯卡都帶有此種接口。VGA類型的顯示驅動需要比較高的掃面頻率和盡量短的處理時間,因而通過FPGA來實現VGA顯示的驅動和控制非常有效。在FPGA中

2017-08-02 11:40:35

如何有效的管理FPGA設計中的時序問題當FPGA設計面臨到高級接口的設計問題時,EMA的TimingDesigner可以簡化這些設計問題,并提供對幾乎所有接口的預先精確控制。從簡單SRAM接口到高速

2009-04-14 17:03:52

本文介紹了流水線ADC的內部結構和工作原理。

2021-04-22 06:56:00

FPGA外部的芯片,可能是FPGA內部的硬核。對于FPGA design來說,必須要關注在指定要求下,它能否正常工作。這個正常工作包括同步時序電路的工作頻率,以及輸入輸出設備的時序要求。在FPGA

2019-07-09 09:14:48

AD7147的環境時的內部校準邏輯電路的工作原理是什么,是否其在做環境補償時,是有一個內部的標準電容作為參考?

2018-08-08 06:54:11

提示:文章寫完后,目錄可以自動生成,如何生成可參考右邊的幫助文檔文章目錄前言一、超聲波模塊的工作原理二、超聲波的時序圖三、利用STM32F407進行驅動編寫1.定時器配置總結前言 今天我們針對超聲波

2022-02-16 06:02:42

擴展模塊設計的詳細信息,請參閱CEA-861規范。表1. EDID簡介VGA和HDMI的時序格式由上述兩個標準設置組分別定義:VESA和CEA/EIA。VESA時序格式的定義參見“VESA監視時序和協

2018-10-24 09:51:36

點數)×(一場行數+消隱行數)×刷新率。對于標準的VGA接口時序640×480@60Hz而言,時鐘頻率為800×525×60=25.175MHz。在本設計中我們采用1024×768@60Hz的XGA

2019-06-04 05:00:12

介紹了基于FPGA的圖形式LCD&VGA控制器的設計,詳細討論了

2009-07-21 17:25:21 0

0 利用BSP-15 DSP處理器上GPDP實現VGA/XGA信號采集:隨著視頻會議系統應用的擴展,2003年7月,ITU批準了H.239標準。基于此項技術,視頻會議廠商需要得到雙流視頻服務。而作為雙流的新增那

2009-10-01 18:39:05 11

11 本文介紹了基于FPGA/CPLD的嵌入式VGA顯示系統的設計,詳細討論了用VHDL設計行場掃描時序的方法,這種設計方法稍作改動便可產生任意行場掃描時序,具有很好的移植性。該顯示系統

2010-07-28 17:13:22 49

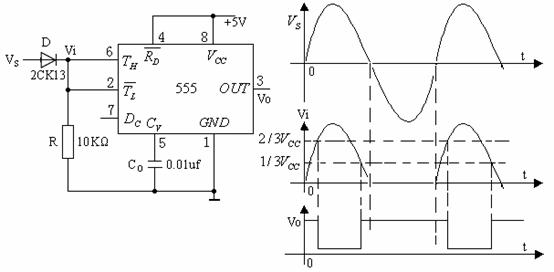

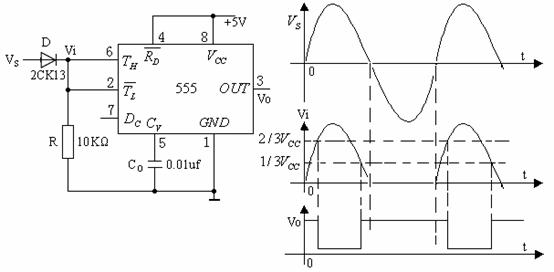

49 本文介紹555定時器內部框圖及電路工作原理:

555定時器內部框圖

555集成時基電路稱為集成定時

2007-11-22 13:00:39 80635

80635

VGA Vesa DDC顯示接口引腳定義圖

VGA 是 Video Graphics Adapter(Array) 的縮寫,VESA 是 Video Electronics Standards Association 的縮寫,DDC 是 Display Data Channel 的縮寫,信號類

2007-11-27 20:17:59 2069

2069

VGA Vesa DDC顯示接口

VGA 是 Video Graph

2009-02-12 10:33:31 4374

4374 如何有效的管理FPGA設計中的時序問題

當FPGA設計面臨到高級接口的設計問題時,EMA的TimingDesigner可以簡化這些設計問題,并提供對幾乎所有接口的預先精確控制。從簡單

2009-04-15 14:19:31 947

947

摘要:介紹了基于FPGA的圖形式LCD&VGA控制器的設計,詳細討論了用VHDL設計行場掃描時序的方法,這種設計方法稍作改動便可產生任意行場掃描時序,具有很好的可重用性。

2009-06-20 13:28:05 1686

1686

VESA發布mDP接口標準,全面支持1.1a標準

視頻電子標準協會(Video Electronics Standards Association, VESA)于日前發布了Mini DisplayPort (mDP) 接口標準,新款小型的接口全面支持DisplayPor

2009-11-23 08:49:37 4641

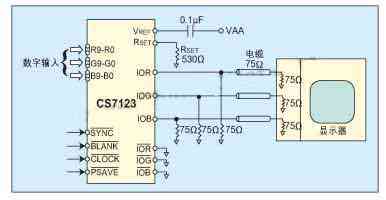

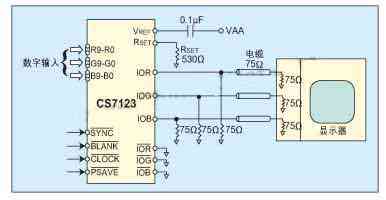

4641 運用CS7123芯片實現VGA/XGA電視盒設計方案

CS7123芯片是深圳市芯海科技有限公司自主設計的高速/高精度視頻DAC芯片,其內部包括三路10位電流導引(Current Steering)結構的DA

2010-02-04 09:55:34 1796

1796

FPGA,FPGA工作原理是什么?

FPGA(現場可編程門陣列)是專用集成電路(ASIC)中集成度最高的一種,用戶可對FPGA內部的邏輯模塊和I/O模塊

2010-03-26 17:07:47 4019

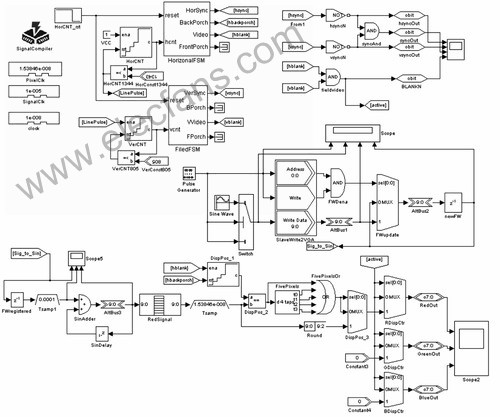

4019 本文基于DSP Builder的VGA接口設計方法,對VGA接口時序和系統設計需求進行了介紹,并在硬件平臺下實現一維與二維信號的顯示。 VGA接口標準 VGA顯

2010-08-03 10:23:40 1533

1533

介紹了采用STA (靜態時序分析)對FPGA (現場可編程門陣列)設計進行時序驗證的基本原理,并介紹了幾種與STA相關聯的時序約束。針對時序不滿足的情況,提出了幾種常用的促進 時序收斂的方

2011-05-27 08:58:50 70

70 本文介紹了基于FPGA(現場可編程門陣列)具有串口控制功能的VGA顯示圖像的設計實現方案。通過對該設計方案進行分析,可把本設計分成3個模塊一一進行實現,這3個模塊分別是串口發

2011-09-19 15:26:51 292

292 一.FPGA工作原理 FPGA 采用了邏輯單元陣列LCA(Logic Cell Array)這樣一個概念,內部包括可配置邏輯模塊CLB(Configurable Logic Block)、輸出輸入模塊IOB(Input Output Block)和內部連線(Interconn

2012-05-12 17:52:44 3566

3566 ,介紹 FPGA 中 SDRAM 控制器的組成和工作流

程 ,給出應用中讀 SDRAM 的時序圖。FPGA 采用模塊化設計 ,增強 SDRAM 控制器的通用性 ,更方便地滿足實際需求。

2015-10-29 14:05:57 2

2 fpga vga 顯示,介紹了如何實現vga的操作以及如何配置

2016-03-15 18:29:06 8

8 Xilinx FPGA工程例子源碼:用FPGA模擬VGA時序PS_2總線的鍵盤接口VHDL源代碼

2016-06-07 15:11:20 33

33 今天給大家介紹一下 STM32 單片機的 DAC 模塊的工作原理,在有的場合,往往需要單片機輸出變化的模擬量,來控制外部的器件來工作,以前我們用的普通 51 單片機內部是沒有 DAC 這個模塊

2016-11-11 17:17:12 84

84 如何有效地管理FPGA設計中的時序問題

2017-01-14 12:49:02 14

14 Xilinx FPGA編程技巧常用時序約束介紹,具體的跟隨小編一起來了解一下。

2018-07-14 07:18:00 5226

5226

一個好的FPGA設計一定是包含兩個層面:良好的代碼風格和合理的約束。時序約束作為FPGA設計中不可或缺的一部分,已發揮著越來越重要的作用。毋庸置疑,時序約束的最終目的是實現時序收斂。時序收斂作為

2017-11-17 07:54:36 2967

2967

的效果,依據該原理,可以實現圖像的采集及在VGA顯示屏上顯示的實現。利用FPGA產生VGA時序信號和發送圖像信息,并將其作為圖像信號采集系統,將大大減小圖像開發的難度和投入。

2017-11-18 12:42:02 2598

2598 VGA 作為一種標準顯示接口,廣泛應用于各種智能控制的顯示終端。伴隨著電子產 業的不斷發展,尤其是高速圖像處理的發展,對可以將實時圖像進行高速處理有了更高的要求。這里根據 VGA 接口的原理,通過

2017-11-30 14:57:27 64

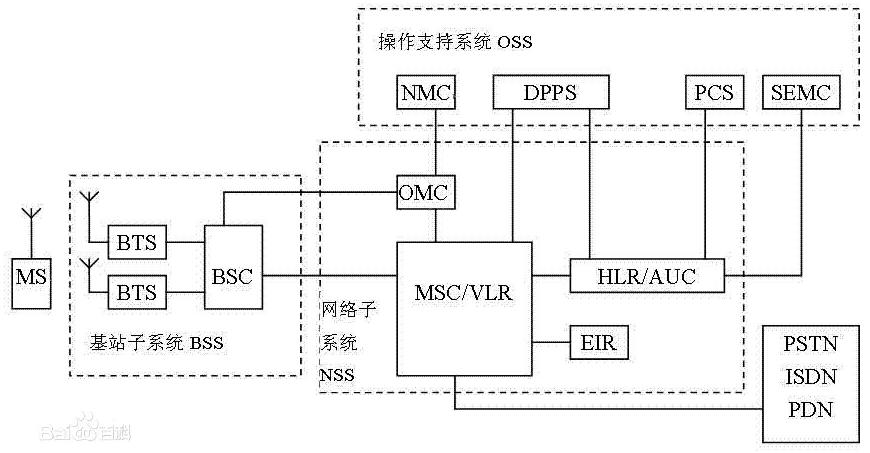

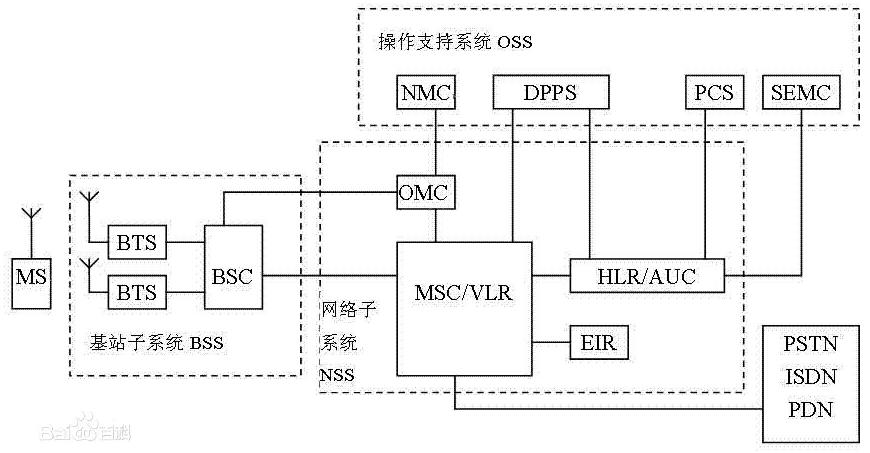

64 本文首先介紹了gsm模塊的概念和gsm系統結構,其次介紹了gsm模塊工作原理與工作模式,最后介紹了五個gsm模塊的典型應用。

2018-05-14 11:28:14 53429

53429

本文主要詳解HC-SR04模塊吉他的工作原理,首先介紹的是HC-SR04模塊的優勢及應用領域,其次闡述了超聲波測距模塊工作原理及電路圖,最后介紹了電氣參數、超聲波時序圖、操作以及程序,具體的跟隨小編來了解一下。

2018-05-17 09:34:48 404249

404249 該文件包括所有當前的VESA監視器計時標準和指南。“指南”與“標準”一樣接受VESA審查和批準過程,但被指定為“指南”,以減輕一些VESA成員對VESA“認可”這些時間標準的擔憂。在低性能系統中,通常使用的準則是低分辨率或低刷新率。作為參考,該文件還包括計算機行業的許多行業標準定時(事實標準)。

2018-07-27 08:00:00 26

26 本文檔的主要內容詳細介紹的是FPGA視頻教程之FPGA設計中時序邏輯設計要點的詳細資料說明免費下載。

2019-03-27 10:56:04 20

20 FPGA采用了邏輯單元陣列LCA(Logic Cell Array)這樣一個概念,內部包括可配置邏輯模塊CLB(Configurable Logic Block)、輸出輸入模塊IOB(Input Output Block)和內部連線(Interconnect)三個部分。

2019-06-27 17:52:56 27053

27053 VGA(視頻圖形陣列)作為一種標準的顯示接口得到廣泛的應用。依據VGA顯示原理,介紹了利用FPGA實現對VGA圖形控制器的Verilog設計方法。詳細描述了各硬件模塊的工作原理及實現途徑,并給出了軟件設計思路。

2019-06-29 10:05:30 5776

5776

本文在介紹了CCO工作原理、分析了CCD輸出信號中混有的芥種噪聲的基礎上,提出幾種產生CCD驅動時序方法,重點介紹了選用FGPA(現場可編程邏輯門陣列)來作為時序發生器的優點,并講解了采用原理圖

2019-12-06 15:36:00 25

25 硬盤是電腦重要的儲存媒介,是電腦必不可少的組成部分,但很多人并不知道硬盤的工作原理,也不知道硬盤由哪些部件組成的。為了讓大家學通弄懂硬盤的工作原理,下面就給大家詳細介紹一下硬盤的工作原理和內部構造。

2021-01-01 17:17:00 34307

34307

在高速系統中FPGA時序約束不止包括內部時鐘約束,還應包括完整的IO時序約束利序例外約束才能實現PCB板級的時序收斂。因此,FPGA時序約束中IO口時序約束也是重點。只有約東正確才能在高速情況下保證FPGA和外部器件通信正確

2021-01-13 17:13:00 11

11 介紹了XGA標準,設計了一種基于FPGA的XGA標準圖像實時控制器,它將PAL制式的電視信號轉換成XGA格式的信號。重點討論了圖像數據的結構轉換過程及控制器的內部結構。

2021-02-05 15:54:00 10

10 時鐘(vga_clk),作為圖像數據生成模塊(vga_pic)和 VGA 時序控制模塊(vga_ctrl)的工作時鐘;(3) 圖像數據生成模塊以 VGA 時序控制模塊傳入的像素點坐標(pix_x,pix_y)為約束條件,生成待顯示彩條圖像的色彩信息(pix_data);(4) 圖像數據生成模塊生成的彩條

2021-12-17 18:44:18 8

8 上一篇《FPGA時序約束分享01_約束四大步驟》一文中,介紹了時序約束的四大步驟。

2022-03-18 10:29:28 2167

2167

時序分析時FPGA設計中永恒的話題,也是FPGA開發人員設計進階的必由之路。慢慢來,先介紹時序分析中的一些基本概念。

2022-03-18 11:07:13 3924

3924 時序約束是我們對FPGA設計的要求和期望,例如,我們希望FPGA設計可以工作在多快的時鐘頻率下等等。因此,在時序分析工具開始對我們的FPGA設計進行時序分析前,我們必須為其提供相關的時序約束信息。在

2022-12-28 15:18:38 5211

5211 GPU和FPGA都是現代計算機技術中的高性能計算設備,具有不同的特點和應用場景。本文將詳細介紹GPU和FPGA的工作原理及其區別。

2023-08-06 16:50:49 3372

3372 VESA 視頻標準同步信號產生器,是從事FPGA圖像領域工程師經常使用到的模塊。

2024-02-29 09:56:33 5850

5850

FPGA芯片的工作原理主要基于其內部的可配置邏輯單元和連線資源。包括以下工作原理: 首先,FPGA內部包含可配置邏輯模塊(CLB)、輸出輸入模塊(IOB)和內部連線(Interconnect)三個

2024-03-14 17:17:51 3091

3091 建立時間和保持時間是FPGA時序約束中兩個最基本的概念,同樣在芯片電路時序分析中也存在。

2024-08-06 11:40:18 2370

2370

電子發燒友網站提供《VESA提議的顯示端口(DP)標準.pdf》資料免費下載

2024-10-22 10:35:47 4

4

電子發燒友App

電子發燒友App

評論