加法器工作原理

加法器是產生數的和的裝置。加數和被加數為輸入,和數與進位為輸出的裝置為半加器。若加數、被加數與低位的進位數為輸入,而和數與進位為輸出則為全加器。常用作計算機算術邏輯部件,執行邏輯操作、移位與指令調用。在電子學中,加法器是一種數位電路,其可進行數字的加法計算。三碼,主要的加法器是以二進制作運算。由于負數可用二的補數來表示,所以加減器也就不那么必要。

設一個n位的加法器的第i位輸入為ai、bi、ci,輸出si和ci+1,其中ci是低位來的進位,ci+1(i=n-1,n-2,…,1,0)是向高位的進位,c0是整個加法器的進位輸入,而cn是整個加法器的進位輸出。則和

si=aiii+ibii+iici+aibici ,(1)進位ci+1=aibi+aici+bici ,(2)

令 gi=aibi, (3)

pi=ai+bi, (4)

則 ci+1= gi+pici, (5)

只要aibi=1,就會產生向i+1位的進位,稱g為進位產生函數;同樣,只要ai+bi=1,就會把ci傳遞到i+1位,所以稱p為進位傳遞函數。把式(5)展開,得到:ci+1= gi+ pigi-1+pipi-1gi-2+…+ pipi-1…p1g0+ pipi-1…p0c0(6) 。

隨著位數的增加式(6)會加長,但總保持三個邏輯級的深度,因此形成進位的延遲是與位數無關的常數。一旦進位(c1~cn-1)算出以后,和也就可由式(1)得出。

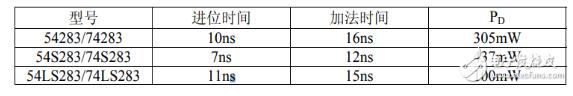

使用上述公式來并行產生所有進位的加法器就是超前進位加法器。產生gi和pi需要一級門延遲,ci 需要兩級,si需要兩級,總共需要五級門延遲。與串聯加法器(一般要2n級門延遲)相比,(特別是n比較大的時候)超前進位加法器的延遲時間大大縮短了。

加法器邏輯電路圖

計算機內部兩個二進制之間的加、減、乘、除算術運算都將轉化成若干步的加法運算進行。因此,在數字系統中,尤其在計算機的數字系統中,二進制加法器是其基本部件。

實現1位二進制數之間加法運算的電路稱為1位加法器。根據加數的不同,1位加法器又分為半加器和全加器兩種電路類型。

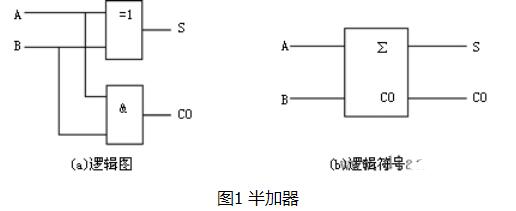

如果不考慮來自低位的進位而是只將兩個1位二進制數相加,即只有加數和被加數相加,這種加法運算稱為半加運算。實現半加運算的電路叫做半加器。

按照二進制加法運算的規則,列出半加器的邏輯真值表如表1所示。其中A、B是加數和被加數,S是相加的和(本位和)輸出,CO是向相鄰高位的進位輸出。

?

根據真值表寫出邏輯函數式并化簡:

?

畫出半加器的邏輯圖如圖1(a)所示。圖5-4-1(b)所示為半加器的邏輯圖形符號。

?

責任編輯:YYX

電子發燒友App

電子發燒友App

評論