信號完整性(Signal Integrity, SI)問題:隨著DDR內存頻率的提高,信號完整性問題....

eSchema電路設計工具作為一款面向專業IC設計者的綜合解決方案,通過集成原理圖設計、電氣規則檢查....

UniVista EDMPro是一款融合電子系統研制流程、技術與管理實踐的差異化一站式電子設計數據管....

總所周知,一般我們在對通信芯片互連的時候,要求兩者的IO接口電平標準是一樣的,而在學習FPGA與DD....

DDR是硬件設計的重要一環,作為一名硬件工程師除了對DDR基礎和原理要有了解外,最重要的也就是對DD....

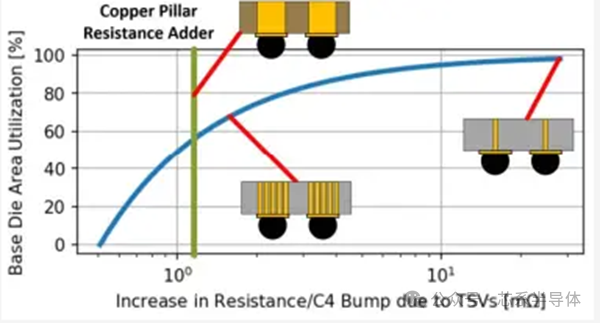

Wisim DC是一款高效、高性能的平臺級電源完整性EDA物理驗證仿真工具。可快速診斷IC封裝和系統....

Wisim SI是一款高效、精準的頻域信號完整性物理驗證EDA仿真工具。能夠高效準確地為設計人員提取....

在電子設備的散熱設計中,熱阻(Thermal Resistance)是一個至關重要的物理量,它定量描....

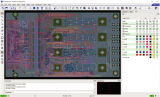

在當今快速發展的電子行業中,高效、精確的PCB(印刷電路板)設計工具是確保產品競爭力的關鍵。為滿足市....

? Cadence Allegro Package Designer Plus提供了一個完整的原理圖....

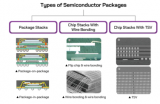

? PoP封裝結構 將要創建的元件參數如下: 1、共有3顆die,上面封裝基板正面放置2顆, Wir....

? PiP封裝結構 將要創建的元件參數如下: 1、共有2顆die,上方的封裝基板正面放置1顆,Wir....

高密度DDR(Double Data Rate)芯片是一種先進的動態隨機存取存儲器(DRAM)芯片,....

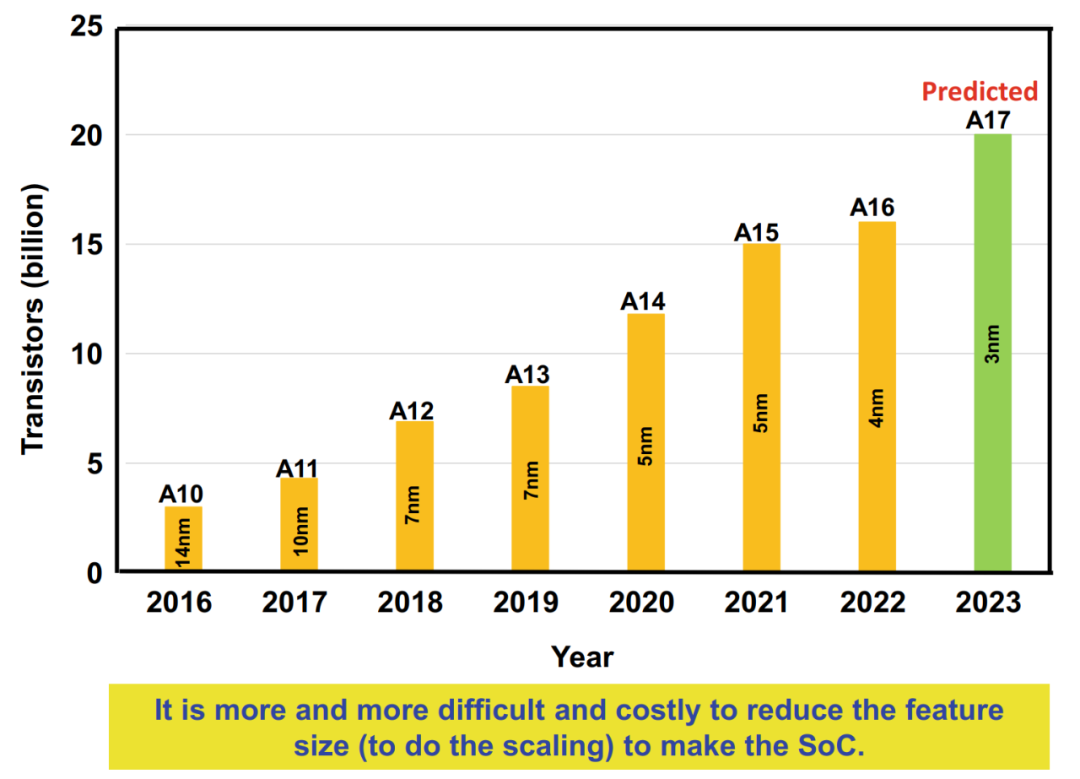

隨著摩爾定律的放緩,半導體行業越來越多地采用芯片設計和異構集成封裝來繼續推動性能的提高。這種方法是將....

DDR作為一種內存技術正朝著更高性能、更低功耗的方向發展。應用前景廣闊,將對半導體、計算機、汽車、新....

微電子鍵合線有多種純材料和合金材料。除了圓線外,扁帶材料還可用于射頻和微波電路等特殊應用中。圓線是迄....

隨著工藝節點的進步,英特爾也在不斷推進下一代封裝技術的發展。對高性能硅需求與工藝節點開發相結合,創造....

在現代芯片封裝技術中,"bump" 和 “micro bump” 是用于不同封裝類型的關鍵組件,尤其....

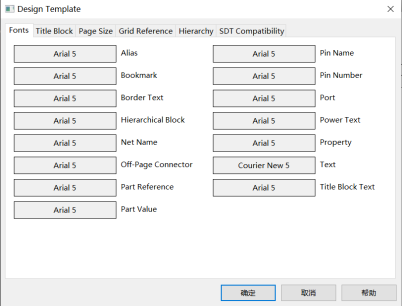

OrCAD Capture是一款具有簡單易用、功能特點豐富的電路原理圖輸入工具。由于它簡單直觀的使用....

步驟一:打開一個 PCB 文件,如下圖 1 所示。

OrCAD PSpice A/D和高級分析技術(A/A)結合了業界先進的模擬、模數混合信號以及分析工....

以DDR開頭的內存適用于計算機、服務器和其他高性能計算設備等領域,目前應用廣泛的是DDR3和DDR4....

OrCAD Capture是一款具有簡單易用、功能特點豐富的電路原理圖輸入工具。

DSN是當前已經打開原理圖文件; 02.DSN是需要對比的文件; Design Differene對....

因為位號重排是按照位置來的,所以應在所有元器件位號絲印全部排列好后再進行重排,推薦在出光繪之前進行重....

原理圖Part參數是指在設計電路時,對于每個元件所需填寫的相關信息,如元件名稱、型號、封裝等。這些參....

在現代電子系統的核心組件中,內存的性能與穩定性至關重要。高密度DDR4芯片作為當前內存技術的杰出代表....

摩爾定律在設計、制造、封裝3個維度上推動著集成電路行業發展。

RDL 技術是先進封裝異質集成的基礎,廣泛應用扇出封裝、扇出基板上芯片、扇出層疊封裝、硅光子學和 2....

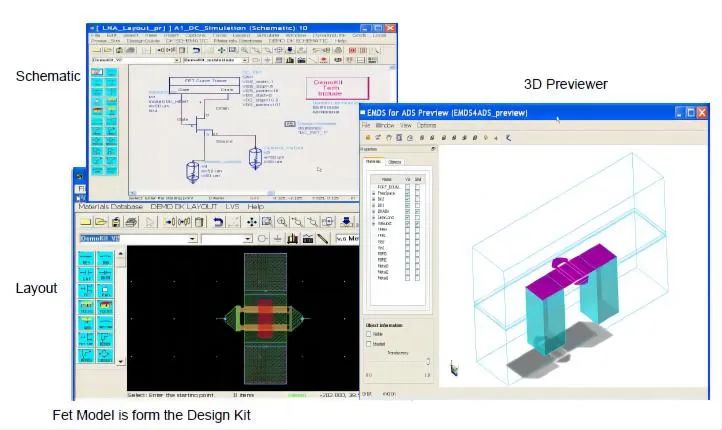

ADS:由Keysight Technologies(前身為Agilent Technologies....