在遵循管腳特定的規(guī)則和約束的同時,可以在 PCB 上的多個 FPGA 之間自動優(yōu)化信號管腳分配。減少布線層數(shù),最大限度地減少 PCB 上的交叉數(shù)量并縮短總體走線長度,以及減少信號完整性問題,從而提高完成率并縮短 FPGA 的布線時間。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

FPGA

+關(guān)注

關(guān)注

1660文章

22412瀏覽量

636282 -

pcb

+關(guān)注

關(guān)注

4404文章

23878瀏覽量

424243

發(fā)布評論請先 登錄

相關(guān)推薦

熱點推薦

人工智能數(shù)據(jù)中心的光纖布線策略

隨著人工智能(AI)技術(shù)的飛速發(fā)展,數(shù)據(jù)中心的光纖布線策略正面臨前所未有的挑戰(zhàn)和機遇。AI的高帶寬需求、低延遲要求以及大規(guī)模并行計算的特點,對數(shù)據(jù)中心的光纖布線提出了更高的要求。本文將從多個方面探討

高頻PCB布線“避坑指南”:4大核心技巧讓信號完整性提升90%

技巧 一、核心布線原則 多層板設(shè)計 高頻電路集成度高,采用至少四層板(頂層、底層、電源層、地層),利用中間層設(shè)置屏蔽和就近接地,降低寄生電感,縮短信號傳輸路徑,減少交叉干擾。例如,四層板比雙面板噪聲低20dB。 電源層與地平面相鄰,利用平面電容

Altera發(fā)布 Quartus? Prime 專業(yè)版和 FPGA AI 套件 25.3 版:編譯更快,智能更強

投產(chǎn)以來編譯時間縮短多達 27%,同時顯著提升了 AI 工具的易用性; 得益于增強型編譯器和架構(gòu)優(yōu)化,設(shè)計人員平均可節(jié)省

如何縮短電能質(zhì)量在線監(jiān)測裝置的抗干擾能力驗證時間?

縮短電能質(zhì)量在線監(jiān)測裝置的抗干擾能力驗證時間,核心是 “ 聚焦關(guān)鍵干擾、優(yōu)化測試流程、復(fù)用技術(shù)工具 ”,在保障核心驗證指標(精度穩(wěn)定性、事件捕捉完整性)不打折的前提下,砍掉冗余步驟、提升并行效率

京微齊力新版福晞軟件工具全面優(yōu)化FPGA設(shè)計環(huán)境

FPGA 設(shè)計開發(fā)過程中,軟件是工程師必不可少的工具,好的軟件開發(fā)環(huán)境可以簡化設(shè)計者的設(shè)計流程,縮短開發(fā)時間,提升整體設(shè)計效率。

PathFinder在FPGA中的角色與缺陷

自 1990 年代末以來,PathFinder 一直是 FPGA 布線(routing)階段的主力算法,為設(shè)計工具提供“能連通又不重疊”的路徑規(guī)劃方案。

低壓布線與傳統(tǒng)布線:有什么區(qū)別?

低壓布線與傳統(tǒng)布線在電壓范圍、應(yīng)用場景、設(shè)計要求、安全規(guī)范及材料選擇等方面存在顯著差異。以下是具體對比分析: 1. 電壓范圍與定義 低壓布線: 電壓等級:通常指交流電壓在1000V以下或直流電

亞馬遜:調(diào)用訂單退款A(yù)PI自動化處理售后請求,縮短用戶等待時間

? 在電商運營中,售后處理效率直接影響用戶體驗和平臺聲譽。亞馬遜作為全球領(lǐng)先的電商平臺,其訂單退款A(yù)PI為賣家提供了強大的自動化工具,幫助高效處理退款請求,顯著縮短用戶等待時間。本文將逐步介紹

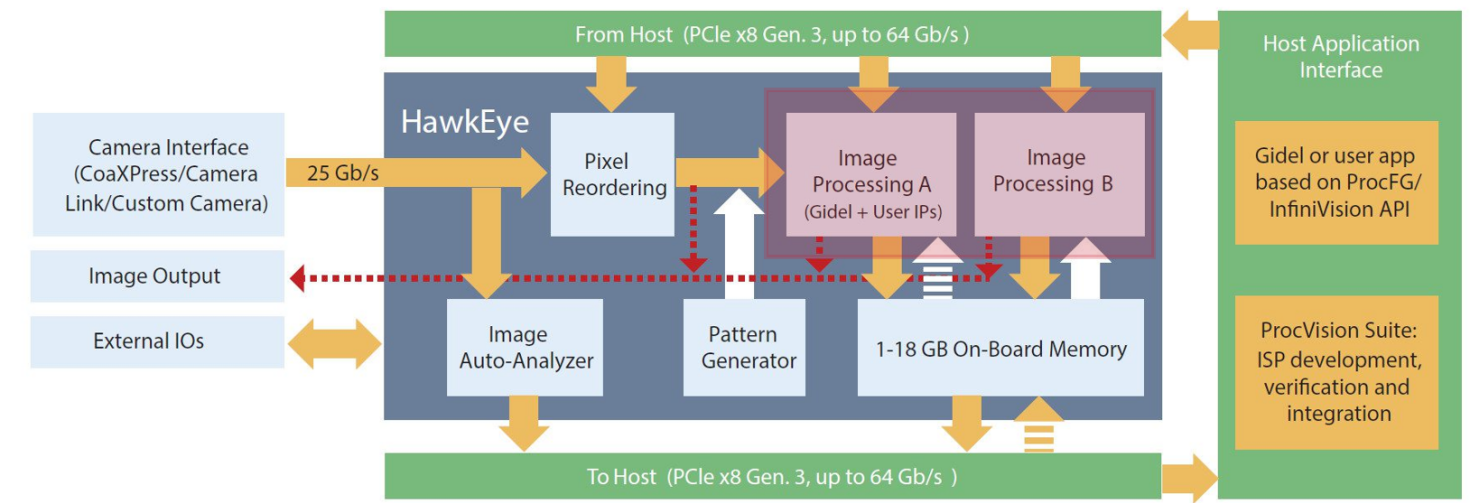

FPGA 加持,友思特圖像采集卡高速預(yù)處理助力視覺系統(tǒng)運行提速增效

圖像預(yù)處理是圖像處理關(guān)鍵環(huán)節(jié),可優(yōu)化數(shù)據(jù)傳輸、減輕主機負擔,其算法可在FPGA等硬件上執(zhí)行。友思特FPGA圖像采集卡憑借FPGA特性,能縮短處理時間

從發(fā)明到 AI 加速:慶祝 FPGA 創(chuàng)新 40 周年

設(shè)計芯片時,如果規(guī)格或需求在中途、甚至在制造完成后發(fā)生變化,他們可以重新定義芯片功能以執(zhí)行不同的任務(wù)。這種靈活性令新芯片設(shè)計的開發(fā)速度更快,從而縮短了新產(chǎn)品的上市時間,并提供了 ASIC 的替代方案。 ? FPGA 對市場的影響

發(fā)表于 06-05 17:32

?1318次閱讀

高層數(shù)層疊結(jié)構(gòu)PCB的布線策略

高層數(shù) PCB 的布線策略豐富多樣,具體取決于 PCB 的功能。這類電路板可能涉及多種不同類型的信號,從低速數(shù)字接口到具有不同信號完整性要求的多個高速數(shù)字接口。從布線規(guī)劃和為各接口分配信號層的角度來看,這無疑是一項極具挑戰(zhàn)性的任

【Simcenter FLOEFD】利用完全嵌入CAD的CFD軟件,幫助設(shè)計師盡早評估流體流動和傳熱,從而縮短開發(fā)時間

解決方案優(yōu)勢利用完全嵌入CAD的CFD軟件,幫助設(shè)計師在NX軟件、SolidEdge軟件、CATIA和Creo中盡早評估流體流動和傳熱,從而縮短開發(fā)時間。前置CFD仿真以縮短開發(fā)時間利

如何縮短多個FPGA的布線時間

如何縮短多個FPGA的布線時間

評論