Testbench

testbench是一種驗(yàn)證的手段。首先,任何設(shè)計(jì)都是會(huì)有輸入輸出的。但是在軟環(huán)境中沒(méi)有激勵(lì)輸入,也不會(huì)對(duì)你設(shè)計(jì)的輸出正確性進(jìn)行評(píng)估。那么此時(shí)便有一種,模擬實(shí)際環(huán)境的輸入激勵(lì)和輸出校驗(yàn)的一種“虛擬平臺(tái)”的產(chǎn)生。在這個(gè)平臺(tái)上你可以對(duì)你的設(shè)計(jì)從軟件層面上進(jìn)行分析和校驗(yàn),這個(gè)就是testbench的含義。

簡(jiǎn)單的Testbench設(shè)計(jì)

//timescale 仿真時(shí)間單位/時(shí)間精度(時(shí)間精度不能比時(shí)間單位還要大)

timescale 1ns/1ps

//定義一個(gè)無(wú)輸入無(wú)輸出的Moudle

module Led_clg_tst();

//被測(cè)設(shè)計(jì)的輸入信號(hào),對(duì)應(yīng)測(cè)試腳本的輸出信號(hào)(注意要定義成reg)

reg clk;

reg rst_n;

//被測(cè)設(shè)計(jì)的輸出信號(hào),對(duì)應(yīng)測(cè)試腳本的輸入信號(hào)(注意要定義成wire)

wire led;

//例化待測(cè)模塊

Led led_test

(

.clk(clk),

.rst_n(rst_n),

.led(led)

);

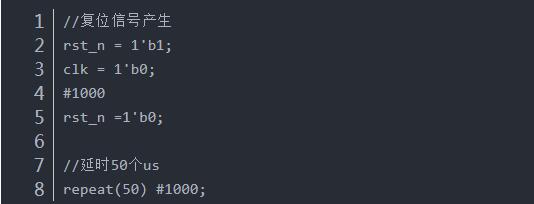

//使用Initail生成rst_n激勵(lì)

initial

begin

//監(jiān)控Led信號(hào)變化

monitor(monitor(time,”led value= %b\n”,led);

end

//使用alwasys模擬產(chǎn)生25M的時(shí)鐘信號(hào)

always #20 clk = ~clk;

endmodule

-

設(shè)計(jì)

+關(guān)注

關(guān)注

4文章

826瀏覽量

71318

發(fā)布評(píng)論請(qǐng)先 登錄

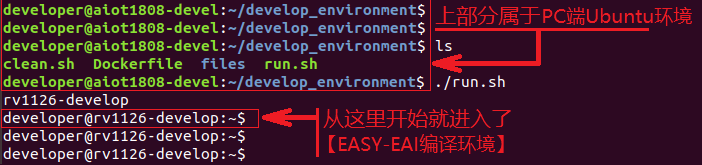

linux-arm開(kāi)發(fā)環(huán)境的簡(jiǎn)單配置

合科泰教你如何焊接簡(jiǎn)單LED閃爍電路

在verilog testbench中運(yùn)行測(cè)試用例時(shí),運(yùn)行到make run_test出錯(cuò)怎么解決?

求助,關(guān)于C代碼中的printf打印的疑問(wèn)求解

想調(diào)用VCS+VERDI測(cè)試蜂鳥(niǎo),按照網(wǎng)上的弄了,但是沒(méi)有波形,為什么?

求助,關(guān)于testbench仿真的問(wèn)題求解

看似簡(jiǎn)單的自動(dòng)泊車(chē)需要哪些技術(shù)支撐?

【精選直播】openDACS 2025 開(kāi)源EDA與芯片大賽 賽題二 賽題四 直播宣講會(huì)

語(yǔ)法糾錯(cuò)和testbench的自動(dòng)生成

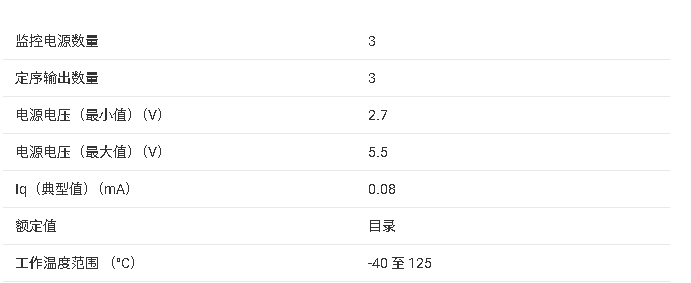

LM3881系列 3軌簡(jiǎn)單功率定序器技術(shù)手冊(cè)

萊姆傳感器接線指南:簡(jiǎn)單易懂的步驟

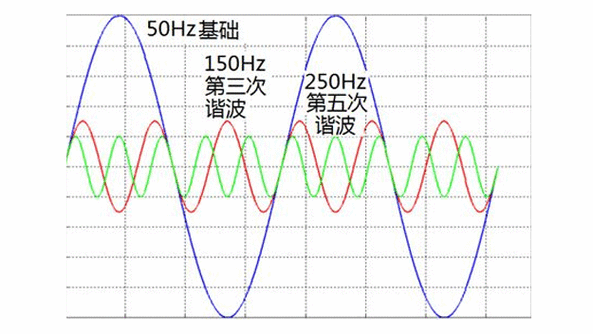

諧波怎么處理最簡(jiǎn)單的方法

在testbench中如何使用阻塞賦值和非阻塞賦值

簡(jiǎn)單的Testbench設(shè)計(jì)

簡(jiǎn)單的Testbench設(shè)計(jì)

評(píng)論