Xilinx System Generator?for DSP是Simulink的一個插件,使設(shè)計人員能夠為Xilinx FPGA開發(fā)高性能DSP系統(tǒng)。設(shè)計人員可以使用MATLAB,Simulink和Xilinx bit / cycle-true模型庫來設(shè)計和仿真系統(tǒng)。然后,該工具將自動生成映射到Xilinx預(yù)優(yōu)化算法的可綜合硬件描述語言(HDL)代碼。然后可以合成此HDL設(shè)計,以便在Xilinx FPGA和All Programmable SoC上實現(xiàn)。因此,設(shè)計人員可以定義系統(tǒng)級設(shè)計的抽象表示,并輕松地將此單個源代碼轉(zhuǎn)換為門級表示。此外,它還提供自動生成HDL測試平臺,可在實施時進(jìn)行設(shè)計驗證。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

dsp

+關(guān)注

關(guān)注

561文章

8244瀏覽量

366685 -

賽靈思

+關(guān)注

關(guān)注

33文章

1798瀏覽量

133442 -

HDL

+關(guān)注

關(guān)注

8文章

332瀏覽量

48978

發(fā)布評論請先 登錄

相關(guān)推薦

熱點推薦

Vector為科世達(dá)頒發(fā)ISO/SAE 21434汽車網(wǎng)絡(luò)安全CSMS流程證書

System)流程證書。該證書的取得,意味著科世達(dá)已建立起完整且高質(zhì)量的汽車網(wǎng)絡(luò)安全CSMS流程,并具備在產(chǎn)品研發(fā)、生產(chǎn)、售后運維等全生命周期中高效落實網(wǎng)絡(luò)安全管理的能力。科世達(dá)與Vector中國的相關(guān)代表共同參加了此次頒證儀

借助 AI 從流程可視化到流程優(yōu)化的 6 個步驟

借助 Minitab Solution Center與 Simul8,將日常流程損耗轉(zhuǎn)化為可量化的效能提升 生活各處都看到流程的影子,無論是逛雜貨店、排隊買咖啡,還是收拾行李準(zhǔn)備度假。你是否曾發(fā)現(xiàn)

IBM Storage Scale System 6000煥新升級

沒有數(shù)據(jù)的 AI 工廠就像沒有燃料的引擎,根本無法運轉(zhuǎn)。IBM Storage Scale System 6000 的全局命名空間和 Active File Management (AFM) 功能

DSP的基礎(chǔ)

高速數(shù)字信號處理技術(shù)是以DSP為核心,具有高速,實時的特點的一種信息處理技術(shù)。其本質(zhì)是信息的變換和提取。DSP(Digital Signal Processor),即數(shù)字信號處理器,是一種專用

發(fā)表于 11-20 06:35

【技術(shù)分享】正確編寫SysV Init腳本以實現(xiàn)Systemd兼容(上)

嵌入式的ubuntu系統(tǒng)如何寫好SysVInit腳本呢?與system服務(wù)又有什么差別呢?一起隨著文章來探究吧。問題背景許多傳統(tǒng)Linux服務(wù)仍使用SysVInit腳本(/etc/init.d

國產(chǎn)32位高性能Audio音頻數(shù)字信號處理器(DSP)芯片-DU561

音頻數(shù)字信號處理器(DSP)的工作原理主要通過數(shù)字化處理提升音頻質(zhì)量,其核心流程包括信號采集、處理和輸出三個關(guān)鍵環(huán)節(jié)。

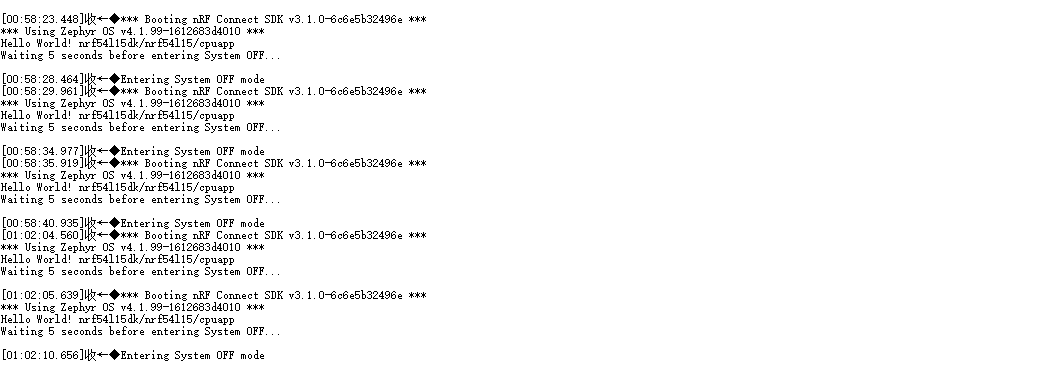

【NCS隨筆】如何進(jìn)入system_off深度睡眠模式以及配置GPIO中斷喚醒

【NCS隨筆】如何進(jìn)入system_off深度睡眠模式以及配置GPIO中斷喚醒 本文章主要是講解NCS下面使用nRF54L15如何進(jìn)入system_off模式,以及如何配置通過按鍵喚醒 一、如何進(jìn)

DSP芯片與800G光模塊的核心關(guān)系:Transmit Retimed DSP、LPO與LRO方案的探討

本文深入探討DSP芯片在800G光模塊中的核心作用,包括Transmit Retimed DSP架構(gòu)與新興LPO/LRO方案的對比分析。DSP在信號均衡、誤碼控制與長距離傳輸中不可或缺,而LPO/LRO以低功耗優(yōu)勢適用于短距互聯(lián)

音頻DSP設(shè)計與應(yīng)用

DSP(即數(shù)字信號處理器)對于音頻處理技術(shù)至關(guān)重要。

新唐DSP集成了Waves(Maxx音頻),DSP 算法的全球領(lǐng)導(dǎo)者。這包括專用的揚聲器校準(zhǔn)算法和心理聲學(xué)算法。此外,它還具有強(qiáng)大的音頻算法

發(fā)表于 09-05 07:45

深度剖析 RT-Thread 線程調(diào)度流程

RT-Thread調(diào)度第一個線程的主要流程分如下:rtthread_startup:RTT的啟動函數(shù),主要負(fù)責(zé)板級驅(qū)動,調(diào)度器,系統(tǒng)線程初始化,啟動調(diào)度的工作

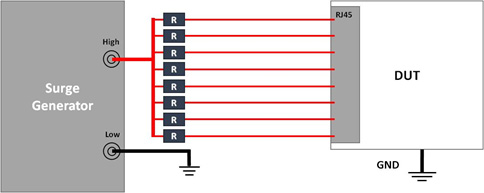

“System Level EOS Testing Method”可以翻譯為: “系統(tǒng)級電性過應(yīng)力測試方法”

“System Level EOS Testing Method”可以翻譯為:

“系統(tǒng)級電性過應(yīng)力測試方法”

智多晶FIFO_Generator IP介紹

FIFO_Generator是智多晶設(shè)計的一款通用型FIFO IP。當(dāng)前發(fā)布的FIFO_Generator IP是2.0版本,相比之前的1.1版本主要新增了非等比輸入輸出數(shù)據(jù)位寬支持和異步FIFO跨時鐘級數(shù)配置功能。

國產(chǎn)開發(fā)板—米爾全志T113-i如何實現(xiàn)ARM+RISC-V+DSP協(xié)同計算?

GPADC采集測試

采集流程如下: 1. 開啟DSP2. DSP核打印3. 開啟DSP后,把GPADC0引腳接入1.8V電源,此時用戶可以執(zhí)行A核應(yīng)用程序與

發(fā)表于 03-21 16:50

System Generator for DSP的設(shè)計流程

System Generator for DSP的設(shè)計流程

評論