了解Express Logic用于Zynq-7000 All Programmable SoC的NetX高性能TCP-IP堆棧。 主題包括:用于Zynq的Eclipse IDE概述,使用Iperf開源在SDK中設(shè)置和執(zhí)行NetX TCP-IP基準(zhǔn)演示..

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

賽靈思

+關(guān)注

關(guān)注

33文章

1798瀏覽量

133425 -

soc

+關(guān)注

關(guān)注

40文章

4576瀏覽量

229117 -

Zynq

+關(guān)注

關(guān)注

10文章

630瀏覽量

49447

發(fā)布評論請先 登錄

相關(guān)推薦

熱點推薦

CW32系列MCU在Eclipse GCC + JLink下的使用示例分享

CW32系列MCU在Eclipse GCC + JLink下的使用示例:

1、下載安裝Eclipse IDE for Embedded C/C++ Developers。

2、下載安裝

發(fā)表于 02-02 06:57

乾芯DSP開發(fā)環(huán)境之IDE安裝使用入門

工欲善其事,必先利其器。對于企業(yè)用戶而言,一款適配的集成開發(fā)環(huán)境(IDE)絕非簡單工具,更是提升團隊效率、保障代碼安全的核心支撐。下面就為大家梳理IDE安裝使用的核心步驟,新手也能快速掌握。一、搭建乾芯DSP開發(fā)環(huán)境QX-IDE

經(jīng)驗分享 | eclipse搭建先楫開發(fā)環(huán)境

最近有小伙伴留言,想在eclipse平臺下開發(fā)先楫的MCU,但是苦于沒有工程模板,自己折騰了半天又遇到一堆報錯,很費時間。基于此需求,筆者基于HPM6E00EVK一步一步搭建在eclipse下的開發(fā)環(huán)境,可以順利實現(xiàn)仿真和調(diào)試,并提供模版工程作為拋磚引玉,用戶可以自由發(fā)揮

蜂鳥E203 Eclipse工程無法調(diào)試怎么解決?

我使用githbird-e-sdk中指向的https://pan.baidu.com/s/1eUbBlVc

HBird-Eclipse_2018_09.rar ,按照書中的步驟創(chuàng)建項目,一步步操作

發(fā)表于 11-11 08:19

在windows上用Eclipse IDE調(diào)試蜂鳥E203,用的開發(fā)板是哪個型號的?

在windows上用Eclipse IDE調(diào)試蜂鳥E203,用的開發(fā)板是哪個型號的,有哪位大佬調(diào)試出來了,求告知

發(fā)表于 11-07 07:19

蜂鳥E203的NMSIS庫結(jié)合Nuclei Studio IDE的使用

Nuclei Studio IDE的應(yīng)用

Nuclei Studio IDE是芯來公司,基于MCU Eclipse IDE開發(fā)的一款針對處理器的開發(fā)工具。

接下來參考網(wǎng)上官網(wǎng)方法建立N

發(fā)表于 10-22 06:26

ZYNQ PS與PL數(shù)據(jù)交互方式

ZYNQ SoC 的 PS (Processing System) 和 PL (Programmable Logic) 之間的數(shù)據(jù)交互是系統(tǒng)設(shè)計的核心。

可以將 Infineon DAVE? IDE 用于 Autrix TC333 MCU 嗎?

我可以將 Infineon DAVE? IDE 用于 Autrix TC333 MCU 嗎?

發(fā)表于 08-15 08:29

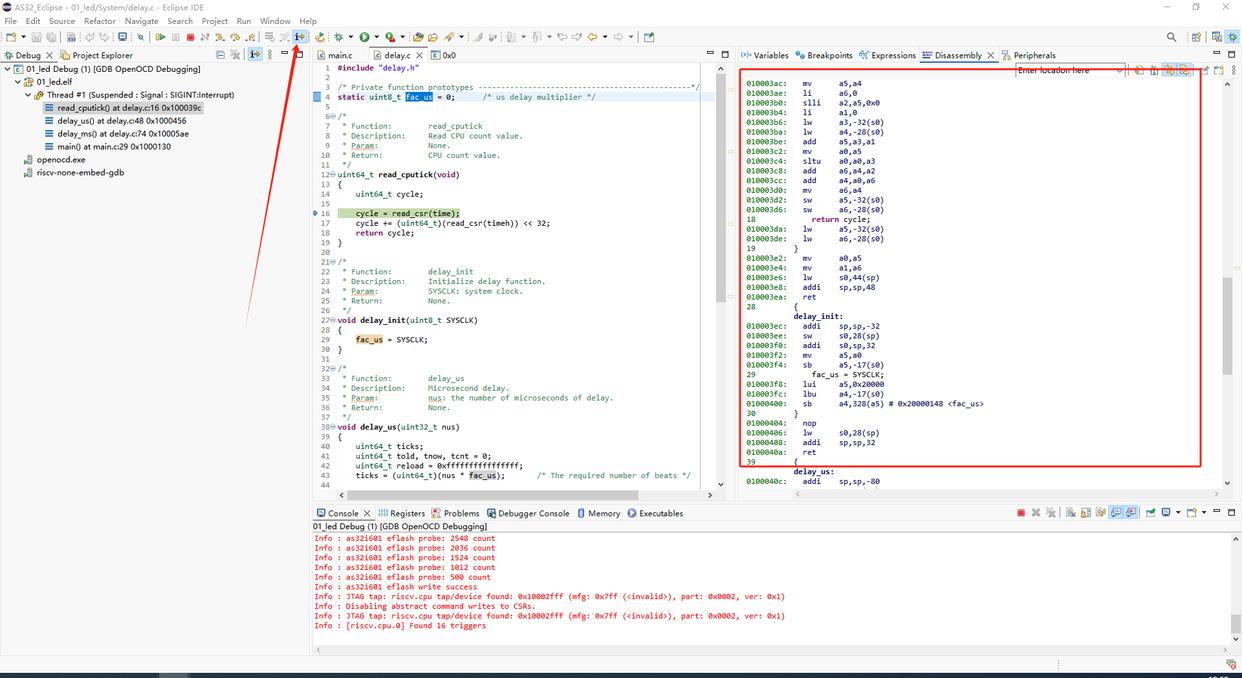

調(diào)試工具:Eclipse調(diào)試工具欄與窗口的深入分析

摘要 :在嵌入式系統(tǒng)開發(fā)領(lǐng)域,高效的調(diào)試工具鏈對于項目的成功實施具有決定性意義。本文聚焦于 Eclipse 調(diào)試工具欄與窗口的功能特性,深入剖析其在嵌入式開發(fā)調(diào)試過程中的關(guān)鍵作用。以廈門國科安芯

CH367連接zynq問題

通過四線SPI連接CH367和zynq時,CH367使用CH367StreamSPI函數(shù)設(shè)置為四線模式,然后設(shè)置SDI為MISO,SDX為MOSI,SCS和SCL為片選和時鐘

發(fā)表于 07-03 10:10

如何在Unified IDE中創(chuàng)建視覺庫HLS組件

組件開始,該組件可以導(dǎo)出為 XO 文件用于 Vitis 系統(tǒng)工程;這與“自上而下的流程”相反,后者從 Vitis 工程開始,然后將 HLS 組件導(dǎo)入該工程。我們將創(chuàng)建視覺庫示例“remap”,并在 Unified IDE 中執(zhí)行每一步,而不是運行 Makefile 腳本

使用AMD Vitis Unified IDE創(chuàng)建HLS組件

這篇文章在開發(fā)者分享|AMD Vitis HLS 系列 1 - AMD Vivado IP 流程(Vitis 傳統(tǒng) IDE) 的基礎(chǔ)上撰寫,但使用的是 AMD Vitis Unified IDE,而不是之前傳統(tǒng)版本的 Vitis HLS。

如何在Eclipse ThreadX RTOS中集成SystemView

SEGGER實時軟件分析工具SystemView已經(jīng)在ThreadX v6.4.2上進行了測試。SystemView從v3.60c版本支持Eclipse ThreadX(Azure RTOS),用戶

SEGGER SystemView支持Eclipse ThreadX

SEGGER的實時軟件分析工具SystemView v3.60c版本現(xiàn)已支持Eclipse ThreadX(Azure RTOS),用戶可以基于Systemview記錄ThreadX操作系統(tǒng)事件并執(zhí)行分析。

用于Zynq的Eclipse IDE概述

用于Zynq的Eclipse IDE概述

評論