在今天賽靈思開發者大會北京站上,賽靈思CEO發布了第一款7nm工藝的ACAP平臺第一款產品Versal,賽靈思產品技術營銷高級總監Kirk Saban詳細介紹了這款產品。

他說這是一款創新產品,考慮了開發者的需求

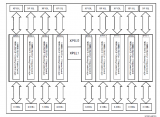

他詳細介紹了Versal各個模塊

行業首款ACAP——VERSAL

Versal ACAP技術之旅

靈活應變的硬件引擎

各種智能引擎

AI引擎

集成主機接口

可擴展的集成存儲器控制器

集成各種協議引擎

范圍最廣泛的收發器

片上網絡(NoC)實現軟件的可編程性

面向廣泛市場應用的Versal

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

賽靈思

+關注

關注

33文章

1798瀏覽量

133607 -

7nm

+關注

關注

0文章

267瀏覽量

36379

原文標題:詳細揭秘賽靈思第一款ACAP產品Versal

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

熱點推薦

賽靈思FPGA電源解決方案全解析

賽靈思FPGA電源解決方案全解析 在當今的電子設計領域,現場可編程門陣列(FPGA)憑借其出色的設計靈活性和較低的工程成本,在眾多應用和終端市場中占據了重要地位。然而,FPGA的電源設計和管理卻是一

易靈思Sapphire SoC中RISC-V平臺級中斷控制器深度解析

隨著 RISC -V處理器在 FPGA 領域的廣泛應用,易靈思 FPGA 的 Sapphire RISC-V 內核憑借軟硬核的靈活支持,為開發者提供多樣選擇。本文深入探討 Sapphire SoC 中 RISC - V 平臺級

“汽車智能化” 和 “家電高端化”

,對算力和穩定性要求極高。而車規芯片要通過 - 40℃~125℃的極端環境測試,7nm 工藝的低功耗、高可靠性剛好匹配需求。目前我國汽車芯片對外依賴度超 90%,高端計算芯片國產化率不足 20%,中芯

發表于 10-28 20:46

國產AI芯片真能扛住“算力內卷”?海思昇騰的這波操作藏了多少細節?

最近行業都在說“算力是AI的命門”,但國產芯片真的能接住這波需求嗎?

前陣子接觸到海思昇騰910B,實測下來有點超出預期——7nm工藝下算力直接拉到256 TFLOPS,比上一代提升了40%,但功耗

發表于 10-27 13:12

AMD 7nm Versal系列器件NoC的使用及注意事項

AMD 7nm Versal系列器件引入了可編程片上網絡(NoC, Network on Chip),這是一個硬化的、高帶寬、低延遲互連結構,旨在實現可編程邏輯(PL)、處理系統(PS)、AI引擎(AIE)、DDR控制器(DDRMC)、CPM(PCIe/CXL)等模塊之間

一文詳解Advanced IO wizard異步模式

7nm Versal系列相對于16nm Ultrascale plus系列,IO做了升級,U+系列的HPIO在Versal升級為XPIO。Versa

基于AMD Versal器件實現PCIe5 DMA功能

Versal是AMD 7nm的SoC高端器件,不僅擁有比16nm性能更強的邏輯性能,并且其PS系統中的CPM PCIe也較上一代MPSoC PS硬核PCIe單元強大得多。本節將基于AMD官方開發板展示如何快速部署PCIe5x8

賽靈思發布基于7nm工藝的ACAP平臺產品Versal

賽靈思發布基于7nm工藝的ACAP平臺產品Versal

評論