CMOS集成電路使用時的技術要求,CMOS IC requirements

關鍵字:CMOS集成電路使用時的技術要求

CMOS集成電路使用時的技術要求

1.CMOS集成電路輸入端的要求

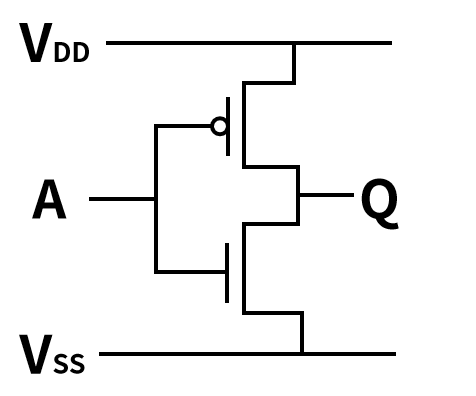

CMOS集成電路具有很高的輸入阻抗,其內部輸入端接有二極管保護電路.以防范外界干擾、沖擊和靜電擊穿。CMOS集成電路的輸入端懸空時輸入阻抗高,易受外界噪聲干擾,使電路產生誤動作。破壞正常的邏輯關系,而且也極易使柵極感應靜電造成擊穿損壞。所以,對于“與”門、“與非”門CMOS集成電路的多余端采取接高電平措施;對于“或”門、“或非”門CMOS集成電路的多余端采取接低電平措施。如果電路的工作速度要求不高,功耗也不需要特別考慮,則可采用多余的輸入端和使用端并用的措施加以解決。輸入端的電流不能超過1mA(極限值為10mA),必須在輸入端加適當的電阻進行限流保護(一般在12V的工作電壓時,輸入端加1.2kΩ的電阻進行限流保護)。輸入信號不可大于VDD小于VSS,否則輸入保護二極管會因正向偏置而引起大電流。在工作或測試時,必須先接通電源后再加信號,先撤除信號后再關電源。如果輸入信號的上升或下降時間過長。容易造成虛假觸發而導致器件失去正常功能,還會造成損耗。對4000B系列,上升或下降時間限于15us以內。否則,須使用史密特觸發電路對輸入信號整形。在CMOS集成電路的輸入端與機械接點連接或應用在其他特殊情況下,輸入端接線過長。使分布電容和分布電感較大,很容易形成LC振蕩,破壞CMOS中的保護二極管。

CMOS集成電路的工作電源電壓一般在3—18V之間.由于CMOS集成電路的工作電壓范圍寬,不使用穩壓的電源電路也可以工作。但當系統中有模擬應用的門電路時,最低工作電壓則不應低于4.5V。工作在不同電源電壓下的器件,其輸出阻抗、工作速度和功耗也會不同.在使用中應注意。CMOS器件輸出端不允許直接和VCC或VSS連接,否則將導致器件損壞。

2.防靜電要求

如果輸入電路中沒有一定的抗靜電措施,CMOS集成電路很容易造成電路的毀滅性破壞。CMOS集成電路應放在抗靜電的材料中儲存和運輸。工作人員不宜穿化纖衣服、硬塑料底的鞋,手或工具在接觸集成塊前最好先接一下地。對器件引線矯直、彎曲或人工焊接時.使用的設備必須接地良好。由于保護電路吸收的瞬變能量有限,太大的瞬變信號和過高的靜電電壓將使保護電路失去作用。在焊接CMOS管腳時,電烙鐵必須可靠接地,利用電烙鐵斷電后的余熱焊接,并先焊接其接地腳,以防電烙鐵漏電擊穿器件輸入端。總而言之,CMOS集成電路在包裝、儲存、運輸、焊接等環節中可能產生的靜電問題,仍須謹慎對待,采取各種措施預防,并且接地良好、可靠。

3。接口與驅動要求

CMOS集成電路與運放接口時。運放如果使用單電源。并且與CMOS使用的電源一樣,則可直接連接。如果運放采用雙電源。CMOS采用的是獨立的另一組電源,在電路中,則要采用鉗位保護電路,使CMOS輸入電壓處在10V與地之間。接口電阻既作為CMOS的限流電阻,又對二極管進行限流保護。邏輯器件的接口電路主要應注意電平匹配和輸出能力兩個問題,要和器件的電源電壓結合起來考慮。例如,CMOS集成電路和TTL等其他電路的連接.其電路相互之間的電源電壓和輸入、輸出電平及電流不相同,則其前級電路的輸出電流必須滿足后級電路對輸入電流的要求:前級電路輸出的邏輯電平必須滿足后級電路對輸入電平的要求,它們之間的連接是通過電平轉換或電流轉換電路完成的。CMOS集成電路既可以將同一個芯片幾個同類電路并接起來提高驅動能力。也可以選用驅動能力較強的緩沖放大器來提高驅動能力。 ◇山東郎筠

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

發布評論請先 登錄

相關推薦

熱點推薦

MC14600:低功耗CMOS報警IC的技術解析

MC14600:低功耗CMOS報警IC的技術解析 在電子設計領域,報警系統的設計一直是一個重要的課題。而Freescale Semiconductor的MC14600低功耗CMOS報警

單片機TTL和CMOS電平知識

和CMOS兩者的區別

(1)TTL電路是電流控制器件,穩定時損耗高,發熱量大,無法做集成度比較高的芯片。而CMOS電路是電壓控制器件,功耗

發表于 12-03 08:10

2.4 GHz CMOS WLAN 射頻前端集成電路,帶 PA、帶旁路的 LNA 以及用于 WLAN 和藍牙?信號功能的 SP3T 開關 skyworksinc

電子發燒友網為你提供()2.4 GHz CMOS WLAN 射頻前端集成電路,帶 PA、帶旁路的 LNA 以及用于 WLAN 和藍牙?信號功能的 SP3T 開關相關產品參數、數據手冊,更有2.4

發表于 10-29 18:32

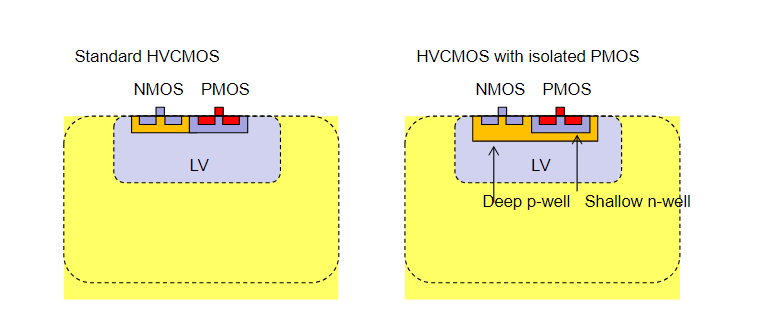

CMOS集成電路中閂鎖效應的產生與防護

閂鎖效應(Latch-up)是CMOS集成電路中一種危險的寄生效應,可能導致芯片瞬間失效甚至永久燒毀。它的本質是由芯片內部的寄生PNP和NPN雙極型晶體管(BJT)相互作用,形成類似可控硅(SCR)的結構,在特定條件下觸發低阻抗通路,使電源(VDD)和地(GND)之間短路

VirtualLab:CMOS傳感器仿真

CMOS傳感器由于其從每個像素單獨提取信息的能力以及其低成本和低功耗,已成為圖像傳感器的主導技術。后者主要歸因于近年來CMOS像素尺寸的快速縮小。然而,小的特征尺寸也使器件功能逼近極限,因為具有非常

發表于 06-16 08:49

一款雙通道采用SOIC-8封裝的25MBd CMOS光耦合器-ICPL-074L

ICPL-074L(雙通道)是采用SOIC-8封裝的25兆位CMOS光耦合器。這些光耦合器采用較新的CMOS集成電路技術,不僅性能卓越,而且功耗極低。ICPL-074L的核心組件包括高

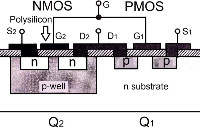

CMOS工藝流程簡介

互補金屬氧化物半導體(CMOS)技術是現代集成電路設計的核心,它利用了N型和P型MOSFET(金屬氧化物半導體場效應晶體管)的互補特性來實現低功耗的電子設備。CMOS工藝的發展不僅推動

電路設計異常要考慮:電流倒灌、熱插拔、過流保護、過壓保護、上電電流

一、異常情況的思考

異常情況的思考

1、電流倒灌集成電路的模型典型如下:

1、D1在大多數CMOS集成電路中產生了抗靜電功能。同時輔助產生了輸入端限幅作用。但在ABT、LVT、LVC和AHC

發表于 05-20 14:27

中國集成電路大全 接口集成電路

資料介紹本文系《中國集成電路大全》的接口集成電路分冊,是國內第一次比較系統地介紹國產接口集成電路的系列、品種、特性和應用方而知識的書籍。全書共有總表、正文和附錄三部分內容。總表部分列有國產接口

發表于 04-21 16:33

CMOS集成電路使用時的技術要求,CMOS IC requirements

CMOS集成電路使用時的技術要求,CMOS IC requirements

評論