一前言

高頻時(shí)鐘信號的快速跳變、不完整的回流路徑、邊緣走線的“天線效應(yīng)”……這些設(shè)計(jì)細(xì)節(jié)稍有不慎,就會(huì)讓整機(jī)變成一臺(tái)“微型電臺(tái)”,向空間肆意發(fā)射電磁波。今天,我們將揭開時(shí)鐘走線EMC整改的底層邏輯,從輻射機(jī)理到實(shí)戰(zhàn)技巧,手把手教你馴服這些“隱形的干擾源”!

二案例分享

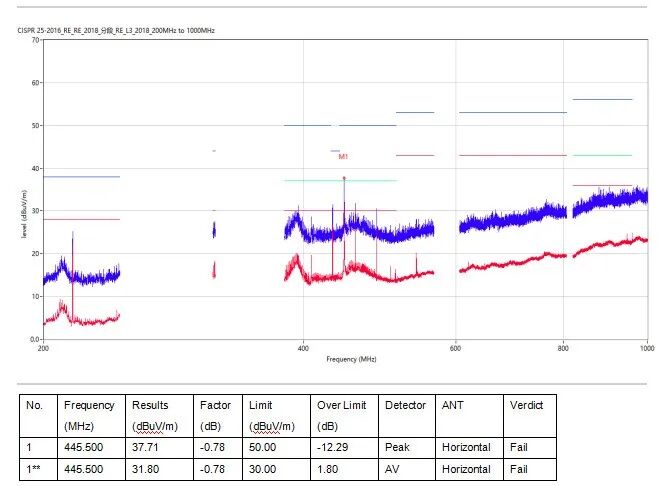

某款行車記錄儀的輻射測試結(jié)果顯示,445.5MHz頻點(diǎn)存在超標(biāo)現(xiàn)象。經(jīng)分析,該問題源于視頻解碼芯片TP9950向主控傳輸?shù)腜CLK時(shí)鐘信號。在整改過程中,嘗試采用以下兩種措施:

1.將PCLK傳輸線上的60Ω磁珠替換為120Ω磁珠;

2.在PCLK傳輸線靠近TP9950芯片端添加濾波電容。

雖然上述措施能夠通過輻射測試,但后續(xù)發(fā)現(xiàn)會(huì)引發(fā)行車記錄儀出現(xiàn)花屏現(xiàn)象。當(dāng)減小這些器件的參數(shù)值時(shí),則出現(xiàn)無法通過輻射測試或顯示畫面異常的兩種情況。

經(jīng)進(jìn)一步檢查PCB布局,發(fā)現(xiàn)TP9950芯片的時(shí)鐘走線存在以下設(shè)計(jì)缺陷:

走線位于板邊區(qū)域;

未進(jìn)行包地處理。

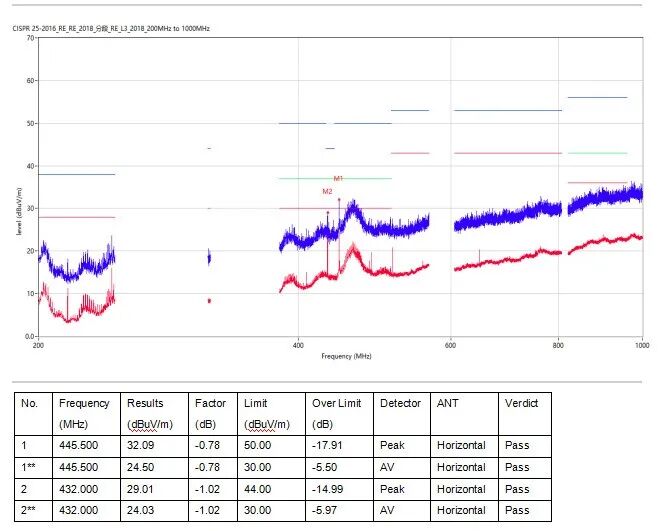

針對此問題,我們建議客戶對PCLK時(shí)鐘走線進(jìn)行優(yōu)化改進(jìn)。實(shí)施整改后,后續(xù)測試結(jié)果顯示輻射問題已得到有效解決,測試結(jié)果符合要求。

【改板建議】:

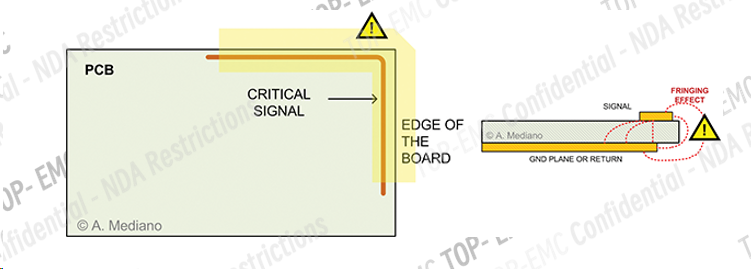

(1)時(shí)鐘信號不能畫在板子邊緣,下方或相鄰的參考地平面可能被切斷或不足,迫使信號回流路徑繞行較遠(yuǎn)距離,就會(huì)如下圖一樣產(chǎn)生一些空間串?dāng)_。

時(shí)鐘信號距離板邊的距離最好大于5mm,在時(shí)鐘信號到板邊之間最好多一個(gè)地走線進(jìn)行隔離,如下圖所示。

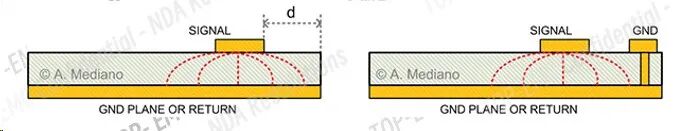

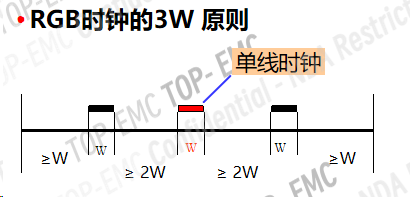

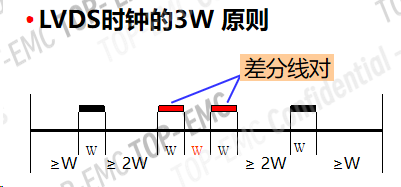

(2)畫PCB板的時(shí)候我們一般會(huì)有3W原則,也就是在PCB設(shè)計(jì)中,為了減少線間串?dāng)_,應(yīng)保證線間距足夠大,當(dāng)線中心間距不少于3倍線寬時(shí)。

例如,若線寬為5mil(0.127mm),則相鄰信號線的最小間距應(yīng)為15mil(0.381mm),耦合到臨近走線的邊緣場很少,大部分的電磁場被包圍在走線和回流平面之間,可以降低70%信號線間電場和磁場的耦合效應(yīng)。如果能滿足10倍線寬則能減少98%信號間的串?dāng)_。單線時(shí)鐘和差分時(shí)鐘會(huì)有一點(diǎn)點(diǎn)區(qū)別,可以參考下圖所示。

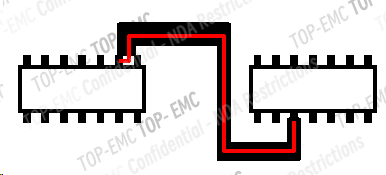

(3)在時(shí)鐘線的下層,沿著信號線布一條地線,地線盡量寬一些。這樣形成的回路面積等于線路板的層間厚度乘以信號線的長度,如下圖所示。

三總結(jié)

一般情況下,時(shí)鐘信號都是比較敏感的,像濾除高頻噪聲的電容或者共模電感,都會(huì)干擾信號的完整性,所以當(dāng)我們遇到時(shí)鐘噪聲超標(biāo)時(shí),我們可以先看看時(shí)鐘走線是否有問題,比如走線過長;走線太過靠近主板邊緣;走線是否進(jìn)行包地處理。因?yàn)闀r(shí)鐘信號回流需要低阻抗路徑,所以對時(shí)鐘走線的整改也是輻射超標(biāo)問題的重要解決手段。

-

高頻

+關(guān)注

關(guān)注

11文章

497瀏覽量

55158 -

電磁波

+關(guān)注

關(guān)注

21文章

1505瀏覽量

55862 -

時(shí)鐘信號

+關(guān)注

關(guān)注

4文章

509瀏覽量

30066

發(fā)布評論請先 登錄

vivado約束案例:跨時(shí)鐘域路徑分析報(bào)告

剛?cè)彳洐C(jī)器人設(shè)計(jì)與仿真分析實(shí)例解析

Small RTOS51 應(yīng)用實(shí)例和分析

時(shí)序邏輯電路分析實(shí)例

MATLAB數(shù)學(xué)建模算法及實(shí)例分析

用實(shí)例深入闡述雙端口分析和回歸比分析

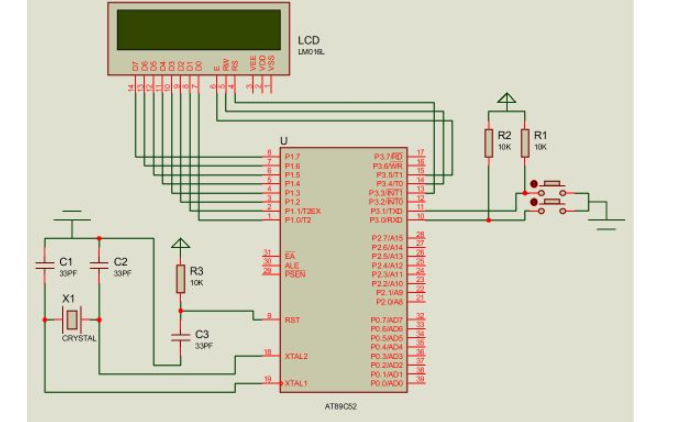

使用C51單片機(jī)和Proteus仿真設(shè)計(jì)模擬時(shí)鐘的應(yīng)用實(shí)例資料說明

時(shí)鐘子系統(tǒng)中clock驅(qū)動(dòng)實(shí)例

時(shí)鐘問題的實(shí)例分析

時(shí)鐘問題的實(shí)例分析

評論