文章來源:Jeff的芯片世界

原文作者:Jeff的芯片世界

側墻工藝是半導體制造中形成LDD結構的關鍵,能有效抑制熱載流子效應。本文從干法刻蝕原理出發,深度解析側墻材料從單層SiO?到ONO三明治結構及雙重側墻的迭代演進,揭示先進制程下保障器件可靠性與性能的核心邏輯。

側墻工藝是半導體制造中用于形成輕摻雜漏(LDD)結構的關鍵技術。在器件尺寸不斷縮小的過程中,漏極電壓升高會導致耗盡區寬度增加,載流子在強電場作用下形成高能熱載流子,進而引發熱載流子注入效應,這是導致器件和芯片失效的常見誘因。為降低漏極與襯底PN結附近的峰值電場強度,研發人員引入了LDD結構,即在漏極與溝道之間形成一層很薄的輕摻雜區。側墻工藝的作用正是在LDD離子注入后,制造出掩蔽層以防止后續重摻雜的源漏離子注入影響輕摻雜區域。從器件剖面圖可見,LDD結構位于側墻正下方,側墻能夠有效掩蔽LDD結構,且該工藝不需要掩模版,成本較低、流程簡單。

側墻的形成基于各向異性的干法刻蝕回刻技術。首先淀積厚度為S1的介質層,多晶硅柵的厚度為S2,其側面介質層總厚度為S1+S2。干法刻蝕方向垂直向下,刻蝕停止于硅表面,刻蝕厚度即為S1,因此多晶硅柵側面剩余的介質層厚度為S2,最終形成側墻結構。側墻的橫向側面寬度略小于S1,該寬度決定了LDD結構的橫向尺寸,由淀積的介質層厚度決定。

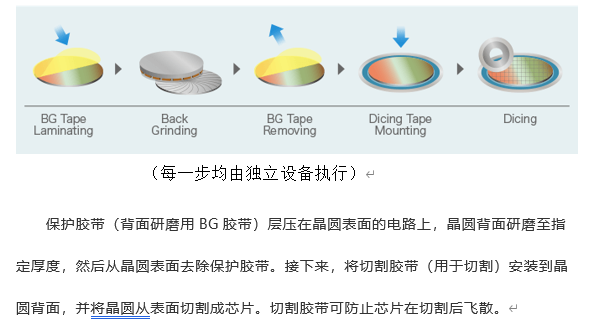

側墻刻蝕工藝流程

側墻刻蝕的典型流程如下:先沉積介質層,隨后進行各向異性的干法刻蝕回刻,刻蝕方向垂直向下,停止于硅表面。側墻的厚度由沉積的介質層厚度決定。針對側墻刻蝕工藝,主要反應氣體包括C4F8、CH3F、CH2F2、CHF3、CF4等,同時需添加稀釋氣體如O2、Ar和He。對于由二氧化硅和氮化硅組成的ON側墻,通常使用含氫的碳氟化合物氣體(如CH3F、CH2F2、CHF3)進行刻蝕。

在0.8μm及以下的工藝技術中,淀積的隔離側墻介質層為二氧化硅,常用TEOS(四乙基氧化硅)發生分解反應生成,厚度約2000?。TEOS的臺階覆蓋率良好,隨后利用干法刻蝕形成側墻。

側墻介質材料的技術迭代

隨著特征尺寸不斷縮小,側墻介質層材料經歷了多次更新迭代。對于0.8μm及以下工藝,使用單層二氧化硅即可滿足要求。當特征尺寸降至0.35μm以下時,單層二氧化硅已無法滿足器件電性能需求,需采用二氧化硅和氮化硅(SiO2/Si3N4,ON)雙層組合結構。其原因有二:其一,單層刻蝕時沒有停止層,易損傷硅襯底,而雙層結構中下層可作為刻蝕停止層;其二,深亞微米下柵極與漏極接觸填充金屬距離很近,二氧化硅隔離效果不足,氮化硅具有更好的電隔離特性。典型工藝為先LPCVD淀積約200?二氧化硅作為應力緩解層,再淀積約1500?氮化硅。

當特征尺寸進入0.18μm及以下,雙層側墻結構出現新問題:厚度較大的氮化硅會產生應力,使器件發生應變,導致飽和電流減小、漏電流增大。為此引入三明治結構(SiO2/Si3N4/SiO2,ONO),即先淀積約200?二氧化硅、再淀積約400?氮化硅、最后用TEOS生成約1000?二氧化硅。該結構通過減薄氮化硅并由兩層二氧化硅控制應力影響。

當特征尺寸達到90nm及以下時,柵極與漏極間的寄生電容Cgd逐漸增大并影響器件速度。為增大柵極與漏極LDD結構的距離,采用雙重側墻技術:先淀積約50?二氧化硅和約150?氮化硅,刻蝕形成第一重側墻,進行LDD離子注入;隨后再淀積ONO三明治結構作為第二重側墻。第二重側墻的典型工藝為LPCVD淀積約150?二氧化硅、約350?氮化硅、約1000?二氧化硅,依次刻蝕形成最終結構。

側墻工藝隨晶體管尺寸縮小而不斷演進,其介質材料經歷了從單層二氧化硅、雙層二氧化硅/氮化硅、ONO三明治結構到雙重側墻的演變過程。

-

半導體

+關注

關注

339文章

31114瀏覽量

265950 -

工藝

+關注

關注

4文章

718瀏覽量

30378

原文標題:側墻(Spacer)工藝介紹

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

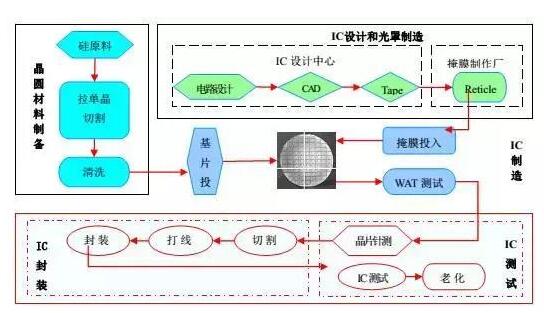

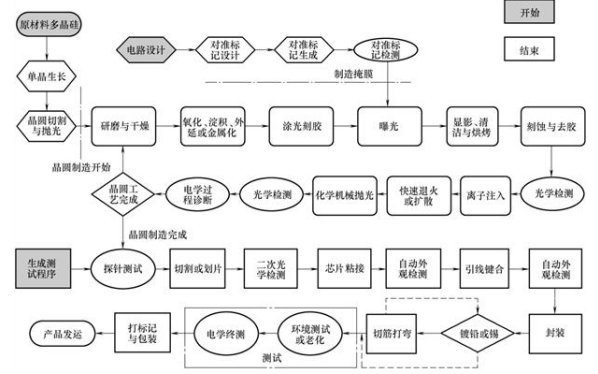

最全最詳盡的半導體制造技術資料,涵蓋晶圓工藝到后端封測

半導體制造的難點匯總

半導體制造工藝中的主要設備及材料大盤點

半導體制造工藝教程的詳細資料免費下載

半導體制造教程之工藝晶體的生長資料概述

兩種標準的半導體制造工藝介紹

半導體制造中的高溫氧化工藝介紹

半導體制造中的側墻工藝介紹

半導體制造中的側墻工藝介紹

評論