MAX1434:高性能八通道10位50Msps ADC的深度解析

在電子設(shè)計(jì)領(lǐng)域,模數(shù)轉(zhuǎn)換器(ADC)是連接模擬世界與數(shù)字世界的關(guān)鍵橋梁。今天,我們來深入探討一款性能卓越的ADC——MAX1434,它由Maxim Integrated推出,適用于醫(yī)療成像和數(shù)字通信等對性能要求極高的應(yīng)用場景。

文件下載:MAX1434.pdf

一、產(chǎn)品概述

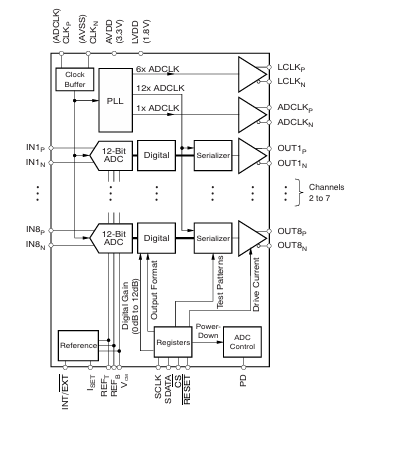

MAX1434是一款八通道、10位的模數(shù)轉(zhuǎn)換器,具備全差分輸入、流水線架構(gòu)和數(shù)字誤差校正功能,采用全差分信號路徑,專為低功耗和高動態(tài)性能而優(yōu)化。它工作在1.8V單電源下,功耗僅767mW(每通道96mW),在5.3MHz輸入頻率下可實(shí)現(xiàn)61dB(典型值)的信噪比(SNR)。此外,它還具有掉電模式,可在空閑時降低功耗。

二、關(guān)鍵特性

(一)出色的動態(tài)性能

- 高信噪比:在5.3MHz輸入頻率下,SNR可達(dá)61dB,能有效抑制噪聲干擾,提高信號質(zhì)量。

- 低失真:84dBc的無雜散動態(tài)范圍(SFDR)和94dB的通道隔離度,確保了信號的純凈度和通道間的獨(dú)立性。

(二)超低功耗

每通道僅96mW的功耗,在正常工作模式下能顯著降低系統(tǒng)的整體功耗,延長設(shè)備的續(xù)航時間。

(三)串行LVDS輸出

- 靈活的輸出模式:支持LVDS/SLVS(可擴(kuò)展低電壓信號)模式,通過引腳選擇,能滿足不同應(yīng)用的需求。

- 長距離傳輸:LVDS輸出支持長達(dá)30英寸的FR - 4背板連接,適用于需要長距離信號傳輸?shù)膱鼍啊?/li>

- 信號完整性測試:具備測試模式,可確保數(shù)字信號的完整性。

(四)全差分模擬輸入

全差分輸入結(jié)構(gòu)能有效抑制共模噪聲,提高抗干擾能力,同時擁有1.4VP - P的寬差分輸入電壓范圍,可適應(yīng)不同幅度的模擬信號。

(五)片上1.24V精密帶隙基準(zhǔn)

內(nèi)部的1.24V精密帶隙基準(zhǔn)為ADC提供了穩(wěn)定的參考電壓,同時也支持外部參考,可根據(jù)需要調(diào)整輸入電壓范圍和提高精度。

(六)時鐘占空比均衡器

單端時鐘控制數(shù)據(jù)轉(zhuǎn)換過程,內(nèi)部的占空比均衡器可補(bǔ)償時鐘占空比的大幅變化,確保轉(zhuǎn)換的準(zhǔn)確性和穩(wěn)定性。

(七)緊湊的封裝

采用14mm x 14mm x 1mm的100引腳TQFP封裝,帶有裸露焊盤,適合在空間有限的設(shè)計(jì)中使用,并且工作溫度范圍為 - 40°C至 + 85°C,能適應(yīng)不同的環(huán)境條件。

三、電氣特性

(一)直流精度

- 分辨率:10位分辨率,能提供較為精確的數(shù)字輸出。

- 積分非線性(INL):±0.1至±1 LSB,保證了轉(zhuǎn)換的線性度。

- 差分非線性(DNL):無漏碼現(xiàn)象,范圍在±0.1至±0.5 LSB之間。

- 偏移誤差:±0.7 %FS,確保了零點(diǎn)的準(zhǔn)確性。

- 增益誤差: - 3至 + 2 %FS,可通過校準(zhǔn)進(jìn)行調(diào)整。

(二)模擬輸入

- 輸入差分范圍:1.4VP - P,能處理較大幅度的差分信號。

- 共模電壓范圍:0.76V,具有一定的共模抑制能力。

- 共模電壓范圍容差:±50mV,保證了在一定范圍內(nèi)的穩(wěn)定性。

- 差分輸入阻抗:2kΩ,適合與不同的信號源匹配。

- 差分輸入電容:12.5pF,對信號的影響較小。

(三)轉(zhuǎn)換速率

- 最大轉(zhuǎn)換速率:50MHz,可實(shí)現(xiàn)高速的數(shù)據(jù)轉(zhuǎn)換。

- 最小轉(zhuǎn)換速率:4.8MHz,能滿足不同的應(yīng)用需求。

- 數(shù)據(jù)延遲:6.5個時鐘周期,在高速轉(zhuǎn)換中需要考慮的延遲因素。

(四)動態(tài)特性

- 信噪比(SNR):在5.3MHz和19.3MHz輸入頻率下,典型值為61.1dB。

- 信噪失真比(SINAD):與SNR相近,反映了信號的整體質(zhì)量。

- 有效位數(shù)(ENOB):在5.3MHz和19.3MHz輸入頻率下,約為9.9位。

- 無雜散動態(tài)范圍(SFDR):在5.3MHz輸入頻率下為84dBc,能有效抑制雜散信號。

- 總諧波失真(THD):在5.3MHz和19.3MHz輸入頻率下,分別為 - 89dBc和 - 91dBc,保證了信號的純凈度。

- 互調(diào)失真(IMD):在5.3MHz和6.3MHz輸入頻率下為86.0dBc,反映了多信號輸入時的性能。

- 三階互調(diào)(IM3):在5.3MHz和6.3MHz輸入頻率下為92.9dBc,對多信號處理有重要意義。

- 孔徑抖動:小于0.4psRMS,確保了采樣的準(zhǔn)確性。

- 孔徑延遲:1ns,在高速采樣中需要考慮的時間因素。

- 小信號帶寬:100MHz,能處理較高頻率的小信號。

- 全功率帶寬:100MHz,可處理較大幅度的信號。

- 輸出噪聲:0.058LSBRMS,保證了輸出信號的質(zhì)量。

- 過范圍恢復(fù)時間:1個時鐘周期,能快速恢復(fù)正常工作。

(五)內(nèi)部參考

- 使能電壓:0.1V,用于控制內(nèi)部參考模式。

- 低泄漏電流:1.5mA,減少了功耗。

- 輸出電壓:1.18至1.30V,典型值為1.24V。

- 參考溫度系數(shù):120ppm/°C,保證了參考電壓的穩(wěn)定性。

(六)外部參考

- 使能電壓:VAVDD - 0.1V,用于控制外部參考模式。

- 高泄漏電流:200μA,需要注意功耗問題。

- 輸入電壓:1.24V,需提供穩(wěn)定的外部參考電壓。

- 輸入電壓容差:±5 %,確保了參考電壓的準(zhǔn)確性。

- 輸入電流:小于1μA,對外部參考源的影響較小。

(七)共模輸出

CMOUT輸出電壓為0.76V,為直流耦合應(yīng)用提供了穩(wěn)定的共模參考電壓。

(八)時鐘輸入

- 輸入高電壓:VAVDD的0.8倍,確保了時鐘信號的正確識別。

- 輸入低電壓:VAVDD的0.2倍,保證了時鐘信號的穩(wěn)定性。

- 時鐘占空比:50%,標(biāo)準(zhǔn)的占空比設(shè)置。

- 時鐘占空比容差:±30%,具有一定的容錯能力。

(九)數(shù)字輸入

- 輸入邏輯高電壓:0.8 x VAVDD,確保了數(shù)字信號的正確識別。

- 輸入邏輯低電壓:0.2 x VAVDD,保證了數(shù)字信號的穩(wěn)定性。

- 輸入泄漏電流:在GND和AVDD輸入時分別為5μA和80μA,需要注意功耗問題。

- 輸入電容:5pF,對信號的影響較小。

(十)LVDS輸出

- 差分輸出電壓:在100Ω負(fù)載下為250至450mV,確保了信號的傳輸強(qiáng)度。

- 輸出共模電壓:1.375mV,提供了穩(wěn)定的共模參考。

- 上升時間:在100Ω負(fù)載和5pF電容下為350ps,保證了信號的快速上升。

- 下降時間:在100Ω負(fù)載和5pF電容下為350ps,確保了信號的快速下降。

(十一)SLVS輸出

- 差分輸出電壓:在100Ω負(fù)載下為205mV,滿足不同的輸出需求。

- 輸出共模電壓:220mV,提供了穩(wěn)定的共模參考。

- 上升時間:在100Ω負(fù)載和5pF電容下為320ps,保證了信號的快速上升。

- 下降時間:在100Ω負(fù)載和5pF電容下為320ps,確保了信號的快速下降。

(十二)掉電模式

- PD下降到輸出使能時間:100ms,從掉電模式恢復(fù)到正常工作的時間。

- PD上升到輸出禁用時間:20ns,進(jìn)入掉電模式的響應(yīng)時間。

(十三)電源要求

- AVDD電源電壓范圍:1.7至1.9V,確保了電源的穩(wěn)定性。

- OVDD電源電壓范圍:1.7至1.9V,為輸出驅(qū)動器提供穩(wěn)定的電源。

- CVDD電源電壓范圍:1.7至3.6V,為時鐘電路提供電源。

- AVDD電源電流:在不同工作模式下有所不同,需要根據(jù)實(shí)際情況進(jìn)行評估。

- OVDD電源電流:同樣在不同工作模式下有所變化,需關(guān)注功耗問題。

- CVDD電源電流:主要用于偏置CLK輸入的ESD保護(hù)二極管,電流較小。

- 功耗:在19.3MHz輸入頻率下為767至882mW,需要合理設(shè)計(jì)散熱方案。

(十四)時序特性

- 數(shù)據(jù)有效到CLKOUT上升/下降時間:根據(jù)采樣率有所變化,需要在設(shè)計(jì)中進(jìn)行精確計(jì)算。

- CLKOUT輸出高寬度:tSAMPLE/10,確保了時鐘信號的正確輸出。

- CLKOUT輸出低寬度:tSAMPLE/10,保證了時鐘信號的穩(wěn)定性。

- FRAME上升到CLKOUT上升時間:根據(jù)采樣率有所變化,需注意時序匹配。

- 采樣CLK上升到FRAME上升時間:在設(shè)計(jì)中需要考慮的時序因素。

- 串?dāng)_: - 94dB,保證了通道間的獨(dú)立性。

- 增益匹配:±0.1dB,確保了各通道增益的一致性。

- 相位匹配:±0.25°,保證了各通道相位的一致性。

四、典型工作特性

通過一系列的圖表展示了MAX1434在不同條件下的性能表現(xiàn),包括信噪比、無雜散動態(tài)范圍、總諧波失真等隨模擬輸入頻率、采樣率、占空比、溫度等因素的變化情況。這些特性曲線為工程師在實(shí)際應(yīng)用中選擇合適的工作參數(shù)提供了重要參考。

五、引腳描述

詳細(xì)介紹了MAX1434的各個引腳功能,包括模擬輸入引腳、電源引腳、時鐘引腳、輸出引腳、參考引腳等。在設(shè)計(jì)PCB時,需要根據(jù)引腳功能合理布局,確保信號的傳輸質(zhì)量和穩(wěn)定性。

六、功能原理

(一)輸入電路

采用全差分輸入結(jié)構(gòu),通過一系列開關(guān)和電容實(shí)現(xiàn)對輸入信號的采樣和保持。在跟蹤模式下,開關(guān)閉合,將輸入信號采樣到電容上;在保持模式下,開關(guān)斷開,將采樣值保持并傳遞給后續(xù)的量化器。

(二)參考配置

支持內(nèi)部和外部參考兩種模式。內(nèi)部參考模式下,REFADJ連接到GND,內(nèi)部帶隙基準(zhǔn)產(chǎn)生1.24V的參考電壓;外部參考模式下,REFADJ連接到AVDD,需要提供穩(wěn)定的外部參考電壓。

(三)時鐘輸入

接受CMOS兼容的時鐘信號,內(nèi)部的占空比均衡器可補(bǔ)償時鐘占空比的變化。低時鐘抖動對于實(shí)現(xiàn)指定的SNR性能至關(guān)重要,需要選擇低抖動的時鐘源。

(四)PLL輸入

通過PLL1、PLL2、PLL3引腳設(shè)置輸入時鐘范圍,PLL可生成5倍于輸入時鐘頻率的輸出時鐘信號,用于驅(qū)動數(shù)據(jù)輸出。

(五)系統(tǒng)時序

詳細(xì)描述了模擬輸入、輸入時鐘、幀對齊輸出、串行時鐘輸出和串行數(shù)據(jù)輸出之間的時序關(guān)系。從采樣到輸出的總時鐘周期延遲為6.5個時鐘周期,需要在設(shè)計(jì)中確保時序的準(zhǔn)確性。

(六)輸出數(shù)據(jù)格式

輸出數(shù)據(jù)格式可通過T/B引腳選擇為偏移二進(jìn)制或二進(jìn)制補(bǔ)碼。不同的輸出格式對應(yīng)不同的轉(zhuǎn)換公式,需要根據(jù)實(shí)際需求進(jìn)行選擇。

(七)LVDS和SLVS信號

通過SLVS/LVDS引腳選擇LVDS或SLVS輸出模式,同時可通過DT引腳選擇是否啟用雙端終端,以提高信號的傳輸質(zhì)量。

(八)LVDS測試模式

通過LVDSTEST引腳可啟用輸出測試模式,輸出固定的測試圖案,用于檢測信號的完整性。

(九)共模輸出

CMOUT引腳提供共模參考電壓,在DC耦合應(yīng)用中,需要將驅(qū)動電路的輸出共模電壓與CMOUT輸出電壓匹配,以減少干擾。

(十)雙端終端

通過DT引腳選擇是否啟用內(nèi)部100Ω終端,可有效減少信號反射,提高信號質(zhì)量。

(十一)掉電模式

通過PD引腳控制掉電模式,在掉電模式下,模擬輸入和數(shù)字輸出的狀態(tài)發(fā)生變化,可降低功耗。

七、應(yīng)用信息

(一)滿量程范圍調(diào)整

MAX1434支持±5%的滿量程調(diào)整范圍,可通過在REFADJ和GND或REFADJ和REFIO之間添加25kΩ至250kΩ的外部電阻或電位器來實(shí)現(xiàn)。

(二)變壓器耦合

使用RF變壓器可將單端輸入信號轉(zhuǎn)換為全差分信號,同時可選擇升壓變壓器以降低驅(qū)動要求,減少信號失真。

(三)接地、旁路和電路板布局

需要采用高速電路板布局技術(shù),將旁路電容盡可能靠近器件放置,使用多層電路板并確保接地和電源平面的完整性,同時隔離模擬和數(shù)字信號,以提高信號的完整性。

八、參數(shù)定義

詳細(xì)解釋了積分非線性(INL)、差分非線性(DNL)、偏移誤差、增益誤差、串?dāng)_、孔徑延遲、孔徑抖動、信噪比(SNR)、信噪失真比(SINAD)、有效位數(shù)(ENOB)、總諧波失真(THD)、無雜散動態(tài)范圍(SFDR)、互調(diào)失真(IMD)、三階互調(diào)(IM3)、小信號帶寬、全功率帶寬、增益匹配和相位匹配等參數(shù)的定義和計(jì)算方法,幫助工程師更好地理解和評估MAX1434的性能。

綜上所述,MAX1434是一款功能強(qiáng)大、性能卓越的ADC,在醫(yī)療成像和數(shù)字通信等領(lǐng)域具有廣泛的應(yīng)用前景。在實(shí)際設(shè)計(jì)中,工程師需要根據(jù)具體需求合理選擇工作參數(shù),優(yōu)化電路板布局,以充分發(fā)揮其性能優(yōu)勢。你在使用MAX1434的過程中遇到過哪些問題呢?歡迎在評論區(qū)分享你的經(jīng)驗(yàn)和見解。

-

adc

+關(guān)注

關(guān)注

100文章

7893瀏覽量

556697 -

電子設(shè)計(jì)

+關(guān)注

關(guān)注

42文章

2405瀏覽量

49906 -

MAX1434

+關(guān)注

關(guān)注

0文章

3瀏覽量

5544

發(fā)布評論請先 登錄

深入剖析LTC1744:高性能14位50Msps ADC的卓越之選

LTC1743:高性能12位、50Msps ADC的全面解析

深度剖析MAX1438:八通道12位65Msps 1.8V ADC的卓越性能與應(yīng)用

深入剖析AD9252:八通道14位50 MSPS串行LVDS 1.8 V ADC

深入解析AD9222:高性能八通道12位ADC的卓越之選

AD9257:八通道14位40/65 MSPS串行LVDS 1.8V模數(shù)轉(zhuǎn)換器深度解析

深入解析LTC2320 - 16:高性能八通道16位ADC的卓越之選

LTC2320 - 14:高性能八通道14位ADC的全面解析

解析ADS1278-HT:一款高性能八通道同步采樣24位ADC

深度解析ADS5281:高性能八通道ADC的卓越之選

MAX1434:高性能八通道10位50Msps ADC的深度解析

MAX1434:高性能八通道10位50Msps ADC的深度解析

評論