MAX19517:高性能雙通道10位130Msps ADC的深度解析

在電子設計領域,模數轉換器(ADC)是連接模擬世界和數字世界的關鍵橋梁。今天,我們來深入探討一款高性能的雙通道10位130Msps ADC——MAX19517,它在通信、醫療、儀器儀表等眾多領域都有著廣泛的應用前景。

文件下載:MAX19517.pdf

一、產品概述

MAX19517是一款雙通道的模數轉換器,具備10位分辨率和高達130Msps的最大采樣率。它的模擬輸入能夠接受0.4V至1.4V的寬輸入共模電壓范圍,這使得它可以采用直流耦合輸入,適用于各種射頻(RF)、中頻(IF)和基帶前端組件。該器件在從基帶至超過400MHz的高輸入頻率范圍內都能提供出色的動態性能,非常適合零中頻(ZIF)和高中頻(IF)采樣應用。

二、關鍵特性

低功耗運行

在130Msps的采樣率下,每個通道的模擬功耗僅為74mW。此外,它在掉電模式下僅消耗1mW,在待機模式下消耗21mW,這種低功耗特性使得它在對功耗要求較高的應用中具有很大的優勢。

寬電源范圍

它可以工作在1.8V的電源下,同時集成的自感應電壓調節器允許其在2.5V至3.3V的電源(AVDD)下工作。數字輸出驅動器則可以在1.8V至3.5V的獨立電源電壓(OVDD)下運行。

出色的動態性能

在(f{IN}=70 MHz)和(f{CLK}=130 MHz)的條件下,典型的信噪比(SNR)性能為59.8dBFS,典型的無雜散動態范圍(SFDR)為82dBc。

可編程特性

通過3線串行端口接口訪問的可編程寄存器,用戶可以進行各種調整和功能選擇。此外,串行端口接口可以禁用,此時三個引腳可用于選擇輸出模式、數據格式和時鐘分頻模式。

靈活的數據輸出

數據輸出通過雙并行CMOS兼容輸出數據總線提供,也可以配置為單復用并行CMOS總線。

小封裝與寬溫度范圍

采用7mm x 7mm的48引腳薄QFN封裝,并且在-40°C至+85°C的擴展溫度范圍內都能正常工作。

三、電氣特性

直流精度

分辨率為10位,積分非線性(INL)在(f{IN}=3MHz)時為-0.8至+0.8 LSB,差分非線性(DNL)在(f{IN}=3MHz)時為-0.7至+0.7 LSB,偏移誤差(OE)在內部參考時為-0.4至+0.4 %FS,增益誤差(GE)在外部參考為1.25V時為-1.5至+1.5 %FS。

模擬輸入

差分輸入電壓范圍為1.5 VP - P,共模輸入電壓范圍為0.4V至1.4V,輸入電阻為4 kΩ,輸入電流為74 μA,輸入電容為0.7至1.2 pF。

轉換速率

最大時鐘頻率為130 MHz,最小時鐘頻率為65 MHz,數據延遲為9個時鐘周期。

動態性能

小信號噪聲底(SSNF)在(f{IN}=70MHz)時小于-35dBFS,信噪比(SNR)在(f{IN}=70MHz)時為58.6至59.8 dBFS,無雜散動態范圍(SFDR)在(f_{IN}=70MHz)時為70.1至82 dBc等。

通道間特性

串擾在(f{INA})或(f{INB}=70MHz)時為95至85 dBc,增益匹配在(f{IN}=70MHz)時為±0.05 dB,偏移匹配在(f{IN}=70MHz)時為±0.15 %FSR,相位匹配在(f_{IN}=70MHz)時為±0.5°。

模擬輸出

CMA和CMB輸出電壓在默認可編程設置下為0.85至0.95V。

內部參考

REFIO輸出電壓為1.23至1.27V,REFIO溫度系數小于±60 ppm/°C。

外部參考

REFIO輸入電壓范圍為1.25 ± 5/-10% V,REFIO輸入電阻為10 ± 20% kΩ。

時鐘輸入

差分時鐘輸入電壓為0.4至2.0 V P - P,差分輸入共模電壓在自偏置時為1.2V,在直流耦合時鐘信號時為1.0至1.4V,輸入電阻在差分默認時為10 kΩ,在內部終端選擇時為100 Ω,共模時為9 kΩ,輸入電容為3 pF。

數字輸入輸出

數字輸入的允許邏輯擺幅為0至VAVDD,輸入高閾值為1.5V,輸入低閾值為0.3V,輸入泄漏電流在不同電壓下有所不同。數字輸出的輸出電壓低為0.2V,輸出電壓高為VOVDD - 0.2V,三態泄漏電流為-0.5至+0.5 μA。

電源管理

從關機狀態喚醒時間為5 ms,從待機狀態喚醒時間為15 μs。

串行端口接口時序

SCLK周期為50 ns,SCLK到CS的建立時間和保持時間均為10 ns,SDIN到SCLK的建立時間為10 ns,SDIN到SCLK的保持時間為0 ns,SCLK到SDIN的輸出數據延遲為10 ns。

時序特性

在雙總線并行模式和復用總線并行模式下,時鐘脈沖寬度高和低均為3.85 ns,時鐘占空比為30至70 %,數據延遲、數據到DCLK的建立時間和保持時間等在不同條件下有相應的數值。

四、引腳描述

MAX19517的引腳功能豐富,包括模擬電源電壓(AVDD)、通道A和B的模擬輸入(INA+、INA-、INB+、INB-)、參考輸入/輸出(REFIO)、時鐘輸入(CLK+、CLK-)、數字輸出(D0A - D9A、D0B - D9B)等。每個引腳都有其特定的功能和作用,在設計電路時需要根據實際需求進行合理連接。

五、詳細工作原理

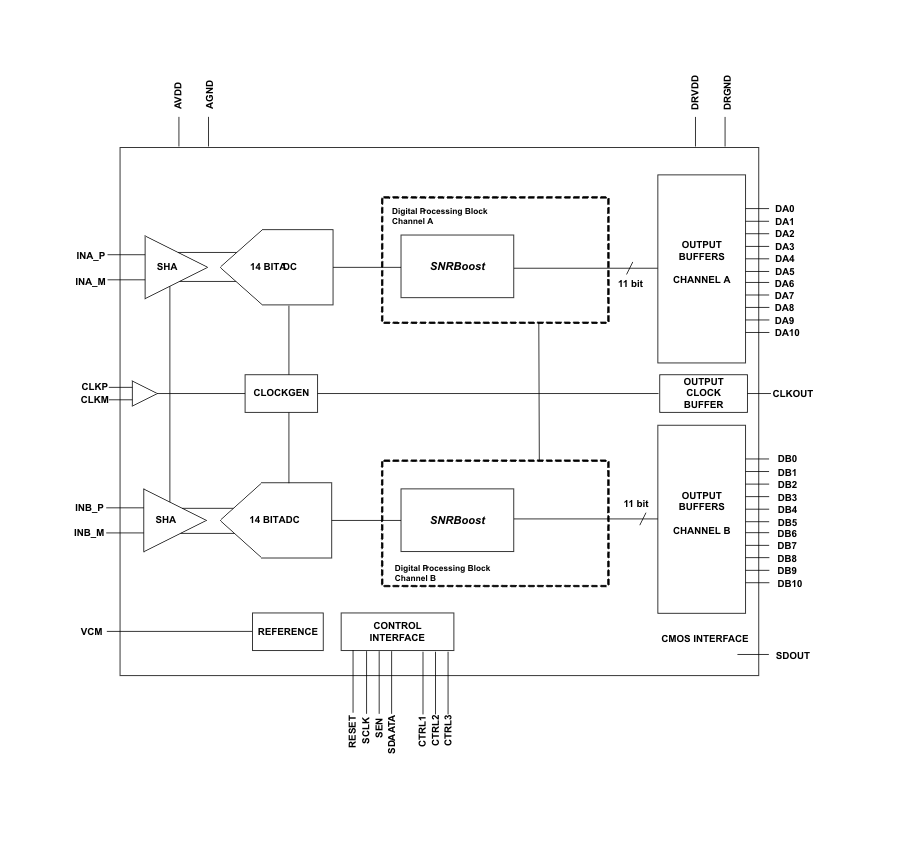

架構

采用10級全差分流水線架構,這種架構允許高速轉換的同時最小化功耗。采樣數據在輸入處每半個時鐘周期逐步通過流水線階段,從輸入到輸出的總延遲為9個時鐘周期。每個流水線轉換器階段將其輸入電壓轉換為數字輸出代碼,除最后一級外,輸入電壓與數字輸出代碼之間的誤差會被放大并傳遞到下一個流水線階段。數字誤差校正用于補償每個流水線階段的ADC比較器偏移,確保沒有丟失代碼。

模擬輸入和共模參考

模擬輸入信號應用于模擬輸入引腳(INA+/INA - 或INB+/INB -),通過輸入采樣開關連接到采樣電容。當輸入采樣開關閉合時,輸入信號通過輸入開關電阻施加到采樣電容上,在輸入開關打開的瞬間進行采樣。流水線ADC處理采樣電壓,數字輸出結果在9個時鐘周期后可用。在輸入開關閉合開始下一個采樣周期之前,采樣電容會被重置到輸入共模電位。共模偏置可以通過外部或內部2kΩ電阻提供。

參考輸入/輸出(REFIO)

REFIO用于調整參考電位,進而調整ADC的滿量程范圍。內部帶隙電壓發生器提供內部參考電壓,該電壓通過10kΩ電阻緩沖并施加到REFIO。通過在REFIO上施加外部電壓,可以微調ADC的滿量程,允許的調整范圍為+5/-15%。

編程和接口

并行接口

將SPEN連接到AVDD可啟用并行接口,提供有限的功能集,通過引腳編程實現特定功能,如選擇輸出格式、時鐘分頻模式等。

串行編程接口

通過CS、SDIN和SCLK輸入對MAX19517的控制寄存器進行編程。串行數據在CS為低電平時,在SCLK的上升沿移入SDIN。通信周期支持兩字節傳輸,第一個字節是控制字節,包含地址和讀寫指令,第二個字節是數據字節。

時鐘輸入

支持全差分時鐘或單端邏輯電平時鐘。對于差分時鐘操作,將差分時鐘連接到CLK+和CLK - 輸入;對于單端操作,將CLK - 連接到GND,通過CLK+輸入邏輯電平信號。

時鐘分頻

提供時鐘分頻選項,可以通過串行接口設置DIV0和DIV1,或者在并行編程配置中使用DIV輸入來啟用時鐘分頻。

同步

使用時鐘分頻時,可以通過滑同步和邊緣同步兩種機制來同步內部時鐘。通過Clock Divide/Data Format/Test Pattern寄存器(06h)中的SYNC_MODE選擇同步模式,并驅動SYNC輸入為高電平進行同步。

數字輸出

具有雙CMOS、可復用、可逆的數據總線。在并行編程模式下,可以使用FORMAT輸入配置數據輸出為偏移二進制、二進制補碼或格雷碼,使用OUTSEL輸入選擇復用或雙總線操作。SPI接口提供更多靈活性,可反轉D0_ - D9_的順序。

可編程數據時序

提供可編程數據時序控制,允許優化時序特性以滿足系統時序要求。通過調整DA_BYPASS、DLY_HALF_T、DTIME<2:0>和DCLKTIME<2:0>等控制信號,可以優化數據輸出延遲和DCLK延遲。

電源管理

SHDN輸入(引腳7)用于切換不同的電源管理狀態,Power Management寄存器(00h)定義了每個電源管理狀態。默認狀態下,(SHDN = 1)關閉MAX19517,(SHDN = 0)恢復全功率。除了關機和待機模式外,還可以通過HPS_SHDN1和HPS_SHDN0激活A + B加法器模式。

六、應用信息

模擬輸入

變壓器耦合差分模擬輸入

MAX19517在全差分輸入信號下具有更好的SFDR和THD性能。使用RF變壓器可以將單端信號轉換為全差分信號,通過連接變壓器的中心抽頭提供共模電壓。不同的變壓器配置適用于不同頻率范圍的信號。

單端交流耦合輸入信號

采用MAX4108提供高速、高帶寬、低噪聲和低失真,以保持輸入信號的完整性。通過內部2kΩ電阻向輸入施加偏置電壓。

直流耦合輸入

由于其寬共模電壓范圍(0.4V至1.4V),允許直流耦合信號,但需要確保共模電壓保持在該范圍內。

時鐘輸入

可以使用單端到差分時鐘輸入轉換電路,如文中所示的電路。

接地、旁路和電路板布局考慮

MAX19517需要高速電路板布局設計技術。所有旁路電容應盡可能靠近器件,最好與ADC在同一側,使用表面貼裝器件以最小化電感。使用多層板和接地、電源平面可以提高信號完整性。高速數字信號走線應遠離敏感的模擬走線,隔離每個轉換器的模擬輸入線以最小化通道間串擾,保持所有信號線短且避免90°轉彎。

七、總結

MAX19517作為一款高性能的雙通道10位130Msps ADC,具有低功耗、寬電源范圍、出色的動態性能、可編程特性等眾多優點。在實際應用中,我們需要根據具體的需求,合理選擇輸入輸出方式、時鐘配置、電源管理模式等,同時注意電路板布局和接地旁路等問題,以充分發揮其性能優勢。希望本文能為電子工程師在設計中使用MAX19517提供有價值的參考。你在使用MAX19517的過程中遇到過哪些問題呢?歡迎在評論區分享交流。

-

adc

+關注

關注

100文章

7893瀏覽量

556697 -

高性能

+關注

關注

0文章

715瀏覽量

21473

發布評論請先 登錄

MAX19517:高性能雙通道10位130Msps ADC的深度解析

MAX19517:高性能雙通道10位130Msps ADC的深度解析

評論