定制 ASIC 設計已不再僅僅是半導體制造商和專業設計公司的專屬領域。如今,一些科技巨頭——其中不乏從未涉足硬件領域的企業——正在組建自己的半導體設計團隊,將芯片設計業務納入內部體系。隨后,他們與代工廠簽訂合同,委托代工廠制造系統級封裝(System-in-Package,SiP),將這些專有器件僅用于其相關產品。

這一趨勢不僅為企業研發創新型 SiP提供了契機,也讓OSAT 和專業基板設計公司能夠為這些產品提供封裝服務。通過合作,這些企業可以將其 IP 和物理設計集成到高質量的 SiP 中。無論貴公司是從事 IP 開發,還是提供器件設計服務,均可參考以下清單,其中列出了當今先進 SiP 所需的主要器件和外設。

設計系統級封裝架構

實際上,SiP 架構的設計方法取決于其所要實現的功能。如今的 SiP 大多是集成了部分內置外設的專用處理器,其目標是縮小系統整體體積并減少 BOM(Bill of Material,物料清單) 數量。由于其他供應商無法提供符合需求的器件,這類 SiP 通常用于特定場景或用途。

總體而言,采用定制 SiP 或等效 SoC 可為設計團隊帶來以下優勢:

將多顆芯片整合為單顆芯片

實現特定功能的異構集成

更易于控制封裝性能,如電源分配

所開發的架構可作為專有設計

系統架構

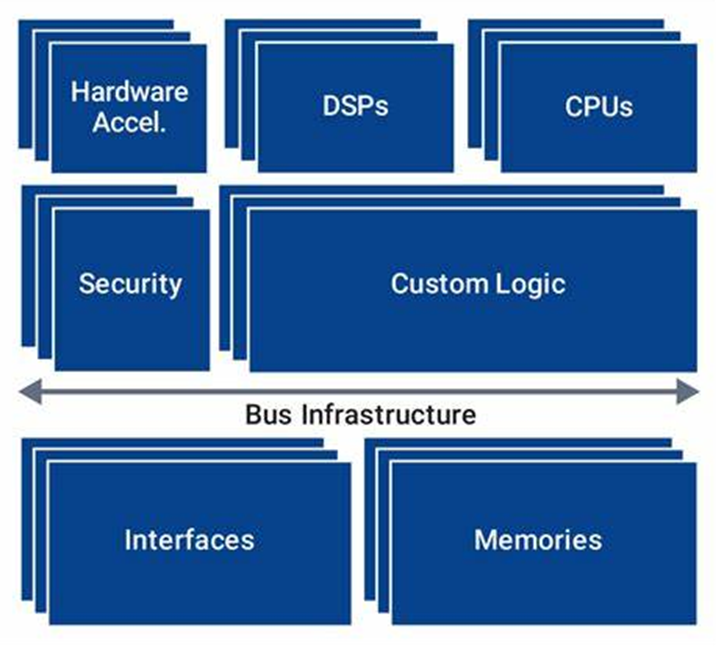

SoC/SiP 系統架構需要一些重要器件來實現基本處理功能并與外設進行信息傳遞。

典型框圖如下所示。在傳統的 SoC 中,所有這些器件通常都集成在同一芯片上。而在 SiP 方案中,部分模塊可作為外部芯片或外設存在。其中,傳感器接口、模擬前端、射頻前端和定制邏輯模塊通常作為外設放置在各自的裸片上,而主處理器模塊及少量內存則與 CPU 放置在同一裸片上。

典型系統架構(WikiChip)

該架構還可擴展至多核處理器,其流量由封裝內的交換器和路由器管理。對于多核處理器而言,這些額外功能將在裸片內實現,未必會增加封裝的復雜程度。隨著外設數量的增加,封裝變得更加復雜,此時可能需要采用 2D、2.5D 或 3D 封裝方案。

封裝類型

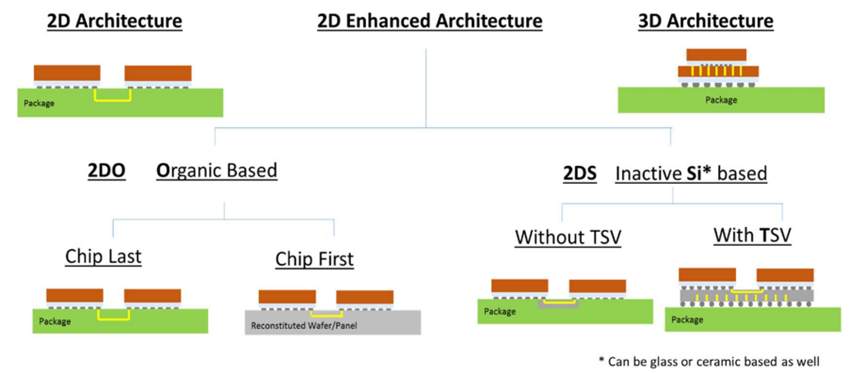

隨著當今更先進的 ASIC 與處理器異構集成,設計人員需選擇與器件最適配的封裝類型。考慮到基板制造商提供的封裝類型和制造能力,部分封裝類型可能無法供應。此外,一些 3D 堆疊封裝需要代工廠提供技術支持,才能成功完成器件制造并證明封裝的可靠性。

截至 2023 年,中國、日本和中國臺灣地區之外的封裝制造能力正在逐步增強。盡管并非所有 3D 堆疊封裝方案均可實現,但 2D 或 2.5D 封裝通常是最易實現的選擇,如基于中介層或直接在基板上封裝。如果需要更高的集成度,例如在具有大量堆疊內存的應用處理器中,則需要采用 3D 堆疊封裝。

2019 年異構集成路線圖中的 2D/2.5D 封裝架構選項(IEEE EPS)

2D 和 2.5D 封裝方式的實現難度通常較低,尤其是在無需中介層的情況下。封裝基板中的布線與 HDI PCB 設計非常相似,再分布層與內部通道從半導體一直延伸到封裝底部的焊球陣列。若采用中介層,則需要在制造和設計中增加一個獨立步驟才能完成封裝,這會增加設計的復雜度和器件的總體成本。

芯粒集成

若無法連通封裝中的芯粒,上述 ASIC 或獨特處理器設計方法將難以實現。芯粒市場正在逐步發展,這為更多設計團隊帶來了機會,使其能夠將獨特功能集成至器件封裝。

目前,芯粒并未作為商用器件通過經銷商在公開市場上銷售。盡管市場上有部分裸片在售,如射頻器件,但此類情況實屬少數,并非行業常態。通常情況下,集成需要通過代工廠開發或生產定制芯粒,或從供應商處獲取 IP 授權。一旦獲取相關數據,便可直接設計封裝,將來自芯粒的信號引出至球柵陣列,隨后接入 PCB。

在打造需要定制 ASIC 的設備時,企業需要一套支持高級封裝的設計工具。Cadence Allegro X Advanced Package Designer 為 PCB 和復雜封裝的設計和實現提供了完整、可擴展的技術:規則驅動的行業標準技術實現了從單芯片到復雜系統的系統規劃、基于先進封測廠(OSAT)和晶圓代工廠(Foundry)的封裝設計,可輕松滿足各類應用場景和復雜程度。

-

半導體

+關注

關注

339文章

30964瀏覽量

265324 -

SiP

+關注

關注

5文章

543瀏覽量

107838 -

封裝

+關注

關注

128文章

9292瀏覽量

148841

發布評論請先 登錄

技術資訊 I 系統級封裝(SiP)的關鍵器件

技術資訊 I 系統級封裝(SiP)的關鍵器件

評論