深入解析 AD9513:高性能時鐘分配芯片的卓越之選

在電子設計領域,時鐘分配芯片對于確保系統(tǒng)的穩(wěn)定性和高性能起著至關重要的作用。今天,我們將深入探討 Analog Devices 公司的 AD9513 時鐘分配芯片,它以其低抖動、低相位噪聲等特性,成為眾多高性能應用的理想選擇。

文件下載:AD9513.pdf

一、AD9513 概述與特性

1. 基本特性

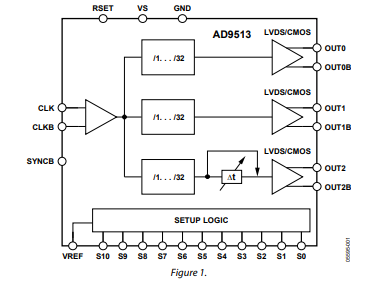

AD9513 是一款具有三個輸出的時鐘分配芯片,設計上著重強調低抖動和低相位噪聲,以最大化數據轉換器的性能。它具備 1.6 GHz 的差分時鐘輸入,三個 800 MHz/250 MHz 的 LVDS/CMOS 時鐘輸出,且輸出抖動僅為 300 fs rms,時間延遲可達 11.6 ns。此外,該芯片通過 4 級邏輯引腳進行配置,采用 32 引腳的 LFCSP 封裝,節(jié)省空間。

2. 應用領域

- 低抖動、低相位噪聲時鐘分配:為對時鐘信號質量要求極高的系統(tǒng)提供穩(wěn)定的時鐘源。

- 高速數據轉換器時鐘:如 ADC、DAC、DDS、DDC、DUC 等,確保數據轉換的高精度和高速度。

- 高性能無線收發(fā)器:滿足無線通信系統(tǒng)對時鐘穩(wěn)定性和低噪聲的要求。

- 高性能儀器儀表:為儀器提供精確的時鐘信號,保證測量的準確性。

- 寬帶基礎設施:支持寬帶通信系統(tǒng)的穩(wěn)定運行。

二、關鍵技術參數分析

1. 時鐘輸入

AD9513 的時鐘輸入頻率范圍為 0 - 1.6 GHz,輸入靈敏度為 150 mVp-p,輸入共模電壓為 1.5 - 1.7 V。需要注意的是,為滿足抖動、相位噪聲和傳播延遲的規(guī)格要求,時鐘輸入的壓擺率需達到 1 V/ns 或更高。

2. 時鐘輸出

- LVDS 輸出:輸出頻率可達 800 MHz,差分輸出電壓為 250 - 450 mV,具備良好的輸出特性。

- CMOS 輸出:輸出頻率為 250 MHz,在帶載能力和輸出電壓方面有特定的參數要求。

3. 時序特性

包括 LVDS 輸出的上升時間、下降時間,以及不同分頻比下的傳播延遲等。同時,還給出了不同輸出之間的偏移和延遲調整的相關參數,這些參數對于確保系統(tǒng)的時序一致性至關重要。

4. 相位噪聲和抖動

從數據手冊中可以看到,AD9513 在不同的輸入頻率、輸出頻率和分頻比下,都有著出色的相位噪聲和抖動性能。例如,在某些情況下,其相位噪聲在 10 Hz 偏移時可達 -100 dBc/Hz 左右,抖動在 300 fs rms 左右。

三、功能模塊詳解

1. 時鐘輸入級

CLK 和 CLKB 為差分時鐘輸入引腳,工作頻率可達 1600 MHz。輸入采用全差分和自偏置方式,信號需通過電容進行交流耦合。若使用單端輸入,需將另一端旁路到交流地。

2. 同步功能

- 上電同步(Power-On SYNC):當電源 (V{s}) 開啟時,若 (V{s}) 在 35 ms 內從 2.2 V 過渡到 3.1 V,可實現上電同步,確保輸出同步啟動。

- SYNCB 引腳同步:在操作過程中,若 AD9513 的設置發(fā)生變化,輸出可能會失去同步。此時,將 SYNCB 引腳拉低并釋放,可使輸出重新同步(除分頻比為 1 的輸出外)。

3. RSET 電阻和 VREF 引腳

- RSET 電阻:用于設置芯片的內部偏置電流,其值應盡可能接近 4.12 kΩ,以保證芯片的正常工作。

- VREF 引腳:提供 ? (V_{s}) 的電壓,作為設置引腳(S0 - S10)的四個邏輯電平之一,為芯片的配置提供參考電壓。

4. 設置配置

AD9513 的具體操作由設置引腳(S10 - S0)上的邏輯電平決定。這些引腳使用四態(tài)邏輯,邏輯電平包括 (V{s})、GND、? (V{s}) 和 ? (V_{s})。通過不同的引腳電平組合,可以設置輸出的邏輯配置、分頻比、相位偏移和延遲等參數。

5. 延遲模塊

OUT2 輸出包含一個模擬延遲塊,可設置 1.8 ns、6.0 ns 或 11.6 ns 的滿量程延遲,每個滿量程延遲還可通過 16 級精細調整。不過,延遲模塊會增加輸出的抖動,因此主要用于為數字芯片提供時鐘,而非數據轉換器的采樣時鐘。

四、電源和功耗

1. 電源要求

AD9513 需使用 3.3 V ± 5% 的電源 (V_{s}),在 PCB 設計中,應遵循良好的工程實踐,對電源和地進行合理布局,并使用足夠的電容進行旁路。

2. 功耗分析

芯片的功耗與輸出模式、分頻比和輸出頻率等因素有關。在不同的工作條件下,功耗有所不同。通過合理配置芯片的功能,如關閉不需要的模塊,可以實現一定的節(jié)能效果。

五、應用信息與設計建議

1. ADC 時鐘應用

在 ADC 時鐘應用中,采樣時鐘的質量對 ADC 的性能影響極大。AD9513 的 LVDS 輸出提供差分時鐘信號,可有效降低噪聲,提高 ADC 的 SNR 性能。在選擇時鐘源時,需考慮 ADC 的輸入要求,如差分或單端、邏輯電平、終端匹配等。

2. LVDS 時鐘分配

AD9513 的 LVDS 輸出采用電流模式輸出級,滿足或超過 ANSI/TIA/EIA - 644 規(guī)范。推薦使用特定的終端電路來確保信號的完整性。

3. CMOS 時鐘分配

CMOS 時鐘分配有一些通用的設計準則,如點對點網絡設計、源端串聯(lián)終端匹配和遠端終端匹配等。由于單端 CMOS 時鐘的局限性,在長距離傳輸高速信號時,建議使用差分輸出。

4. 設置引腳和電源接地考慮

設置引腳的連接和旁路電容的使用對于芯片的正常配置至關重要。在 PCB 設計中,應采用適當的 RF 技術,確保電源旁路和接地良好,以提高芯片的性能。

六、總結

AD9513 作為一款高性能的時鐘分配芯片,以其豐富的功能和出色的性能,為電子工程師在設計高性能系統(tǒng)時提供了一個強大的工具。通過深入了解其技術參數、功能模塊和應用信息,工程師可以更好地利用該芯片,實現系統(tǒng)的優(yōu)化設計。你在使用這類時鐘分配芯片時,遇到過哪些挑戰(zhàn)呢?歡迎在評論區(qū)分享交流。

-

時鐘分配芯片

+關注

關注

0文章

40瀏覽量

2245 -

ad9513

+關注

關注

0文章

3瀏覽量

1543

發(fā)布評論請先 登錄

深入剖析AD9516 - 4:高性能時鐘發(fā)生器的卓越之選

深入解析LMK02002:高精度時鐘調節(jié)器的卓越之選

深入剖析CDCLVC11xx:高性能時鐘緩沖器的卓越之選

探索LMK04832:高性能時鐘調節(jié)器的卓越之選

AD9513 800MHz時鐘分配IC,分頻器,延遲調整,三路輸出技術手冊

深入解析 AD9513:高性能時鐘分配芯片的卓越之選

深入解析 AD9513:高性能時鐘分配芯片的卓越之選

評論