深入剖析AD9512:高性能時鐘分配IC的卓越之選

在電子設計的領域中,時鐘分配對于確保系統的穩定運行和高性能表現起著至關重要的作用。今天,我們將深入探討ADI公司的AD9512時鐘分配IC,它以其低抖動、低相位噪聲的特性,為數據轉換器和其他對時鐘質量要求苛刻的應用提供了理想的解決方案。

文件下載:AD9512.pdf

一、AD9512的核心特性

1. 豐富的輸入輸出配置

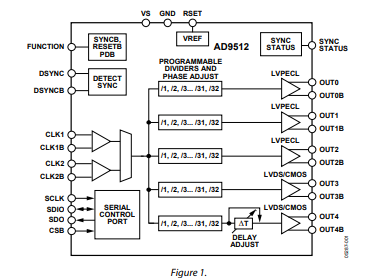

AD9512具備兩個1.6 GHz的差分時鐘輸入,能夠適應高速時鐘信號的輸入需求。它擁有五個可編程的分頻器,分頻比范圍為1到32的整數,為時鐘信號的頻率調整提供了極大的靈活性。輸出方面,有三個獨立的1.2 GHz LVPECL輸出,以及兩個可選擇為800 MHz LVDS或250 MHz CMOS的時鐘輸出,滿足不同設備對時鐘信號電平的要求。

2. 出色的抖動和噪聲性能

在低抖動和低相位噪聲方面,AD9512表現卓越。其LVPECL輸出的附加輸出抖動典型值為225 fs rms,LVDS/CMOS輸出的附加輸出抖動典型值為275 fs rms。這種低抖動特性有助于提高數據轉換器的性能,減少信號失真和誤差。

3. 靈活的相位和延遲調整

通過分頻器的相位選擇功能,AD9512可以實現輸出到輸出的粗延遲調整,方便用戶根據系統需求調整時鐘信號的相對相位。此外,其中一個LVDS/CMOS輸出還具備精細延遲調整功能,延遲范圍可達10 ns,分辨率為5位,提供了32種可能的延遲選擇。

二、技術規格詳解

1. 時鐘輸入特性

AD9512的時鐘輸入頻率范圍為0到1.6 GHz,輸入靈敏度為150 mVp - p,輸入共模電壓為1.5 - 1.7 V。在不同的測試條件下,輸入電阻和電容等參數都有明確的規定,為工程師的設計提供了精確的參考。

2. 時鐘輸出特性

LVPECL輸出:輸出頻率可達1200 MHz,輸出高電壓、低電壓和差分電壓等參數都有明確的范圍,確保輸出信號的穩定性。

LVDS輸出:輸出頻率為800 MHz,差分輸出電壓、偏移電壓等參數符合相關標準,并且具備一定的短路保護能力。

CMOS輸出:輸出頻率為250 MHz,輸出高電壓和低電壓在特定負載條件下有相應的規定。

3. 時序特性

包括輸出上升時間、下降時間、傳播延遲和輸出偏移等參數,在不同的輸出類型(LVPECL、LVDS、CMOS)和分頻比條件下都有詳細的說明。這些參數對于確保時鐘信號在系統中的準確傳輸和同步至關重要。

4. 相位噪聲和抖動特性

詳細給出了不同輸入和輸出頻率組合下的相位噪聲和附加時間抖動數據,幫助工程師評估AD9512在具體應用中的性能表現。

三、功能模塊分析

1. 可編程分頻器

每個時鐘輸出都有獨立的分頻器,可以通過串行控制端口編程設置分頻比。分頻器的設置不僅影響輸出頻率,還與輸出信號的占空比和相位有關。通過合理設置分頻器的參數,可以實現不同頻率、占空比和相位關系的時鐘輸出。

2. 相位偏移設置

每個分頻器都有4位的相位偏移設置和一個起始高/低比特。通過設置相位偏移,可以在同步脈沖后控制時鐘輸出邊沿的起始時間,從而實現輸出到輸出的延遲調整。不同的分頻比下,可用的唯一相位偏移數量等于分頻比本身,并且可以通過計算相位步長將相位偏移轉換為度數。

3. 延遲模塊

OUT4輸出帶有一個模擬延遲元件,可以通過編程設置實現1 ns到10 ns的可變時間延遲。延遲范圍和精細調整由特定的寄存器控制,通過計算相關參數可以精確設置延遲值。但需要注意的是,延遲模塊會增加一定的抖動,因此更適合用于數字芯片的時鐘驅動。

四、電源和控制管理

1. 電源要求

AD9512需要一個3.3 V ± 5%的電源供應,在電源布局和設計時,應遵循良好的工程實踐,使用足夠的電容進行旁路,確保電源的穩定性。同時,RSET電阻的選擇對芯片內部的偏置電流和邏輯電平有重要影響,應使用接近4.12 kΩ的標準1%電阻。

2. 多種電源管理模式

芯片電源關斷模式(PDB):通過將FUNCTION引腳拉低,可以使芯片進入低功耗狀態,大部分功能和電流被關閉,但LVPECL輸出會保持在安全關閉模式。在喚醒時,芯片將恢復到關斷前的設置。

分布電源關斷:通過寫入特定寄存器,可以關閉分布部分的偏置。

單個時鐘輸出電源關斷:可以通過串行控制端口單獨關閉任何一個時鐘輸出,LVPECL輸出具有多種電源關斷模式,以適應不同的輸出負載配置。

單個電路塊電源關斷:可以根據實際需求單獨關閉某些電路塊,如CLK1和CLK2等,實現靈活的功耗管理。

3. 復位和同步模式

復位模式:包括上電復位、通過FUNCTION引腳的異步復位和通過串行端口的軟復位。不同的復位方式可以使芯片恢復到默認設置或特定的狀態。

同步模式:支持單芯片同步和多芯片同步。單芯片同步可以通過設置FUNCTION引腳或寫入特定寄存器實現,使時鐘輸出在已知狀態下同步運行。多芯片同步需要使用DSYNC和DSYNCB引腳,通過比較快時鐘和慢時鐘的邊緣來實現多個AD9512芯片之間的同步。

4. 串行控制端口

AD9512的串行控制端口是一個靈活的、同步的串行通信端口,兼容多種行業標準協議。通過該端口,可以對芯片的所有寄存器進行讀寫操作,支持單字節或多字節傳輸,以及MSB先傳輸或LSB先傳輸的格式。在通信過程中,CSB引腳用于控制通信周期,指令字用于定義數據傳輸的類型(讀或寫)、數據長度和起始寄存器地址。

五、應用案例分析

1. ADC時鐘應用

高速ADC對采樣時鐘的質量非常敏感,時鐘的噪聲、失真和抖動會直接影響ADC的輸出信號質量。AD9512的低抖動LVPECL和LVDS輸出可以為ADC提供高質量的差分時鐘信號,滿足高分辨率和高帶寬ADC的時鐘需求。根據理論公式,采樣時鐘的抖動越小,ADC的SNR越高。在實際應用中,應根據ADC的輸入頻率和分辨率要求選擇合適的時鐘輸出和參數設置。

2. CMOS時鐘分布

AD9512的OUT3和OUT4輸出可以選擇為CMOS電平,用于驅動需要CMOS邏輯電平時鐘輸入的設備。在單端CMOS時鐘分配時,應遵循一些通用的指導原則,如采用點對點網絡、源端串聯終止電阻、控制PCB走線長度等,以確保信號的完整性。當需要驅動長距離或高速信號時,應考慮使用差分輸出,如LVPECL或LVDS。

3. LVPECL和LVDS時鐘分布

LVPECL輸出具有最低的抖動,需要進行直流端接以偏置輸出晶體管。推薦使用標準的LVPECL遠端端接電路,以匹配傳輸線阻抗和開關閾值。LVDS輸出采用電流模式輸出級,具有多種可選的電流水平,標準值為3.5 mA,端接電路應使用100 Ω電阻。

AD9512以其豐富的功能、出色的性能和靈活的配置,為電子工程師在時鐘分配設計中提供了一個強大的工具。在實際應用中,工程師需要根據具體的系統需求和性能要求,合理選擇和配置AD9512的參數,充分發揮其優勢,確保系統的穩定運行和高性能表現。你在使用類似時鐘分配IC的過程中遇到過哪些挑戰呢?歡迎在評論區分享你的經驗。

-

電子設計

+關注

關注

42文章

1974瀏覽量

49873 -

ad9512

+關注

關注

0文章

4瀏覽量

1420

發布評論請先 登錄

AD9512 1.2 GHz時鐘分配IC、2路1.6 GHz輸入、分頻器、延遲調整、5路輸出技術手冊

深入剖析AD9512:高性能時鐘分配IC的卓越之選

深入剖析AD9512:高性能時鐘分配IC的卓越之選

評論