AD4129 - 4:超低功耗16位ADC的卓越之選

在當今對功耗要求日益嚴苛的電子設備設計領域,找到一款既能滿足高性能需求,又能有效降低功耗的模數轉換器(ADC)至關重要。AD4129 - 4就是這樣一款脫穎而出的產品,它以超低功耗、高精度和豐富的功能特性,為低帶寬電池供電應用提供了理想的解決方案。

文件下載:AD4129-4.pdf

一、產品概述

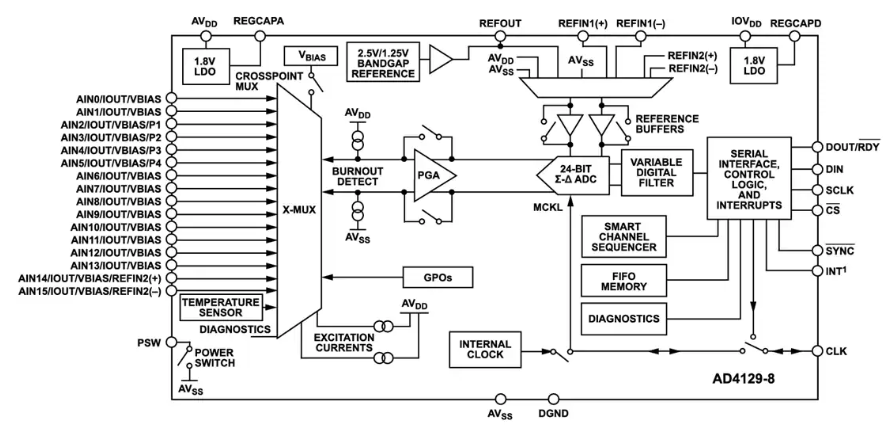

AD4129 - 4是一款超低功耗、高精度的16位Σ - Δ ADC,專為低帶寬電池供電應用而設計。它集成了模擬前端(AFE),包括多路復用器、可編程增益放大器(PGA)、16位Σ - Δ ADC、片上參考和振蕩器、可選濾波器選項、智能序列器、傳感器偏置和激勵選項、診斷功能等。此外,還新增了先進先出(FIFO)緩沖區和占空比循環功能,可顯著延長電池使用壽命。

該產品允許用戶以極低的電流消耗測量低頻信號,連續轉換模式下,增益為1時電流消耗為28.5 μA,增益為128時為32.5 μA。若使用占空比循環選項,平均電流消耗還會更低。它可配置為4個差分輸入或8個單端/偽差分輸入,通過交叉點多路復用器,任何輸入對都可成為PGA和ADC的測量通道輸入。

二、關鍵特性

2.1 超低功耗

AD4129 - 4在不同模式下的電流消耗極低,連續轉換模式(增益 = 128)典型值為32 μA;占空比循環模式(比率 = 1/16)為5 μA;待機模式為0.5 μA;掉電模式為0.1 μA。這種超低功耗特性使其非常適合電池供電的應用場景,能有效延長設備的續航時間。

2.2 系統級節能功能

- 占空比循環比率:支持1/4或1/16的占空比循環比率,可根據實際需求靈活調整,進一步降低功耗。

- 智能序列器:可對每個通道進行預配置,自動按預定順序轉換所有啟用的通道,減少主機處理器的負載。

- 深度嵌入式FIFO:深度為256個樣本,可存儲轉換結果,減少主機處理器與ADC之間的通信頻率,降低系統功耗。

- 自主FIFO中斷功能:當FIFO中的樣本達到預定義值或超過用戶可編程閾值時,可觸發中斷信號,讓主機處理器及時響應。

2.3 高性能指標

- 低噪聲:在1.17 SPS、增益 = 128時,RMS噪聲為25 nV rms(48 nV/√Hz),最高可達16位無噪聲位(增益 = 1)。

- 寬輸出數據速率:輸出數據速率范圍為1.17 SPS至2.4 kSPS,可滿足不同應用的需求。

- 寬電源電壓范圍:可在1.71 V至3.6 V的單電源或±1.8 V的分離電源下工作,單電源低至1.71 V時仍能正常工作,有助于延長電池壽命。

- 高精度參考:帶隙參考的最大漂移為15 ppm/°C,提供穩定的參考電壓。

2.4 豐富的模擬功能

- PGA:可編程增益范圍從1到128,輸入阻抗高、輸入電流低,可直接連接低輸出幅度的傳感器,如電阻橋、熱電偶和電阻溫度探測器(RTD)。

- 低漂移精密電流源:IEXC0和IEXC1電流源可用于激勵2 - 、3 - 和4 - 線RTD,輸出電流選項包括100 nA、10 μA、20 μA、50 μA、100 μA、150 μA和200 μA。

- 低側電源開關:可用于在轉換之間對橋傳感器進行斷電操作,降低系統功耗。

- 熱電偶偏置電壓發生器:可將通道的共模電壓設置為(AV_{DD}/2),方便熱電偶應用。

2.5 強大的診斷功能

包括開路檢測、內部溫度傳感器、參考檢測、模擬輸入過壓和欠壓檢測等。數字接口還具備循環冗余校驗(CRC)和串行接口檢查功能,確保通信鏈路的可靠性。

三、工作原理

3.1 ADC核心

AD4129 - 4采用基于Σ - Δ的ADC核心,由MASH22 Σ - Δ調制器((f_{MOD}=38.4 kHz))和數字濾波器組成。該架構通過過采樣、量化噪聲整形、數字濾波和抽取等技術,在高分辨率、低頻應用中具有顯著優勢。

3.2 數字濾波器

提供多種數字濾波器選項,包括Sinc3、Sinc4、Sinc3 + Sinc1、Sinc4 + Sinc1和后置濾波器等。不同的濾波器選項會影響輸入帶寬、輸出數據速率、噪聲性能、建立時間以及50 Hz和60 Hz抑制能力。用戶可根據具體應用需求選擇合適的濾波器。

3.3 ADC主時鐘

Σ - Δ ADC核心需要76.8 kHz的MCLK來驅動內部調制器。設備默認使用內部振蕩器生成MCLK,也可選擇外部時鐘。使用外部時鐘可使多個ADC由同一個時鐘驅動,實現同步轉換。

3.4 ADC參考

可選擇內部或外部參考電壓。內部集成的帶隙電壓參考可配置為1.25 V或2.5 V低噪聲電壓參考,默認禁用。啟用內部參考時,REFOUT引腳需連接1 nF電容。外部參考可通過REFIN1(±)或REFIN2(±)輸入,適用于比率測量應用。

3.5 模擬前端

- 模擬輸入多路復用器:可配置為4個差分或8個偽差分模擬輸入,靈活的多路復用功能允許用戶選擇任意模擬輸入引腳作為正輸入(AINP)和負輸入(AINM),方便進行診斷和簡化PCB設計。

- 激勵電流:包含兩個獨立的激勵電流源IEXC0和IEXC1,可設置為不同的電流值,并可配置到任意通道。

- 偏置電壓發生器:可在所有模擬輸入通道上選擇偏置電壓,將所選輸入引腳偏置到((AV{DD}-AV{SS})/2),適用于熱電偶應用。

- 通用輸出:具有三個通用輸出(GPO)引腳(P0 - P2),可用于輸出邏輯信號,還可根據配置實現不同的功能,如作為中斷源或指示設備的待機狀態。

- 功率開關:低側功率開關(PSW)可用于對橋傳感器進行斷電操作,降低系統功耗。

3.6 可編程增益放大器

PGA可將多路復用器的輸出放大,增益可編程為1、2、4、8、16、32、64或128。也可通過設置PGA_BYP_n位旁路PGA,此時增益固定為1,可節省功耗并進一步降低噪聲,但會增加模擬輸入電流。

四、寄存器配置與操作

AD4129 - 4具有豐富的寄存器,用于配置設備的各種功能。主要寄存器包括通信寄存器(COMMS)、狀態寄存器(STATUS)、ADC控制寄存器(ADC_CONTROL)、輸入/輸出控制寄存器(IO_CONTROL)等。通過對這些寄存器的設置,用戶可以實現不同的功能,如選擇轉換模式、設置增益、啟用診斷功能等。

4.1 ADC轉換模式

- 連續轉換模式:默認模式,ADC持續對每個啟用的通道進行轉換,完成一個序列后,從最低啟用的通道重新開始。

- 單序列模式:執行一次轉換序列,完成后進入待機模式。

- 占空比循環模式:設備在活動和待機模式之間自動循環,可有效降低功耗。默認占空比循環比率為1/4,也可設置為1/16。

- 單序列 + 空閑/待機同步模式:可通過SYNC引腳觸發單序列轉換,在空閑或待機模式下等待SYNC引腳的低脈沖信號。

4.2 數據準備信號

當ADC轉換完成時,狀態寄存器中的RDYB位從1變為0,可通過配置INT_PIN_SEL位將數據準備信號輸出到指定引腳。當FIFO啟用時,數據準備信號變為FIFO準備信號,指示FIFO是否準備好被讀取。

4.3 連續讀取模式

通過設置ADC_CONTROL寄存器中的CONT_READ位啟用連續讀取模式。在此模式下,無需向COMMS寄存器寫入命令即可讀取數據寄存器,數據準備信號作為輸出數據的幀信號。

4.4 系統同步

SYNC引腳可用于多種操作,如重置調制器、數字濾波器和校準控制邏輯,啟動轉換,同步多個AD4129 - 4設備等。

4.5 ADC校準

提供內部校準和系統校準兩種方式,可更新OFFSET_n和GAIN_n寄存器,消除設備內部或整個系統的偏移和增益誤差。校準模式包括內部偏移校準、內部增益校準、系統偏移校準和系統增益校準。

五、FIFO功能

AD4129 - 4的片上FIFO緩沖區可存儲多達256個轉換結果,有助于進一步降低系統功耗。FIFO有三種模式:禁用模式、水印模式和流式模式。

5.1 水印模式

FIFO收集數據直到達到水印級別,達到后用戶必須讀取所有數據,否則會發生FIFO寫入錯誤。水印級別可通過FIFO_CONTROL寄存器設置。

5.2 流式模式

FIFO始終存儲最新的ADC數據,當FIFO滿時,舊數據會被新數據覆蓋。

5.3 FIFO讀取

通過COMMS寄存器讀取地址0x3D可讀取FIFO緩沖區的內容。讀取時需注意時間,避免數據丟失。

5.4 FIFO中斷

可配置多種中斷模式,如FIFO水印中斷、數據閾值中斷、FIFO空中斷、FIFO讀寫錯誤中斷和FIFO溢出中斷等。中斷信號可通過INT_PIN_SEL位輸出到指定引腳。

六、應用信息

6.1 電源方案

- 單電源操作:(AV{SS})和DGND短接,使用單個電源連接(AV{DD})和(IOV_{DD})。使用真正的雙極性輸入時,需要外部電平轉換電路。

- 分離電源操作:(AV{SS})設置為負電壓,可直接應用真正的雙極性輸入,無需外部電平轉換電路。但需注意絕對最大額定值,且當(AV{SS}≠DGND)時,GPO不能用作數字輸出引腳。

- 獨立正電源操作:(AV{DD})和(IOV{DD})連接到獨立電源,可分別降低到最小值,以最小化功耗。

6.2 推薦去耦

良好的去耦對于高分辨率ADC至關重要。(AV{DD})和(IOV{DD})引腳需分別使用1 μF鉭電容和0.1 μF電容進行去耦,所有模擬輸入和參考輸入也需進行去耦。

6.3 輸入濾波器

需要外部抗混疊濾波器來抑制調制器頻率((f_{MOD}=38.4 kHz))及其倍數的干擾,還可根據需要進行電磁干擾(EMI)濾波。

6.4 微處理器接口

通過標準的4線或3線SPI接口與微處理器連接,兼容大多數數字信號處理器(DSP)和微控制器。

6.5 未使用引腳處理

數字引腳如SYNC、CS和CLK在不使用時需進行適當處理,模擬引腳可保持電氣浮空,但需焊接到PCB以確保機械穩定性。

6.6 上電和初始化

按照推薦的電源供電順序上電,上電后等待(t_{RESET_DELAY})時間再進行SPI事務。建議在初始化程序中進行軟件復位,以確保設備正常工作。

6.7 布局和接地

PCB設計應將模擬和數字部分分開,采用最小蝕刻技術設計接地平面,將去耦電容盡可能靠近設備放置,避免數字線路在設備下方布線,防止噪聲耦合。

6.8 組裝指南

對于WLCSP封裝,熱通過焊球傳遞到PCB,PCB的銅層和接地過孔越多,散熱效果越好。使用與硅的熱膨脹系數(CTE)匹配的PCB材料可提供最佳機械性能,對于有機材料PCB,可使用底部填充材料提高機械性能。

七、總結

AD4129 - 4以其超低功耗、高精度、豐富的功能和靈活的配置選項,為低帶寬電池供電應用提供了全面的解決方案。無論是智能變送器、無線電池和能量收集供電的傳感器節點,還是便攜式儀器、溫度和壓力測量等領域,AD4129 - 4都能發揮出色的性能。在實際設計中,工程師可根據具體需求合理配置寄存器和功能,充分發揮該產品的優勢,打造出高性能、低功耗的電子設備。

-

超低功耗ADC

+關注

關注

0文章

6瀏覽量

5193

發布評論請先 登錄

AD4131 - 4:超低功耗16位Sigma - Delta ADC的卓越之選

AD4129 - 8:超低功耗16位Sigma - Delta ADC的技術解析與應用指南

ADuCM4050:超低功耗ARM Cortex - M4F MCU的卓越之選

STM32L051x6/8:超低功耗32位MCU的卓越之選

STM32L052x6/8:超低功耗32位MCU的卓越之選

Analog Devices Inc. AD4129 16位Σ-Δ ADC特性/應用/框圖

AD4129 - 4:超低功耗16位ADC的卓越之選

AD4129 - 4:超低功耗16位ADC的卓越之選

評論