AD4062:緊湊型低功耗16位SAR ADC的卓越之選

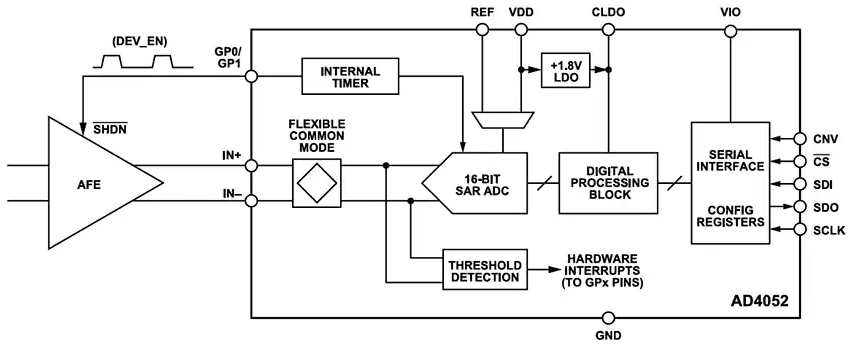

在當今對功耗和性能要求日益嚴苛的電子設計領域,一款優秀的ADC至關重要。AD4062作為一款緊湊型、低功耗的16位逐次逼近寄存器(SAR)模數轉換器(ADC),憑借其獨特的性能和創新特性,成為眾多應用場景的理想選擇。

文件下載:AD4062.pdf

一、AD4062的核心特性

1. 高性能與低功耗的完美平衡

AD4062在性能和功耗之間實現了出色的平衡。它具有±0.5 LSB的最大積分非線性(INL),信噪比(SNR)在 (V_{REF }=3.3 ~V) 時可達86.1dB,每次轉換僅消耗1.35nJ能量。在300kSPS的采樣模式下,功耗僅為405μW;在1MSPS/300kSPS的自主模式下,功耗分別為370μW/112μW,待機功耗更是低至4.1μW。這種低功耗特性使其非常適合電池供電的應用,能夠有效延長設備的續航時間。

2. 易于驅動的設計

其Easy Drive特性極大地簡化了模擬前端(AFE)的設計。小采樣電容(3.4pF)最大化了輸入阻抗,減少了對高帶寬、高功耗放大器的依賴。寬輸入共模范圍支持差分和單端信號鏈,降低了數字主機的活動和功耗。同時,自主采樣功能結合窗口比較器和中斷生成,以及支持突發采樣的平均濾波器,進一步提升了系統的效率和靈活性。

3. 豐富的功能特性

- 多模式操作:支持采樣模式、突發平均模式、監測模式、觸發模式和睡眠模式等多種操作模式,可根據不同的應用需求進行靈活選擇。

- I3C接口:采用2線I3C接口,兼容1.8V至3.3V邏輯,支持循環冗余校驗(CRC),確保數據傳輸的可靠性。

- 溫度范圍廣:工作溫度范圍為?40°C至+125°C,能夠適應各種惡劣的工作環境。

二、工作原理剖析

1. 轉換操作

AD4062的工作分為采集階段和轉換階段。在采集階段,內部的跟蹤保持電路連接到每個輸入引腳(IN+和IN?),獨立采集每個引腳的電壓。當CONV_READ或CONV_TRIGGER寄存器啟動轉換時,進入轉換階段,跟蹤保持電路對采集到的模擬輸入信號進行采樣,SAR ADC核心生成相應的16位數字代碼。

2. 數字處理特性

- 增益縮放:可對16位ADC結果應用16位無符號數字增益因子,用于校準系統增益誤差。通過MONVAL位字段設置增益縮放因子,可在使用VDD作為 (V{REF}) 源時調整ADC傳輸函數。

- 滿量程飽和檢測:當采樣的模擬輸入電壓超出輸入范圍限制時,轉換結果會在數字上飽和。ADC核心和增益縮放塊的輸出都設有飽和檢測塊,檢測到飽和時會設置相應的標志位。

- 塊平均濾波器:具有可編程平均比率( (N_{AVG}) )從2到4096的塊平均濾波器,在突發平均模式下自動啟用,可有效降低噪聲。

3. 內部定時器

內部定時器用于在突發平均模式和自主模式下生成ADC采樣時鐘,采樣頻率由TIMER_CONFIG寄存器中的FS_BURST_AUTO位字段設置,范圍從2MSPS到111SPS。同時,定時器還控制DEV_EN信號延遲,優化系統功耗。

4. 比較器操作

AD4062的ADC核心提供12位窗口比較器模式,用于自主閾值檢測和監測。在自主模式下,內部定時器作為采樣時鐘,比較器對輸入信號進行一系列比較,當信號進入用戶可編程的閾值區域時,生成警報標志和硬件中斷。

三、操作模式詳解

1. 采樣模式

在采樣模式下,轉換啟動觸發單次轉換,轉換結束后生成16位結果,控制器通過I3C總線讀取該結果。最大采樣率受I3C總線輸出數據速率的限制,可通過重復讀取CONV_READ寄存器來實現最快的輸出數據速率。

2. 突發平均模式

突發平均模式下,轉換啟動觸發內部定時器進行一系列轉換,平均濾波器對這些轉換結果進行累積并生成20位平均結果。控制器需等待平均結果準備好后再通過I3C總線讀取。

3. 自主模式

自主模式包括監測模式和觸發模式,允許AD4062自主監測輸入信號,檢測超出范圍的事件。在這兩種模式下,ADC核心進入低功耗比較器模式,功耗較低。

- 監測模式:持續監測輸入信號,當信號超出閾值時,相應的中斷信號會被觸發,內部定時器繼續生成采樣時鐘,當信號回到范圍內時,中斷信號會自動清除。

- 觸發模式:當檢測到閾值交叉時,AD4062自動進行16位轉換,并進入采樣模式,同時發送相應的IBI。

4. 睡眠模式

睡眠模式下,AD4062除數字接口外的所有功能塊都被關閉,功耗低至430nW,適合長時間閑置的應用場景。

四、串行接口與寄存器配置

1. 串行接口

AD4062的數字接口采用2線I3C接口,主要用于讀寫配置寄存器和讀取ADC結果。支持常見命令代碼(CCCs)和帶內中斷(IBIs),但不支持熱加入機制和I2C控制器。

2. 動態尋址

AD4062通過I3C控制器分配的唯一動態地址(TGT_ADDR)進行尋址。設備復位后,控制器需發起動態地址分配(DAA)程序,為每個目標設備分配唯一的7位動態地址。

3. 寄存器操作

- 寄存器地址指針(ADDR_PTR):用于選擇要讀寫的寄存器。

- 寄存器寫入:包括目標寫入請求階段、指令階段和數據階段。

- 寄存器讀取:包括寫入更新ADDR_PTR、目標讀取請求階段和數據階段。

- 寄存器訪問CRC:采用CRC-8進行錯誤檢查,確保數據傳輸的可靠性。

五、應用設計指南

1. 模擬前端設計

- 寬輸入共模范圍:AD4062的模擬輸入具有寬共模輸入電壓范圍,支持差分和單端信號,能夠有效衰減共模信號。

- 等效模擬輸入模型:模擬輸入可建模為開關電容負載,采樣開關在轉換階段斷開和重新連接采樣電容,會導致輸入電流和電壓的瞬態毛刺。建議在IN+和IN?引腳使用RC反沖濾波器來衰減電壓毛刺。

- 噪聲和失真考慮:AFE電路的噪聲和失真規格會影響系統的整體性能,總系統噪聲是AFE RMS噪聲和ADC RMS噪聲的均方根和。建議在放大器電路中進行額外的噪聲或抗混疊濾波。

2. 參考電路設計

- 等效REF輸入模型:AD4062需要外部電壓參考來定義輸入范圍,建議使用低噪聲、穩定的參考源,并在REF引腳附近放置2.2μF的去耦電容,以確保 (V_{REF}) 電壓的穩定。

- 參考噪聲考慮:參考電路的噪聲會影響系統的動態范圍和SNR,對于大輸入信號,參考噪聲會耦合到轉換結果中。

3. 同步放大器關閉和ADC采樣

DEV_EN信號可同步放大器的電源開關和ADC采樣,在采樣前最大化放大器的上電穩定時間。設置t (PWR ON) 延遲大于放大器的開啟時間,以確保放大器輸出在ADC采樣前穩定。

4. 高精度參考關閉

AD4062可選擇VDD作為 (V_{REF}) 源,并通過自動測量VDD和REF輸入電壓的比率,計算數字校正因子來自動縮放ADC采樣結果,從而在關閉外部電壓參考的情況下保持系統精度。

5. VDD功耗

AD4062的ADC核心功耗與采樣率成正比,在較慢的采樣率下,有效功耗更低。不同操作模式下,功耗也有所不同,如在自主模式下功耗更低。

6. 串行接口輸出數據速率計算

AD4062的最大輸出數據速率受操作條件和串行接口規格的限制,使用CONV_READ觸發ADC轉換可實現更快的輸出數據速率。

7. 布局建議

- 確保PCB層中有實心接地平面,AD4062的GND引腳與接地平面層之間有低阻抗連接。

- 模擬輸入和REF跡線與數字接口跡線物理分離,避免串擾。

- 降低電壓參考電路與AD4062 REF引腳之間的阻抗,在REF引腳附近放置低ESR去耦電容。

六、總結

AD4062以其高性能、低功耗、豐富的功能特性和靈活的操作模式,為電子工程師提供了一個優秀的ADC解決方案。無論是在電池供電的數據采集、生命體征監測,還是生物化學分析、地質地震傳感等領域,AD4062都能發揮出色的性能。在實際應用中,工程師需要根據具體需求合理選擇操作模式,優化電路設計和布局,以充分發揮AD4062的優勢。你在使用AD4062的過程中遇到過哪些問題呢?歡迎在評論區分享你的經驗和見解。

-

電子設計

+關注

關注

42文章

2002瀏覽量

49878

發布評論請先 登錄

深入解析AD4630 - 16/AD4632 - 16:高性能雙通道SAR ADC的卓越之選

AD4131 - 4:超低功耗16位Sigma - Delta ADC的卓越之選

Amphenol Rugged SOM:超緊湊型嵌入式計算機模塊的卓越之選

深入解析ADS8507:16位低功耗采樣ADC的卓越之選

Analog Devices Inc. AD4052緊湊型低功耗Easy Drive SAR模數轉換器數據手冊

AD4062:緊湊型低功耗16位SAR ADC的卓越之選

AD4062:緊湊型低功耗16位SAR ADC的卓越之選

評論