電源模塊在電子系統中提供了最關鍵的功能之一,因為它們的行為影響系統在不同工作模式(啟動、關閉、穩態運行)下的表現以及發生故障時的表現——這對于實現功能安全應用中的安全狀態至關重要。需要注意的是,系統性能力是滿足基本功能安全標準的三項關鍵要求之一。這項要求側重于預防和控制系統性故障,即由于設計缺陷、技術規格偏差和管理流程不善引起的故障。面對此類要求,必須解決電源的系統性故障。

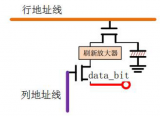

為了消除電源引起的系統性故障,需要使用正確的技術規格,提供必要的時序控制,并確保負載始終在其裕量范圍內運行。如圖1所示,傳感器子系統中的圖像傳感器和邏輯子系統中的微控制器是安全相關系統中最易受影響的元器件之一。如果系統復位時涉及自動重啟此類子系統的電源,則這些元器件可能會損壞。

圖1. 自主移動機器人(AMR)子系統示例

對于圖像傳感器而言,不完整的上電或關斷周期會使電路承受電氣應力。當系統關斷時,圖像傳感器的電源也應盡快關斷,以便圖像傳感器在理想條件下(即電路中沒有殘留電壓)迅速重新啟動。如果傳感器由典型線性穩壓器供電,即使穩壓器的電源關閉,穩壓器的輸出通常也會由輸出電容予以維持,使圖像傳感器保持通電狀態。這種情況可能會干擾系統預期的關斷和開啟操作。圖2顯示了一個電源示例,輸出電壓為3.3 V,輸出電容為10 μF。利用 LTspice進行仿真,此示例在10 kΩ負載下的放電時間為160 ms。

圖2. 電源示例:(a)LDO;(b)輸出電壓放電時間

使用輸出放電功能

為了確保關斷時輸出電壓完全放電,一種方法是使用輸出放電功能。對于需要精確電源時序和更快關斷時間的應用而言,這類功能必不可少,能夠在系統關斷時處理電源軌的浮地輸出,從而緩解電源循環過程中可能出現的問題。圖3顯示了有輸出放電功能和無輸出放電功能的輸出電壓曲線示例。

圖3. 輸出放電操作

添加外部MOSFET作為放電電路

在最近的電源管理設計中,越來越多的低壓差(LDO)穩壓器引入了附加功能,其中電源良好信號(PGOOD)已成為一項越來越常見的功能。PGOOD信號是LDO的一種狀態輸出,通常用于告知系統輸出電壓已達到并正在保持適當的穩壓值。在大多數實現方式中,此信號來自一個開漏MOSFET,其狀態會根據穩壓器的狀態而改變。當LDO輸出處于穩壓范圍內時,PGOOD MOSFET關斷,使得該引腳處于高阻抗狀態,并使PGOOD輸出引腳被拉高。這種情況如圖4a所示。而當輸出超出范圍時,MOSFET會導通,通過其低阻抗路徑將PGOOD引腳拉低。這種配置使得PGOOD信號能夠輕松地與不同的邏輯電平和電源電壓連接,因此具有良好的通用性和廣泛的適用范圍。這種情況如圖4b所示。

然而,這也帶來了設計上的挑戰。大多數LDO PGOOD輸出采用的開漏MOSFET主要用于輔助管理任務,只能吸收少量電流,并不適合直接從輸出電容中吸收大電流,尤其是在LDO禁用或關斷時輸出需要快速放電的情況下。若強行嘗試用它來承載大電流,可能會損壞器件,或者根本行不通。

圖4. PGOOD信號演示:(a)置為有效時;(b)置為無效時

更穩健的解決方案是將PGOOD信號與外部MOSFET電路結合,形成受控放電路徑。如圖5所示,此電路使用放電電阻R1,后者決定了輸出電容的放電速度。設計人員可根據所需的放電時間確定該電阻的大小。較大的電阻會使電容放電更慢,而較小的電阻會加快放電速度。在這種配置中,MOSFET Q1用作放電開關;當通過使能引腳(EN)禁用轉換器時,此開關導通。同時,Q2負責反轉來自LDO的PGOOD信號的邏輯,確保Q1以正確的時序激活。這種設置可實現完全定制的有源放電電路,能夠根據LDO的狀態作出適當響應。

圖5. (a)利用LT3045的PGOOD信號來觸發外部MOSFET,實現放電電路;(b)在10 kΩ負載下,放電時間為3.2 ms

圖6. (a) LT3063示例電路;(b)在10 kΩ輸出負載下,放電時間為0.5 ms

采用這種方法,任何配備PGOOD引腳的LDO都能有效地新增外部有源輸出放電功能。這為設計人員提供了極大的靈活性,讓他們能夠微調電源軌的放電曲線。然而,其代價是需要使用外部元件,因而成本和電路板占用空間都會增加。盡管如此,在需要精確控制放電的應用中,這仍然是一種有價值且可定制的解決方案。

實現集成解決方案

為了在不借助外部電路的情況下滿足這一需求,ADI公司提供了集成有源放電功能的LDO解決方案。例如, LT3063內置了有源輸出放電機制,可簡化設計過程,減少元件數量,節省PCB空間,同時還能實現快速放電。如圖6所示,使用該器件可實現0.5 ms的放電時間,與圖5中的示例相比,改善效果明顯。

圖7. (a) LT2928示例電路;(b)在10 kΩ負載下,放電時間為6.5 ms

在安全關鍵應用中,為了實現更高的可靠性和足夠的獨立性,最好采用單獨的監控電路。LTC2928等電源時序控制器集成了過壓和欠壓監控功能,可確保符合功能安全要求,同時支持電源時序控制和輸出放電。圖7顯示的是一個示例電路。其他具有輸出放電功能的監控電路包括MAX16050和MAX16051。

結論

為了選擇合適的方法來解決電源輸出的放電性能問題,需要對設計要求和工作條件進行全面評估。實現有源輸出放電的多種方法各有優勢和不足。有些解決方案在特定的輸出或應用場景下可能更有效,而其他方法在不同條件下可能性能更佳。 因此,了解每種技術的特點和局限性是確保實施效果達到最優的關鍵。

在需要較高輸出電壓或最大靈活性的應用中,通常首選外部MOSFET。但是,設計人員必須愿意接受更高的成本、更大的電路板占用空間和逆變電路帶來的額外功耗。對于低功耗或空間受限的設計而言,集成解決方案通常是最佳選擇,無需額外的元件,同時還能降低功耗。缺點是這類方案的可用性較為有限,因為只有某些LDO支持此特性。此外,監控電路非常適合具有多個輸出軌且注重電源時序的系統。雖然監控電路的MOSFET灌電流有限,對于大輸出電容而言效果差強人意,但在注重時序控制、系統協調及功能安全獨立性的應用場景中,監控電路仍是很好的選擇。總之,選擇何種方法,取決于方法的優勢是否與應用對輸出電壓、空間、放電時間和時序控制的特定要求相契合。

-

電源

+關注

關注

185文章

18903瀏覽量

263974 -

傳感器

+關注

關注

2577文章

55213瀏覽量

792556 -

穩壓器

+關注

關注

24文章

4950瀏覽量

100124 -

ldo

+關注

關注

35文章

2457瀏覽量

160234

原文標題:利用輸出放電解決電源的系統性故障

文章出處:【微信號:analog_devices,微信公眾號:analog_devices】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

電解的脈沖放電特性

提高DCS控制系統電源可靠性的方案

如何影響FFX輸出并最終影響系統性能?

如何利用GPRS設計GIS局部放電監測系統?

spacex火箭爆炸的真實原因或是存在系統性安全故障

新手必看!FPGA的系統性學習

利用輸出放電解決電源的系統性故障

利用輸出放電解決電源的系統性故障

評論