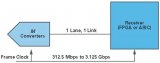

上一篇文章提到,數(shù)據(jù)轉換器(ADC/DAC)的分辨率和采樣率呈指數(shù)級增長。數(shù)據(jù)轉換器(ADC/DAC)的分辨率和采樣率呈指數(shù)級增長。為應對這一瓶頸,JEDEC固態(tài)技術協(xié)會推出的JESD204標準旨,為大家詳細介紹了高速串行JESD204B/C/D標準、高速DAC接收機(RX)面臨的物理層測試挑戰(zhàn)等內(nèi)容,并結合SL3000系列誤碼儀的技術指標、功能指標等給出針對JESD204C 物理層一致性測試的實際測試方案。

接收機抖動容限(Jitter Tolerance, JTOL)測試

接收機均衡能力與眼圖靈敏度測試

本文將基于前文所述測試方法,實現(xiàn)對高速DAC接收機的全面驗證,關鍵在于測試系統(tǒng)是否具備連續(xù)速率輸出、精確抖動注入以及真實信道環(huán)境模擬能力。

針對JESD204C/D DAC測試中的關鍵需求,中星聯(lián)華科技SL3000系列誤碼分析儀,圍繞上述測試方法的工程實現(xiàn),提供了完整的測試能力與實現(xiàn)路徑。

SL3000系列誤碼儀

中星聯(lián)華SL3000系列誤碼儀的特點

針對JESD204C/D DAC測試的痛點,中星聯(lián)華科技推出的SL3000BX系列誤碼分析儀(BERT)憑借其獨特的硬件架構,提供了超越傳統(tǒng)通用儀器的測試能力。

0.5G至33G連續(xù)速率可調(diào):覆蓋全協(xié)議棧

JESD204C標準向下兼容,且不同應用場景下的速率配置極多(例如通過通過降速來換取更遠的傳輸距離)。

傳統(tǒng)痛點:許多誤碼儀僅支持特定的標準頻點(如10G, 25G),在測試非標速率或進行“超頻”余量摸底時無能為力。

SL3000優(yōu)勢:無斷點連續(xù)可調(diào),支持未來更高的JESD-204D標準。這意味著研發(fā)人員可以從幾百Mbps一路掃描至32 Gbps,繪制出DAC接收機在不同頻率下的靈敏度曲線(Bathtub Curve),精準定位CDR環(huán)路帶寬的拐點。這對于驗證DAC內(nèi)部PLL的鎖定范圍(Lock Range)至關重要。

高級抖動注入能力:模擬真實惡劣環(huán)境

這是物理層壓力測試的核心。SL3000不僅能產(chǎn)生理想信號,更能充當“信號破壞者”。

低頻周期性抖動(SJ):模擬開關電源(DC-DC)噪聲干擾。SL3000支持注入從10KHZ到10MHz頻率的SJ,直接考驗DAC CDR的抖動容限(Jitter Tolerance)。

高頻周期性抖動(PJ):模擬系統(tǒng)時鐘串擾等高頻確定性干擾。SL3000支持注入大于10MHz的PJ,直接考驗DAC CDR的抖動容限(Jitter Tolerance)。

中星聯(lián)華誤碼儀PPG輸出10MHz 抖動

發(fā)射端上升/下降時間濾波器(Rise/Fall Time Filters):JCOM算法會針對不同的Tx模型優(yōu)化信號的轉換時間。SL3000 具備硬件級的上升時間可調(diào)功能(Tunable Transition Time)。用戶可以在15ps至35ps范圍內(nèi)連續(xù)調(diào)節(jié)輸出信號的邊沿速率。這一特性使得研發(fā)人員能夠物理復現(xiàn)JCOM仿真中設定的不同壓擺率(Slew Rate)場景,驗證DAC接收端在不同邊沿速度下的建立/保持時間裕量,而無需更換硬件濾波器。

·發(fā)射端前饋均衡(Tx FFE):對于Class C-M和C-R鏈路,標準要求Tx具備特定的預加重能力以補償信道損耗。SL3000 PPG支持2個Pre-cursor + 1個Post-cursor的高精度均衡,且抽頭系數(shù)支持0.1dB步進微調(diào)。

符號間干擾(ISI):通過可變插損的高速ISI 通道板來實現(xiàn),支持模擬從5dB到30dB的各種不同的插損環(huán)境。

高速ISI插損板外觀

ISI 插損板支持各種不同插入損耗曲線

模擬串擾:通過高速信號完整性損傷板來實現(xiàn),支持模擬各種真實世界的串擾,skew等問題。

高速信號完整性損傷板注入串擾噪聲測試環(huán)境

無串擾耦合噪聲眼圖

VS

串擾耦合噪聲后眼圖

自定義碼型(User Defined Pattern): SL3000系列誤碼儀支持超過8Mb長度的自定義序列。

SL3000進行高性能DAC芯片

測試和調(diào)試實例

在實際支持客戶測試的過程中,公司發(fā)現(xiàn)客戶研發(fā)的一款高性能DAC,采用JESD204C接口,單通道速率很大支持12.5Gbps 到32 Gbps。但在初期流片驗證中,在特定PCB板上偶爾出現(xiàn)鏈路失鎖,且模擬輸出的底噪異常抬高。針對上述情況我們協(xié)助客戶迅速定位問題并提出下述解決方案。

問題定位

使用常規(guī)BERT測試,眼圖和誤碼率看似正常。使用中星聯(lián)華SL3000系列介入后,通過其高級PJ注入功能,工程師在7.8 MHz頻點注入0.6 UI的抖動時,瞬間復現(xiàn)了鏈路失鎖故障。

根因分析

經(jīng)排查,該PCB板上的供電模塊(VRM)在重載下存在約7.8 MHz的開關紋波耦合到了DAC的SerDes電源域。而該DAC的CDR環(huán)路帶寬設計恰好在40-60 MHz附近存在增益峰值(Peaking),導致對該頻率的抖動不僅沒有抑制,反而進行了放大,最終導致采樣時序違規(guī)。

解決方案與驗證

優(yōu)化CDR的環(huán)路濾波器參數(shù),壓低帶內(nèi)峰值。

優(yōu)化電源去耦電容。

回歸測試: 再次使用SL3000注入100K-10MHz 抖動,幅度提升至0.8UI,DAC依然穩(wěn)定鎖定,指標滿足要求。

SL3000系列誤碼儀的寬頻段抖動注入能力,幫助客戶發(fā)現(xiàn)了常規(guī)手段無法檢測的“設計死角”,避免了潛在的批量召回風險,顯著提升了芯片的量產(chǎn)可靠性。

隨著JESD204C/D標準的普及,高速DAC的物理層測試已不再是簡單的數(shù)字邏輯驗證,而是涉及信號完整性、電源完整性及模擬性能的跨域系統(tǒng)工程。

中星聯(lián)華科技SL3000系列誤碼儀,憑借其連續(xù)速率覆蓋,深度抖動注入等差異化優(yōu)勢,完美契合高端DAC芯片設計與系統(tǒng)集成的測試需求。它不僅是一臺誤碼測試儀器,更是探測芯片物理極限、優(yōu)化系統(tǒng)設計的強力工具。

-

接收機

+關注

關注

9文章

1247瀏覽量

56369 -

dac

+關注

關注

44文章

2739瀏覽量

197383 -

壓力測試

+關注

關注

0文章

31瀏覽量

13806

發(fā)布評論請先 登錄

JESD204B有專用于ADC/DAC和FPGA或ASIC的接口嗎?

JESD204B的系統(tǒng)級優(yōu)勢

在Xilinx FPGA上快速實現(xiàn)JESD204B

JESD204 v5.2約束使用生成的dcp構建邏輯計時失敗

JESD204接口簡介

串行LVDS和JESD204B的對比

JESD204標準解析

FPGA高速數(shù)據(jù)采集設計之JESD204B接口應用場景

AD9683的引腳如何與zynq 7015芯片中的JESD204 ip核端口對應相連?

采用JESD204標準的高速串行接口的應用

JESD204——它是什么?

一種連接數(shù)據(jù)轉換器和邏輯器件的高速串行接口—JESD204介紹

技術文章|高速DAC JESD204接口接收機物理層壓力測試(上)

技術文章|高速DAC JESD204接口接收機物理層壓力測試(下)

技術文章|高速DAC JESD204接口接收機物理層壓力測試(下)

評論