隨著無線通信向5G/6G演進以及雷達系統向寬帶多模發展,高速數模轉換器(DAC)的采樣率已突破GSPS量級,數據接口從傳統的并行LVDS全面轉向高速串行JESD204B/C/D標準。在雷達,電子偵察(ESM)與干擾吊艙中,寬帶接收機前端的 ADC/DAC 會在極惡劣的信噪比(SNR)下工作。伴隨半導體發熱以及無界熱噪聲會嚴重污染基帶高速數據接口,傳統的“連通性”測試已無法滿足高可靠性芯片的設計需求,必須引入包含抖動注入(Jitter Injection)的壓力測試(Stress Test)來摸底芯片的物理層余量。

本文深入探討了JESD204C/D標準的物理層特性,結合中星聯華科技SL3000系列誤碼儀的五大核心優勢——高級抖動注入、通道間相位微調、高級自定義碼型支持,0.5G-32G連續速率覆蓋,以及信號完整性損傷板模擬真實惡劣環境, 插損板模擬標準要求的MR/LR插損場景,詳細闡述了如何構建高保真的DAC接收機壓力測試環境。文章重點分析了如何利用PJ注入模擬電源噪聲與系統干擾,徹底評估DAC的時鐘恢復(CDR)魯棒性及最終的模擬輸出性能,為提升國產高端DAC芯片的產品化可靠性提供實踐指導。

SL3000系列誤碼儀

高速數據轉換器接口的演進與挑戰

從LVDS到JESD204C/D的跨越

在過去十年中,數據轉換器(ADC/DAC)的分辨率和采樣率呈指數級增長。采用傳統的并行CMOS或LVDS接口,意味著需要數百個I/O引腳,這在PCB布線密度、封裝成本以及通道間時序對齊(Skew)方面都是不可接受的。

JEDEC固態技術協會推出的JESD204標準旨在解決這一瓶頸。

JESD204B:引入了確定性延遲(Deterministic Latency),通過Subclass 1(基于SYSREF)實現多芯片同步,最高速率達到12.5 Gbps,采用8b/10b編碼。

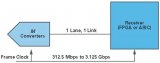

JESD204C:為了提高傳輸效率,引入了64b/66b編碼,降低了編碼開銷(從20%降至3%),單通道速率提升至32 Gbps。物理層定義了從Class A到Class C的多種類別,以適應不同長度的信道損耗。

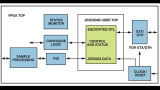

典型DAC和FPGA的應用框圖實例

JESD要求的不同速率

高速DAC接收機(RX)

面臨的物理層測試挑戰

在JESD204鏈路中,DAC芯片充當接收機(RX)的角色,FPGA或ASIC充當發射機(TX)。隨著速率邁向32 Gbps,物理層面臨信號完整性的挑戰:

信道損耗(Insertion Loss):PCB走線在高頻下的介質損耗和集膚效應導致信號眼圖閉合。DAC接收端必須具備強大的連續時間線性均衡(CTLE)和判決反饋均衡(DFE)能力。

抖動(Jitter):在數十Gbps速率下,單位間隔(UI)僅為30ps左右。來自參考時鐘的相位噪聲、電源紋波引入的周期性抖動(PJ)、以及熱噪聲引入的隨機抖動(RJ),都會壓縮采樣窗口,導致誤碼。

失真和噪聲:在超過25Gbps的串擾和噪聲更加嚴重,影響RX接收機的余量 。

傳統的“完美眼圖”測試無法體現電子戰設備在干擾壓制下的魯棒性,僅在理想條件下測試DAC“能工作”是遠遠不夠的。標準要求必須在測試階段引入壓力測試,人為惡化輸入信號質量,探測芯片在極限條件下的生存能力(余量)。

JESD204C/D 物理層接收機測試

接收機抖動容限(Jitter Tolerance, JTOL)測試

DAC內部集成了時鐘數據恢復(CDR)電路,用于從高速串行流中提取采樣時鐘。CDR本質上是一個低通濾波器,它能跟蹤低頻抖動,但無法跟蹤高頻抖動。如果在CDR帶寬之外存在過大的抖動,就會導致采樣錯誤,進而不僅產生數字誤碼。

SL3000應用方案:

測試搭建:將SL3000的PPG輸出連接至DAC的JESD輸入端。DAC配置為通過SPI/I2C讀取內部誤碼計數器(Error Counter),或將解幀后的數據環回至BERT的ED(若支持)。

基準測試:設置目標速率(如12.5 Gbps),不加抖動,調整SL3000的輸出擺幅和預加重,確保DAC無誤碼鎖定。

高級抖動注入(關鍵步驟):

利用SL3000的抖動注入功能,掃描SJ和PJ頻率,從1KHz級別一直掃描至40MHz.。

通過觀察DAC在哪個抖動頻率下開始出現誤碼或失鎖,可以精確反推DAC內部CDR的環路帶寬。SL3000支持的高頻PJ注入能力在此處無可替代,因為很多電源噪聲和時鐘耦合干擾 harmonics 恰好落在10MHz-40MHz區間。

接收機均衡能力與眼圖靈敏度測試

JESD204C定義了不同等級的信道損耗(如Class C-R支持高損耗)。DAC接收端必須通過CTLE/DFE張開閉合的眼圖。

SL3000應用方案:

最小輸入幅度測試:利用SL3000輸出幅度的連續可調特性,逐漸降低差分擺幅(例如從800mV降至200mV),測試DAC的輸入靈敏度。

模擬長信道:在SL3000與DAC之間串入不同長度的ISI插損板,迫使DAC內部的CTLE/DFE全速工作。

通過上述測試方法,可以對DAC接收機在抖動、信道損耗及輸入幅度等多維條件下的性能進行系統性驗證,從而全面評估其物理層設計的魯棒性與性能余量。

在實際工程中,這類測試不僅需要覆蓋寬頻段抖動掃描、多種信道損耗條件,還涉及復雜的信號質量調控與環境模擬,對測試系統的能力提出了極高要求。

圍繞上述測試需求,下篇我們將針對JESD204C/D DAC測試中的關鍵需求,詳述中星聯華SL3000系列誤碼儀測試方法的工程實現與實例,剖析SL3000系列為何會成為JESD204C/D DAC測試的理想平臺。

SL3000系列誤碼儀的五大核心優勢

具有高級抖動注入、高壓和噪聲增加等功能

通道間相位可調

支持高級自定義碼型

連續速率范圍覆蓋0.5G-32G

模擬真實的信號完整性損傷板環境及插損板標準要求的MR/LR插損場景

精彩預告

后續將針對JESD204C/D DAC測試中的關鍵需求,詳述中星聯華SL3000系列誤碼儀測試方法的工程實現與實例。

-

測試

+關注

關注

9文章

6277瀏覽量

131492 -

接口

+關注

關注

33文章

9550瀏覽量

157290 -

接收機

+關注

關注

9文章

1247瀏覽量

56333 -

dac

+關注

關注

44文章

2726瀏覽量

197271

發布評論請先 登錄

JESD204B的系統級優勢

在Xilinx FPGA上快速實現JESD204B

JESD204 v5.2約束使用生成的dcp構建邏輯計時失敗

JESD204接口簡介

串行LVDS和JESD204B的對比

JESD204標準解析

FPGA高速數據采集設計之JESD204B接口應用場景

AD9683的引腳如何與zynq 7015芯片中的JESD204 ip核端口對應相連?

在Xilinx FPGA上快速實現 JESD204B

采用JESD204標準的高速串行接口的應用

JESD204——它是什么?

技術文章|高速DAC JESD204接口接收機物理層壓力測試(上)

技術文章|高速DAC JESD204接口接收機物理層壓力測試(上)

評論