AD9574以太網時鐘發生器:設計指南與應用解析

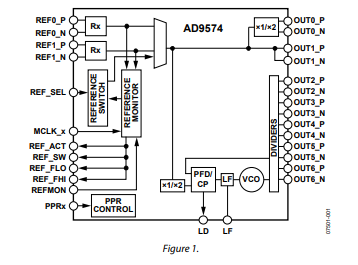

在當今高速發展的電子領域,以太網和千兆以太網技術的應用日益廣泛,對于高性能時鐘發生器的需求也愈發迫切。AD9574作為一款專為以太網和千兆以太網線卡應用優化的多輸出時鐘發生器,憑借其卓越的性能和豐富的功能,成為眾多電子工程師的理想選擇。本文將深入解析AD9574的特性、工作原理、配置方法以及應用場景,為電子工程師在實際設計中提供全面的參考。

文件下載:AD9574.pdf

特性亮點

冗余輸入與監控功能

AD9574具備冗余輸入參考時鐘能力和參考監控功能,這為系統的穩定性和可靠性提供了有力保障。在實際應用中,當一個參考時鐘出現故障時,系統可以迅速切換到另一個備用時鐘,確保系統的正常運行。同時,參考監控功能可以實時監測參考時鐘的頻率和相位,及時發現潛在的問題并進行處理。

低抖動與寬頻率范圍

該時鐘發生器在低抖動性能方面表現出色,例如在156.25 MHz時,10 kHz至10 MHz的均方根抖動僅為0.234 ps,12 kHz至20 MHz的均方根抖動為0.243 ps。這種低抖動特性對于高速數據傳輸和高精度信號處理至關重要,可以有效減少信號失真和誤碼率。此外,AD9574支持19.44 MHz或25 MHz的輸入頻率,并能通過預設的頻率轉換功能提供多種輸出頻率,滿足不同應用的需求。

集成化設計與靈活配置

AD9574采用了完全集成的VCO/PLL核心和集成式環路濾波器,僅需一個外部電容即可完成環路濾波,大大減少了外部元件的數量,降低了設計復雜度和成本。同時,通過PPRx引腳進行設備配置,用戶可以根據具體需求靈活選擇不同的頻率轉換、時鐘輸出功能和輸入參考功能,實現個性化的設計。

多種輸出驅動格式

該時鐘發生器支持HSTL、LVDS、HCSL以及1.8 V和3.3 V CMOS等多種輸出驅動格式,能夠與不同類型的電路和設備進行良好的匹配,提高了系統的兼容性和靈活性。

工作原理

AD9574的工作原理基于其內部的PLL(鎖相環)結構,主要由頻率預分頻器、PFD(鑒相器)、電荷泵、環路濾波器、VCO(壓控振蕩器)和反饋分頻器等六個功能單元組成。

頻率預分頻器

頻率預分頻器通過×2頻率乘法器、÷5分頻器和多路復用器實現不同的頻率分頻比,根據PPRx引腳的設置,可提供1/2、1、5/2或5的分頻值,為后續的PLL處理提供合適的輸入頻率。

PLL核心處理

PFD、電荷泵和環路濾波器協同工作,根據輸入時鐘和反饋時鐘的相位差來調整VCO的輸出頻率。環路濾波器采用部分集成的三階RC網絡,外部通過連接電容或電容與電阻的串聯網絡來調整PLL的帶寬,以確保VCO輸出頻率穩定在N倍的PFD輸入頻率(N為反饋分頻器的值)。

輸出時鐘生成

VCO輸出的頻率經過反饋分頻器和輸出分頻器的處理后,生成所需的輸出時鐘信號。OUT0和OUT1通道可提供參考頻率的副本,OUT0還具備頻率加倍選項;OUT2至OUT6通道則通過集成的整數-N PLL實現不同的頻率轉換,為系統提供多樣化的時鐘信號。

PPRx引腳配置

AD9574通過七個PPRx引腳進行設備配置,每個引腳控制特定的功能或功能塊。通過連接不同阻值的上拉或下拉電阻到PPRx引腳,并根據電阻的阻值和連接方向確定引腳的狀態(共8種狀態),實現對設備的各種功能配置。

PPR0 - 參考時鐘輸入配置

PPR0引腳控制參考時鐘輸入(REF0_x和REF1_x)的配置,可選擇單端3.3 V CMOS緩沖模式或差分模式。在單端模式下,可直接連接3.3 V時鐘源到正參考輸入引腳,同時將負輸入引腳通過0.1 nF電容接地;在差分模式下,需將差分時鐘驅動器通過0.1 nF電容交流耦合到兩個參考輸入引腳,也支持單端1.8 V CMOS時鐘源連接。

PPR1 - 頻率轉換設置

PPR1引腳允許用戶從預定義的頻率轉換組中選擇,確定OUT4和OUT5通道的輸出頻率,同時也影響OUT2和OUT3通道的頻率。每個PPR1狀態對應一組輸出頻率,具體的頻率值和PLL的設置(如×2倍增器狀態和PLL帶寬)在數據表中詳細給出。

PPR2 - OUT0和OUT1配置

PPR2引腳用于配置OUT0和OUT1通道的輸出驅動類型和頻率縮放因子,可選擇HSTL或3.3 V CMOS驅動,輸出頻率可以是參考頻率的1倍或2倍。

PPR3 - OUT4和OUT5配置

PPR3引腳根據PPR1確定的頻率對,選擇OUT4和OUT5通道的具體輸出頻率和輸出驅動類型,提供了多種組合選項。

PPR4 - OUT6配置

PPR4引腳用于配置OUT6通道的輸出頻率和驅動類型,但該通道的配置與PPR1狀態相關,在PPR1狀態2至7時,OUT6通道將被禁用。

PPR5 - 參考監控閾值

PPR5引腳控制參考頻率監控的誤差閾值,以ppm(百萬分之一)為單位,可設置為±25、±10、±50或±100 ppm,用于實時監測參考時鐘的頻率準確性。

PPR6 - 監控時鐘(MCLK_x)輸入配置

PPR6引腳控制MCLK_x輸入的配置,包括輸入頻率和輸入類型(單端3.3 V CMOS或差分),可選擇0.008 MHz、10 MHz、19.44 MHz、25 MHz或38.88 MHz的固定頻率輸入。

應用場景與設計要點

雙振蕩器參考輸入應用

在雙振蕩器參考輸入應用中,使用兩個晶體振蕩器作為參考輸入,同時提供一個穩定的振蕩器源作為MCLK_x輸入,用于參考監控功能。通過FPGA進行控制接口的管理,實現對參考狀態和PLL鎖定狀態的監測,并根據需要進行參考切換。在設計時,需根據實際需求選擇合適的PPRx狀態,通過連接相應的編程電阻來實現。

單振蕩器參考輸入應用

對于簡單的單振蕩器參考輸入應用,使用一個晶體振蕩器作為參考輸入,參考監控功能相對簡化。通過將REF_FHI和REF_FLO引腳進行線或連接,并將REF_MON接地,可實現參考存在檢測功能。同樣,通過設置PPRx狀態來配置AD9574的工作模式。

時鐘輸出接口設計

在與不同類型的時鐘輸出接口進行連接時,需要注意以下幾點:

- CMOS時鐘輸出:盡量設計點對點網絡,使驅動器只有一個接收器,以簡化終端方案并減少阻抗不匹配引起的振鈴。通常需要在源端進行串聯終端匹配,串聯電阻值根據板設計和時序要求而定,一般在10 Ω至100 Ω之間。同時,為了保證信號的上升/下降時間和信號完整性,建議CMOS輸出的走線長度小于6英寸。

- LVDS和HSTL時鐘輸出:LVDS和HSTL采用差分輸出驅動器,推薦使用圖中所示的終端電路進行匹配,以確保信號的穩定傳輸。

- HCSL時鐘輸出:HCSL采用差分開漏架構,需要使用外部終端電阻。在某些情況下,為了減少過沖和振鈴,可在傳輸線路中串聯一個10 Ω至30 Ω的小電阻。

電源與熱設計

AD9574需要3.3 V ± 10%的電源供應,在PCB設計中,應遵循良好的工程實踐,合理布局電源走線和接地平面。在電源引腳附近使用足夠的旁路電容(如0.1 μF),并在PCB上對電源進行充分的去耦(>10 μF)。此外,AD9574封裝的外露金屬焊盤需要正確接地,以提供良好的散熱路徑。根據熱性能參數表,可以計算在不同氣流條件下的結溫,必要時可使用氣流源來確保結溫不超過規定值。

總結

AD9574以其高性能、高集成度和靈活的配置能力,為以太網和千兆以太網應用提供了可靠的時鐘解決方案。電子工程師在設計過程中,需要深入理解其工作原理和配置方法,根據具體的應用場景和需求,合理選擇PPRx狀態,優化時鐘輸出接口設計,并注意電源和熱設計,以確保系統的穩定運行和高性能表現。希望本文能為電子工程師在使用AD9574進行設計時提供有益的參考和指導。你在實際應用中是否遇到過類似時鐘發生器的配置難題?你是如何解決的呢?歡迎在評論區分享你的經驗和見解。

-

設計應用

+關注

關注

0文章

176瀏覽量

5249 -

ad9574

+關注

關注

0文章

5瀏覽量

4097

發布評論請先 登錄

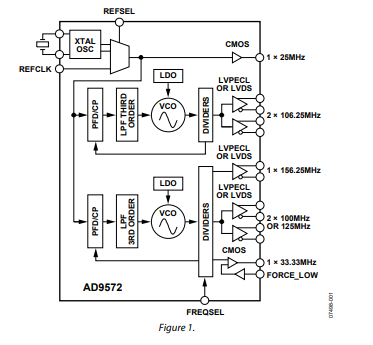

AD9572:高性能光纖通道/以太網時鐘發生器IC的深度解析

解析AD9571:以太網時鐘發生器的卓越之選

AD9524:高性能時鐘發生器的深度剖析與應用指南

AD9520-3:高性能時鐘發生器的深度解析與應用指南

AD9520-4:高性能時鐘發生器的深度解析與應用指南

AD9518-2:6輸出時鐘發生器的詳細解析與應用指南

AD9517-1:高性能12輸出時鐘發生器的深度解析

AD9520-0:高性能時鐘發生器的深度解析與應用指南

深入解析 CDC421Axxx:高性能低抖動時鐘發生器

深入解析 CDC421Axxx:高性能低抖動時鐘發生器

LMK03806:超低抖動時鐘發生器的技術解析與應用指南

探索時鐘發生器的競爭優勢

LMK5B33414EVM網絡時鐘發生器評估模塊技術解析

AD9572光纖通道/以太網時鐘發生器IC,PLL內核,分頻器,7路時鐘輸出技術手冊

AD9574以太網 千兆以太網時鐘發生器技術手冊

AD9574以太網時鐘發生器:設計指南與應用解析

AD9574以太網時鐘發生器:設計指南與應用解析

評論