AD9520-0:高性能時鐘發生器的深度解析與應用指南

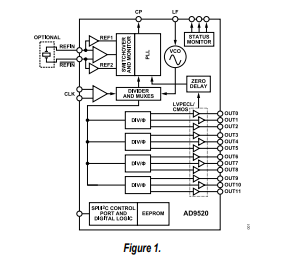

在電子設計領域,時鐘發生器是確保系統穩定運行的關鍵組件。AD9520-0作為一款12 LVPECL/24 CMOS輸出的時鐘發生器,集成了2.8 GHz VCO,以其卓越的性能和豐富的功能,在眾多應用場景中展現出強大的優勢。本文將深入剖析AD9520-0的特性、工作原理以及應用要點,為電子工程師們提供全面的設計參考。

文件下載:AD9520-0.pdf

一、AD9520-0的特性亮點

1. 低相位噪聲與PLL

AD9520-0具備低相位噪聲的鎖相環(PLL),這對于需要高精度時鐘信號的應用至關重要。低相位噪聲能夠有效減少信號的抖動和干擾,提高系統的穩定性和可靠性。

2. 靈活的VCO配置

片上VCO的頻率范圍為2.53 GHz至2.95 GHz,同時還支持外部3.3 V/5 V VCO/VCXO,最高可達2.4 GHz。這種靈活的配置方式使得AD9520-0能夠適應不同的應用需求,為設計提供了更多的選擇。

3. 多樣的參考輸入

支持1個差分或2個單端參考輸入,可接受CMOS、LVDS或LVPECL參考信號,頻率最高可達250 MHz。此外,還能接受16.62 MHz至33.3 MHz的晶體作為參考輸入,并具備可選的參考時鐘倍頻器和參考監測功能。

4. 豐富的輸出配置

擁有12個1.6 GHz LVPECL輸出,分為4組,每組3個輸出共享一個1至32的分頻器,并可設置相位延遲。每個LVPECL輸出還可配置為2個CMOS輸出(頻率 ≤250 MHz),且所有輸出在上電時可自動同步,也支持手動同步。

5. 便捷的控制接口

提供SPI和I2C兼容的串行控制端口,方便與微控制器或其他設備進行通信。同時,片內的非易失性EEPROM可存儲配置設置,確保系統在重啟后能夠快速恢復到之前的工作狀態。

二、工作原理詳解

1. 鎖相環(PLL)

AD9520-0的PLL是其核心組成部分,它可以利用片上VCO或外部VCO/VCXO創建完整的鎖相環。PLL需要一個外部環路濾波器來設置環路帶寬和穩定性,其配置參數包括R分頻器、N分頻器、PFD極性、抗反沖脈沖寬度、電荷泵電流等,這些參數可通過可編程寄存器進行設置。

2. 參考輸入與切換

PLL的參考輸入電路非常靈活,支持差分輸入、單端輸入和晶體振蕩器輸入。在雙單端參考模式下,AD9520-0支持自動和手動的PLL參考時鐘切換,確保系統在不同參考信號之間能夠平穩切換。

3. 時鐘分配

時鐘分配部分由四個時鐘通道組成,每個通道有自己的可編程分頻器,可將輸入的時鐘頻率進行分頻。VCO分頻器可將VCO輸出進行1至6的分頻,以滿足不同的頻率需求。通道分頻器還支持可選的占空比校正和相位偏移設置,進一步提高時鐘信號的質量。

4. 零延遲操作

AD9520-0具備內部和外部零延遲模式,可將輸出時鐘的相位與外部PLL參考輸入的相位對齊。在內部零延遲模式下,通道分頻器0的輸出反饋到PLL的N分頻器;在外部零延遲模式下,一個輸出時鐘反饋到CLK輸入,最終反饋到PLL的N分頻器。

三、應用場景分析

1. 低抖動時鐘分配

在需要低抖動、低相位噪聲時鐘分配的應用中,AD9520-0能夠提供高質量的時鐘信號,確保系統的穩定性和性能。例如,在通信系統、數據中心等領域,精確的時鐘分配對于數據傳輸和處理至關重要。

2. 時鐘生成與轉換

適用于SONET、10Ge、10GFC、同步以太網、OTU2/3/4等通信標準的時鐘生成和轉換。其靈活的配置和高性能的PLL能夠滿足不同標準對時鐘信號的要求。

3. 高速ADC、DAC等設備的時鐘驅動

高速ADC和DAC對采樣時鐘的質量要求極高,AD9520-0的低抖動特性能夠有效提高這些設備的性能,減少噪聲和失真。

4. 高性能無線收發器

在無線通信領域,AD9520-0可為無線收發器提供穩定的時鐘信號,確保信號的準確傳輸和接收。

5. 測試與測量設備

ATE和高性能儀器需要高精度的時鐘信號來保證測量的準確性,AD9520-0的高性能特性使其成為這些設備的理想選擇。

四、設計要點與注意事項

1. 電源供應

AD9520-0的電源供應需要特別注意,VS和VS_DRV的電壓范圍應嚴格按照規格要求設置,同時要確保電源的穩定性和低噪聲。

2. 環路濾波器設計

PLL的環路濾波器對系統的性能影響很大,需要根據具體的應用需求進行合理設計。可以使用ADIsimCLK等工具來輔助設計,確保環路的穩定性和帶寬。

3. 參考輸入選擇

在選擇參考輸入時,要根據實際情況選擇合適的輸入方式和頻率。同時,要注意輸入信號的幅度、頻率范圍和偏置電壓等參數,以確保PLL能夠正常工作。

4. 輸出配置與匹配

在配置輸出時,要根據負載的需求選擇合適的輸出類型(LVPECL或CMOS)和電平。同時,要注意輸出的匹配和端接,以減少信號反射和干擾。

5. EEPROM操作

EEPROM可用于存儲配置設置,但在操作時要注意確保數據的正確寫入和讀取。在寫入EEPROM之前,要先對AD9520-0的寄存器進行配置,并確保VCO校準位設置正確。

五、總結

AD9520-0作為一款高性能的時鐘發生器,以其豐富的功能和卓越的性能,為電子工程師們提供了一個強大的設計工具。在實際應用中,工程師們需要根據具體的需求,合理配置AD9520-0的參數,確保系統的穩定性和性能。同時,要注意電源供應、環路濾波器設計、參考輸入選擇等方面的問題,以充分發揮AD9520-0的優勢。希望本文能夠為電子工程師們在使用AD9520-0進行設計時提供有益的參考。

-

時鐘發生器

+關注

關注

1文章

349瀏覽量

70106 -

應用指南

+關注

關注

0文章

108瀏覽量

6128

發布評論請先 登錄

AD9576:高性能雙PLL異步時鐘發生器的深度解析

AD9524:高性能時鐘發生器的深度剖析與應用指南

AD9522-1:高性能時鐘發生器的深度剖析與應用指南

AD9518-1:高性能時鐘發生器的深度剖析與應用指南

AD9517-1:高性能12輸出時鐘發生器的深度解析

AD9517-0:高性能多輸出時鐘發生器的全面解析

AD9520 - 2:高性能時鐘發生器的深度剖析

AD9520-1:高性能時鐘發生器的全方位解析

TI CDC421Axxx:高性能低抖動時鐘發生器的深度解析

CDCE421A:高性能低相位噪聲時鐘發生器的深度解析

AD9520-0 12 LVPECL/24 CMOS輸出時鐘發生器技術手冊

AD9520-0:高性能時鐘發生器的深度解析與應用指南

AD9520-0:高性能時鐘發生器的深度解析與應用指南

評論