解析AD9571:以太網時鐘發生器的卓越之選

在高速通信和數據處理的當今時代,時鐘發生器對于確保系統的穩定運行和精確同步至關重要。今天,我們將深入探討Analog Devices的AD9571以太網時鐘發生器,它在低抖動、高性能時鐘生成方面表現出色,為以太網應用提供了理想的解決方案。

文件下載:AD9571.pdf

一、AD9571的關鍵特性

1. 低抖動性能

AD9571具備出色的低抖動特性,在不同頻率下表現優異。例如,在156.25 MHz時,從1.875 MHz到20 MHz的均方根抖動僅為0.17 ps;在125 MHz時,從12 kHz到20 MHz的均方根抖動為0.41 ps。這種低抖動性能對于需要高精度時鐘信號的應用,如以太網線卡、交換機和路由器等,至關重要。它能有效減少信號傳輸中的誤差,提高系統的穩定性和可靠性。

2. 多輸出功能

該時鐘發生器提供10個時鐘輸出,包括6個25 MHz的CMOS輸出、1個156.25 MHz的LVPECL/LVDS輸出、2個100 MHz或125 MHz的LVPECL/LVDS輸出以及1個33.33 MHz的CMOS輸出。這種多輸出配置可以滿足不同設備對時鐘信號的需求,為系統設計提供了更大的靈活性。

3. 集成度高

AD9571集成了VCO/PLL核心、環路濾波器等關鍵組件,無需外部環路濾波器組件,節省了設計時間和電路板空間。同時,它還具備預設的分頻比,可方便地配置為156.25 MHz、33.33 MHz、100 MHz和125 MHz等常用頻率。

4. 低功耗設計

在LVDS操作模式下,功耗僅為0.48 W;在LVPECL操作模式下,功耗為0.69 W。低功耗設計不僅降低了系統的散熱需求,還延長了設備的使用壽命,尤其適用于對功耗敏感的應用場景。

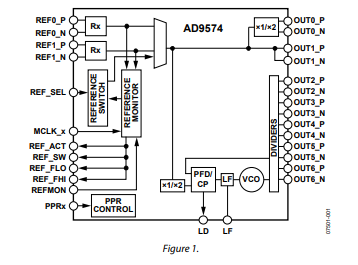

二、工作原理與結構

1. PLL核心

AD9571的PLL部分由低噪聲相位頻率檢測器(PFD)、精密電荷泵(CP)、低相位噪聲電壓控制振蕩器(VCO)以及預編程的反饋分頻器和輸出分頻器組成。通過將外部晶體或參考時鐘連接到REFCLK引腳,可將高達156.25 MHz的頻率鎖定到輸入參考。

2. 輸出配置

用戶可以通過FREQSEL引腳選擇100 MHz或125 MHz的輸出頻率。同時,FORCE_LOW引腳可將33.33 MHz輸出強制置為低電平,以減少對其他輸出的干擾。

3. 電源與接地

AD9571需要3.3 V ± 10%的電源供應,在PCB布局時,應遵循良好的工程實踐,對電源走線和接地平面進行合理設計。使用足夠的電容對電源進行旁路,確保電源的穩定性。此外,芯片封裝上的外露金屬焊盤不僅是電氣連接,還具有散熱增強功能,必須正確連接到地。

三、應用領域

1. 以太網應用

AD9571專為以太網線卡應用而優化,可用于以太網交換機、路由器等設備,為其提供低抖動、低相位噪聲的時鐘信號,確保數據的準確傳輸和交換。

2. 存儲與接口應用

在SCSI、SATA和PCI - express等存儲和接口應用中,AD9571的高性能時鐘輸出可以滿足這些接口對時鐘精度的要求,提高數據傳輸的可靠性。

3. 其他對相位噪聲和抖動要求苛刻的應用

對于一些對相位噪聲和抖動要求極高的應用,如高速數據采集、通信基站等,AD9571同樣能夠提供穩定可靠的時鐘信號。

四、性能指標分析

1. 相位噪聲

在不同輸出頻率下,AD9571的相位噪聲表現出色。例如,在156.25 MHz的LVDS輸出中,在1 kHz時的相位噪聲為 - 120 dBc/Hz,在10 MHz時為 - 151 dBc/Hz。低相位噪聲有助于減少信號干擾,提高系統的抗干擾能力。

2. 抖動性能

不同輸出類型(LVDS、LVPECL、CMOS)在不同帶寬下的抖動指標均符合要求。如LVDS輸出在12 kHz到20 MHz帶寬下,156.25 MHz輸出的均方根抖動為0.41 ps,這保證了時鐘信號的穩定性和準確性。

五、設計注意事項

1. 參考輸入

默認情況下,晶體振蕩器啟用并作為參考源,需要連接外部25 MHz晶體。當REFSEL引腳接地時,晶體振蕩器關閉,REFCLK引腳需提供高質量的25 MHz參考時鐘。

2. 時鐘分配

在進行CMOS時鐘分配時,應盡量采用點對點網絡,減少信號反射和干擾。對于LVPECL和LVDS輸出,需要進行適當的終端匹配,以確保信號的完整性。

3. 電源旁路

在PCB設計中,要對電源進行充分的旁路,使用足夠的電容來濾除電源噪聲。同時,要注意芯片各電源引腳的旁路電容的位置和值的選擇。

六、總結

AD9571作為一款高性能的以太網時鐘發生器,憑借其低抖動、多輸出、高集成度和低功耗等特性,在以太網及其他相關應用領域具有廣泛的應用前景。電子工程師在設計相關系統時,可以充分利用AD9571的優勢,提高系統的性能和可靠性。在實際應用中,還需要根據具體需求,合理配置輸出頻率、選擇合適的輸出類型,并注意PCB設計中的各種細節,以確保AD9571能夠發揮最佳性能。你在使用時鐘發生器的過程中,遇到過哪些挑戰呢?歡迎在評論區分享你的經驗。

-

低抖動

+關注

關注

0文章

73瀏覽量

6097 -

ad9571

+關注

關注

1文章

4瀏覽量

3892

發布評論請先 登錄

AD9574以太網時鐘發生器:設計指南與應用解析

深入解析AD9573:PCI - Express時鐘發生器IC的卓越之選

AD9572:高性能光纖通道/以太網時鐘發生器IC的深度解析

深入解析AD9516-3:多輸出時鐘發生器的卓越之選

德州儀器CDCR83A:Direct Rambus時鐘發生器的卓越之選

深度解析CDCM61001:高性能低抖動時鐘發生器的卓越之選

深入解析CDCM61002:高性能時鐘發生器的卓越之選

探索 CDC421Axxx:高性能低抖動時鐘發生器的卓越之選

探索CDC421Axxx:高性能時鐘發生器的卓越之選

深度剖析CDCE62002:高性能時鐘發生器的卓越之選

CDCM9102:低噪聲時鐘發生器的卓越之選

深入解析LMK03318:超高性能時鐘發生器的卓越之選

AD9574以太網 千兆以太網時鐘發生器技術手冊

解析AD9571:以太網時鐘發生器的卓越之選

解析AD9571:以太網時鐘發生器的卓越之選

評論