AD9543:高性能時鐘同步與抖動清理芯片解析

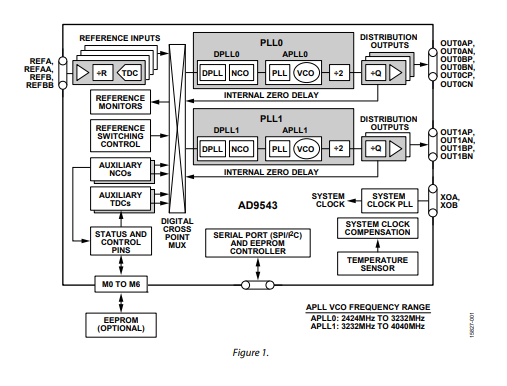

在當今的電子系統中,時鐘信號的穩定性和準確性至關重要。AD9543作為一款四輸入、十輸出的雙DPLL/IEEE 1588同步器和抖動清理器,為電子工程師們提供了強大的時鐘解決方案。本文將深入剖析AD9543的特性、應用及相關技術細節,幫助工程師們更好地理解和應用這款芯片。

文件下載:AD9543.pdf

一、AD9543特性概覽

1. 雙DPLL同步能力

AD9543的雙DPLL能夠同步2 kHz至750 MHz的物理層時鐘,不僅實現了頻率轉換,還能對噪聲參考進行抖動清理。它符合ITU - T G.8262和Telcordia GR - 253等標準,同時支持Telcordia GR - 1244、ITU - T G.812、G.813等一系列標準,為系統的穩定性和兼容性提供了有力保障。

2. 頻率監測與參考驗證

芯片具備連續頻率監測和參考驗證功能,能夠檢測低至50 ppb的頻率偏差。這使得系統能夠及時發現參考時鐘的異常,確保時鐘信號的準確性。

3. 可編程功能

- 數字環路濾波器帶寬:可編程數字環路濾波器帶寬低至(10^{-4} Hz),為工程師提供了靈活的設計空間,以滿足不同應用場景的需求。

- 輔助NCO:兩個獨立的可編程輔助NCO(1 Hz至(<1.4 ×10^{-12} Hz)),適用于IEEE 1588 Version 2伺服反饋,在PTP應用中表現出色。

4. 自動與手動操作

支持自動和手動保持模式以及參考切換,能夠實現零延遲、無中斷或相位建立操作。同時,還提供可編程的基于優先級的參考切換,支持手動、自動恢復和自動非恢復模式。

5. 豐富的輸入輸出接口

- 輸出:擁有5對時鐘輸出引腳,每對可作為差分LVDS/HCSL/CML或2個單端輸出,輸出頻率范圍為1 Hz至500 MHz。

- 輸入:提供2個差分或4個單端輸入參考,并且具備交叉點復用器,可將參考輸入連接到PLL。

二、AD9543的應用領域

1. PTP和SyncE應用

在PTP(IEEE 1588)和SyncE應用中,AD9543能夠進行抖動清理和同步,確保時鐘信號的準確性和穩定性,滿足高精度時間同步的需求。

2. 光傳輸網絡

在光傳輸網絡(OTN)、SDH以及宏基站和小基站中,AD9543可用于OTN映射/解映射并進行抖動清理,為網絡的穩定運行提供支持。

3. 其他應用

還可用于小基站時鐘、Stratum 2、Stratum 3e和Stratum 3保持、抖動清理和相位瞬態控制,以及JESD204B支持的ADC和DAC時鐘等領域。

三、技術細節剖析

1. 系統時鐘PLL

系統時鐘PLL由整數 - N頻率合成器、集成環路濾波器和壓控振蕩器(VCO)組成。VCO輸出的系統時鐘頻率范圍為2250 MHz至2415 MHz。用戶需要聲明系統時鐘PLL的輸入參考頻率,可通過編程SYSCLK參考頻率位字段來實現。系統時鐘源可選擇晶體路徑或直接路徑,路徑選擇通過使能維持放大器位進行。此外,系統時鐘PLL還提供2×頻率倍增器選項,可降低PLL帶內噪聲,但要求參考輸入信號的占空比接近50%。

2. 數字PLL(DPLL)

DPLL是一種全數字鎖相環,使用數控振蕩器(NCO)代替傳統的VCO。AD9543的DPLL具有數字TDC基相位檢測器和可編程帶寬的數字環路濾波器,輸出數字頻率調諧字(FTW)以產生相應的NCO輸出頻率。DPLL有多種操作模式,包括自由運行、保持和活動模式,通過環路控制器確保模式之間的無縫過渡。

3. 鎖相檢測器

- DPLL相位鎖相檢測器:每個DPLL通道都有一個全數字相位鎖相檢測器,用戶可通過源配置文件控制其閾值靈敏度和滯后。相位鎖相檢測器提供兩個狀態位,分別表示DPLL從非鎖相到鎖相和從鎖相到非鎖相的狀態變化。

- DPLL頻率鎖相檢測器:其操作與相位鎖相檢測器類似,但基于參考信號和反饋信號的周期偏差進行判斷,不受相位斜率限制器狀態的影響。

4. 相位步長檢測器

相位步長檢測器用于監測DPLL相位檢測器輸出的相位瞬變,可通過編程Profile x相位步長閾值位字段來激活。當檢測到相位瞬變超過規定值時,根據使能步長檢測參考故障位的狀態,DPLL會啟動新的采集序列或重置參考監視器。

5. 偏移調整

偏移調整功能允許用戶為參考輸入關聯一個固定的相位偏移,適用于具有冗余全球導航衛星系統(GNSS)/全球定位系統(GPS)參考源的應用。通過編程Profile x相位偏移位字段來激活該功能。

6. EEPROM使用

AD9543支持外部I2C兼容的EEPROM,可實現自動或手動下載和上傳配置。EEPROM控制器負責與EEPROM的通信,在下載和上傳過程中會進行校驗和計算,以確保數據的準確性。同時,還支持多設備共享一個EEPROM,通過總線仲裁機制解決沖突。

7. 串行控制端口

AD9543的串行控制端口支持SPI和I2C協議,用戶可通過M4多功能引腳在啟動時選擇使用的協議。SPI端口支持3線和4線硬件配置,以及MSB先和LSB先的數據格式。I2C端口支持400 kHz快速模式和100 kHz標準模式,采用直接16位內存尋址。

四、總結與思考

AD9543以其強大的功能和豐富的特性,為電子工程師們提供了一個可靠的時鐘解決方案。在實際應用中,工程師們需要根據具體的需求和場景,合理配置芯片的各項參數,以充分發揮其性能。同時,對于一些關鍵參數的選擇,如鎖相檢測器的閾值、偏移調整值等,需要結合實際的信號特性和系統要求進行優化。大家在使用AD9543的過程中,是否遇到過一些特殊的問題或挑戰呢?又是如何解決的呢?歡迎在評論區分享你的經驗和見解。

-

時鐘同步

+關注

關注

0文章

137瀏覽量

13591

發布評論請先 登錄

LMK04000 系列時鐘抖動清理器:高精度時鐘解決方案深度剖析

解析LMK04000系列時鐘抖動清理器:特性、應用與設計要點

LMK04100 系列時鐘抖動清理器:特性、應用與設計指南

深入剖析 LMK04100 系列時鐘抖動清理器:性能、應用與設計要點

LMK0482x系列時鐘抖動清除器:高性能時鐘解決方案解析

深度解析LMK04616:超低噪聲時鐘抖動清理器的卓越之選

Texas Instruments LMK04368-EP:超低噪聲時鐘抖動清理器的深度解析

AD9543四通道輸入、10路輸出、雙通道DPLL/IEEE 1588同步器和抖動清除器技術手冊

AD9543:高性能時鐘同步與抖動清理芯片解析

AD9543:高性能時鐘同步與抖動清理芯片解析

評論