AD9517-3:高性能時鐘發生器,滿足多樣設計需求

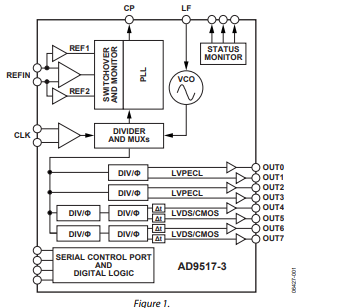

在當今的電子設計領域,時鐘發生器對于各類電子系統的穩定運行起著至關重要的作用。AD9517-3作為一款功能強大的12輸出時鐘發生器,集成了2.0 GHz VCO,為電子工程師們提供了出色的時鐘解決方案。接下來,我們將深入探討AD9517-3的特性、應用、工作原理以及相關設計要點。

文件下載:AD9517-3.pdf

一、產品特性

1. 低相位噪聲與出色的抖動性能

AD9517-3具有低相位噪聲的特點,其內部PLL和VCO的設計使得它能夠提供亞皮秒級的抖動性能。內部VCO的頻率范圍為1.75 GHz至2.25 GHz,并且還可以選擇使用高達2.4 GHz的外部VCO/VCXO,為不同的應用場景提供了靈活的選擇。

2. 豐富的輸入輸出接口

- 輸入方面:它擁有1個差分或2個單端參考輸入,支持LVPECL、LVDS或CMOS參考信號,輸入頻率可達250 MHz,還具備參考監測能力,以及自動恢復和手動參考切換/保持模式,大大增強了系統的可靠性和靈活性。

- 輸出方面:提供了4對LVPECL輸出(最高可達1.6 GHz)和4對LVDS輸出(最高可達800 MHz),每對LVDS輸出還可重新配置為兩個250 MHz的CMOS輸出。此外,輸出還具有可調節的延遲和相位,能夠滿足不同系統對時鐘信號的精確要求。

3. 其他特性

- 具有數字或模擬鎖檢測功能,可根據需求進行選擇。

- 所有輸出在加電時可自動同步,也支持手動輸出同步。

- 采用48引腳LFCSP封裝,便于在電路板上進行布局和安裝。

二、應用領域

1. 通信網絡

在10/40/100 Gb/sec的網絡線卡中,如SONET、同步以太網、OTU2/3/4等,AD9517-3能夠提供低抖動、低相位噪聲的時鐘信號,確保數據傳輸的準確性和穩定性。

2. 數據轉換

在高速ADC、DAC、DDS、DDC、DUC、MxFEs等數據轉換設備中,它可以為這些設備提供高質量的時鐘信號,提高數據轉換的性能。

3. 無線通信

在高性能無線收發器中,AD9517-3能夠滿足對時鐘信號的嚴格要求,保證無線通信的穩定性和可靠性。

4. 測試與測量

在ATE和高性能儀器中,它可以提供精確的時鐘信號,滿足測試和測量的高精度需求。

三、工作原理

1. PLL工作原理

AD9517-3內部集成了PLL和VCO,PLL通過比較參考信號和VCO輸出信號的相位和頻率,控制電荷泵調整VCO的頻率,從而實現鎖相。PLL的配置非常靈活,可以通過可編程寄存器設置R分頻器、N分頻器、PFD極性、反沖脈沖寬度、電荷泵電流等參數,以適應不同的應用需求。

2. 時鐘分配原理

時鐘分配部分通過通道分頻器對時鐘信號進行分頻和延遲調整。LVPECL和LVDS/CMOS輸出通道都有各自的可編程分頻器,可以實現不同的分頻比和相位延遲。此外,還可以通過設置粗相位延遲和精細延遲調整,進一步優化時鐘信號的相位和延遲。

四、設計要點

1. 電源設計

- 電源電壓:AD9517-3需要3.3 V的主電源(VS),LVPECL電源(VS_LVPECL)的范圍為2.5 V至3.3 V,電荷泵電源(VCP)的范圍為3.3 V至5.0 V。在設計電源時,需要確保電源的穩定性和紋波符合要求。

- 電源濾波:為了減少電源噪聲對芯片的影響,需要在電源引腳附近添加合適的濾波電容。例如,在BYPASS引腳連接220 nF的電容,以確保內部LDO穩壓器的穩定性。

2. 參考輸入設計

- 輸入類型選擇:可以選擇差分或單端參考輸入,根據實際應用需求進行選擇。在選擇差分參考輸入時,需要注意輸入信號的自偏置和交流耦合。

- 輸入匹配:為了確保參考信號的準確傳輸,需要進行輸入匹配,避免信號反射和干擾。

3. 輸出設計

- 輸出負載匹配:對于LVPECL和LVDS輸出,需要進行合適的負載匹配,以確保輸出信號的質量。例如,LVPECL輸出需要進行直流終端匹配,LVDS輸出需要連接100 Ω的差分終端電阻。

- 輸出極性和延遲調整:可以根據實際需求調整輸出的極性和延遲,以滿足系統對時鐘信號的相位和延遲要求。

4. 寄存器配置

AD9517-3的功能通過寄存器進行配置,需要根據具體的應用需求設置相應的寄存器值。例如,設置PLL的參數、通道分頻器的分頻比和延遲、輸出的極性和功率等。在配置寄存器時,需要仔細閱讀數據手冊,確保寄存器的設置正確。

五、總結

AD9517-3作為一款高性能的時鐘發生器,具有低相位噪聲、豐富的輸入輸出接口、靈活的配置等優點,適用于多種應用領域。在設計過程中,需要注意電源設計、參考輸入設計、輸出設計和寄存器配置等要點,以確保芯片的性能和穩定性。通過合理的設計和配置,AD9517-3能夠為電子系統提供高質量的時鐘信號,滿足各種復雜的應用需求。

作為電子工程師,我們在使用AD9517-3時,要充分發揮其優勢,同時也要注意其設計要點,以實現最佳的系統性能。你在使用AD9517-3的過程中遇到過哪些問題呢?歡迎在評論區分享你的經驗和見解。

-

時鐘發生器

+關注

關注

1文章

349瀏覽量

70106 -

電子設計

+關注

關注

42文章

1974瀏覽量

49873

發布評論請先 登錄

AD9524:高性能時鐘發生器的深度剖析與應用指南

AD9522-5:高性能時鐘發生器的設計與應用

AD9522-3:高性能時鐘發生器的技術剖析與應用指南

AD9520-3:高性能時鐘發生器的深度解析與應用指南

AD9517-4:高性能多輸出時鐘發生器的深度解析

AD9517-1:高性能12輸出時鐘發生器的深度解析

AD9517-2:高性能12輸出時鐘發生器的設計與應用解析

AD9517-0:高性能多輸出時鐘發生器的全面解析

探索 CDC421Axxx:高性能低抖動時鐘發生器的卓越之選

深入解析 CDC421Axxx:高性能低抖動時鐘發生器

深入解析 CDC421Axxx:高性能低抖動時鐘發生器

深度剖析CDCE62002:高性能時鐘發生器的卓越之選

CDCE421A:高性能低相位噪聲時鐘發生器的深度解析

深入解析PLL1707-Q1:高性能多時鐘發生器的理想選擇

AD9517-3 12路輸出時鐘發生器,集成2.0GHz VCO技術手冊

AD9517-3:高性能時鐘發生器,滿足多樣設計需求

AD9517-3:高性能時鐘發生器,滿足多樣設計需求

評論