AD9518-0:高性能6輸出時鐘發生器的深度剖析

在電子設計領域,時鐘發生器的性能對于系統的穩定性和數據處理能力起著至關重要的作用。今天,我們將深入探討Analog Devices的AD9518-0 6輸出時鐘發生器,它以其低抖動、低相位噪聲等特性,成為眾多應用場景的理想選擇。

文件下載:AD9518-0.pdf

一、AD9518-0概述

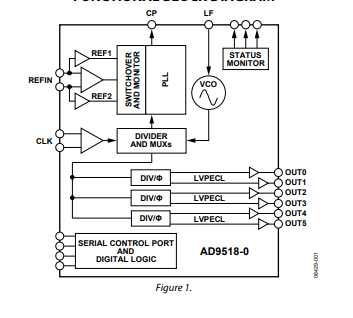

AD9518-0是一款具有亞皮秒抖動性能的多輸出時鐘分配器件,集成了片上PLL和VCO。其片上VCO的調諧范圍為2.55 GHz至2.95 GHz,同時也支持使用最高2.4 GHz的外部VCO/VCXO。該器件強調低抖動和相位噪聲,能夠最大程度地提升數據轉換器的性能,適用于對相位噪聲和抖動要求苛刻的各種應用。

1.1 主要特性

- 低相位噪聲PLL:有效降低信號干擾,保證時鐘信號的穩定性。

- 靈活的參考輸入:提供1個差分或2個單端參考輸入,支持LVPECL、LVDS或CMOS參考信號,頻率可達250 MHz,還具備參考監測和自動/手動參考切換/保持模式。

- 豐富的輸出配置:擁有3對1.6 GHz的LVPECL輸出,每對輸出共享一個1至32的分頻器,并可進行粗相位延遲設置。

- 低抖動性能:附加輸出抖動僅為225 fs rms,通道間的偏斜小于10 ps。

- 自動同步功能:在上電時可自動同步所有輸出,也支持手動輸出同步。

- 封裝形式:采用48引腳LFCSP封裝,便于電路板布局。

1.2 應用領域

- 低抖動時鐘分配:為系統提供穩定、低抖動的時鐘信號。

- 高速網絡線卡:如10/40/100 Gb/sec網絡線卡,包括SONET、同步以太網、OTU2/3/4等。

- 誤差校正:用于前向誤差校正(G.710)。

- 高速數據轉換:為高速ADC、DAC、DDS、DDC、DUC、MxFEs等提供時鐘。

- 無線通信:在高性能無線收發器中發揮重要作用。

- 測試與測量:適用于ATE和高性能儀器儀表。

二、工作原理與配置

2.1 鎖相環(PLL)

AD9518-0的PLL可與片上VCO或外部VCO/VCXO配合使用,需要一個外部環路濾波器來設置環路帶寬和穩定性。PLL的配置非常靈活,可通過可編程寄存器設置R分頻器、N分頻器、PFD極性、反沖脈沖寬度、電荷泵電流等參數,以適應不同的參考頻率、PFD比較頻率和VCO頻率。

2.2 參考輸入

該器件提供靈活的PLL參考輸入電路,支持差分輸入或兩個單端輸入。輸入頻率范圍為0至250 MHz,輸入信號可通過電容進行交流耦合。差分輸入的自偏置電平略有偏移,可防止輸入緩沖器在參考信號緩慢或缺失時產生抖動。單端輸入可由直流耦合的CMOS電平信號或交流耦合的正弦波/方波驅動,且可獨立關閉以提高隔離度和降低功耗。

2.3 時鐘分配

AD9518-0具有三個時鐘通道,每個通道有兩個LVPECL輸出,共六個輸出。每個通道都有一個可編程分頻器,可將輸入時鐘頻率進行2至32的整數分頻,也可旁路分頻器實現1分頻。此外,通道分頻器還支持選擇不同的占空比、進行占空比校正和設置粗相位偏移。

2.4 工作模式配置

- 高頻時鐘分配(CLK或外部VCO > 1600 MHz):默認配置下,PLL關閉,CLK/CLK輸入通過VCO分頻器連接到分配部分,允許最高2.4 GHz的外部輸入。

- 使用外部VCO:使能PLL后,可使用頻率低于2400 MHz的外部VCO或VCXO,此時內部VCO關閉。

- 內部VCO和時鐘分配:使用內部VCO時,必須使用VCO分頻器,以確保通道分頻器的輸入頻率不超過1600 MHz。同時,需要對VCO進行校準,以確保最佳性能。

- 時鐘分配(外部VCO < 1600 MHz):當外部時鐘源或外部VCO/VCXO頻率低于1600 MHz時,可繞過VCO分頻器。

三、寄存器配置與控制

AD9518-0通過串行控制端口進行寄存器配置,支持單字節或多字節傳輸,以及MSB先傳或LSB先傳的格式。寄存器配置涵蓋了PLL設置、時鐘分配、輸出控制等多個方面,具體如下:

3.1 串行控制端口

- 引腳功能:包括SCLK(串行時鐘)、SDIO(串行數據輸入/輸出)、SDO(串行數據輸出)和CS(芯片選擇)。

- 操作模式:支持讀寫操作,通過16位指令字指定數據傳輸類型、數據長度和起始寄存器地址。

- 數據傳輸:寫入數據時,需將數據先寫入串行控制端口緩沖區,然后通過設置Register 0x232[0] = 1b將緩沖區內容傳輸到實際控制寄存器。讀取數據時,可選擇讀取緩沖區或活動寄存器的數據。

3.2 控制寄存器

控制寄存器涵蓋了PLL、LVPECL輸出、VCO分頻器、時鐘輸入等多個方面的設置。例如,通過設置PLL相關寄存器可選擇參考輸入、設置R和N分頻器、調整PFD極性和電荷泵電流等;通過設置LVPECL輸出相關寄存器可控制輸出極性、差分電壓和電源狀態等。

四、性能指標與測試

4.1 電源要求

該器件的電源要求包括VS(3.3 V ± 5%)、VS_LVPECL(2.5 V至3.3 V ± 5%)和VCP(3.3 V至5.0 V ± 5%),同時需要連接適當的電阻和電容來設置內部偏置電流和電荷泵電流范圍。

4.2 時鐘輸入與輸出

- 時鐘輸入:CLK/CLK差分輸入頻率范圍為0至2.4 GHz,輸入靈敏度為150 mV p-p,支持交流耦合。

- 時鐘輸出:LVPECL輸出頻率最高可達2950 MHz,輸出差分電壓為550至980 mV,輸出上升/下降時間為70至180 ps,傳播延遲和輸出偏斜也有相應的指標。

4.3 相位噪聲與抖動

- 相位噪聲:內部VCO在不同頻率下的相位噪聲表現良好,如在2.95 GHz時,1 kHz偏移處的相位噪聲為 -47 dBc/Hz。

- 抖動:輸出絕對時間抖動在不同應用場景下有不同的表現,如在時鐘生成模式下,VCO = 2.95 GHz、LVPECL = 491.52 MHz、PLL LBW = 75 kHz時,積分帶寬為200 kHz至10 MHz的抖動為148 fs rms。

五、應用注意事項

5.1 熱性能

該器件采用48引腳LFCSP封裝,其熱阻在不同氣流條件下有所不同。可根據實際應用場景,通過相關公式計算結溫,以確保器件在合適的溫度范圍內工作。

5.2 ESD防護

AD9518-0是靜電放電(ESD)敏感器件,盡管具有專利或專有保護電路,但仍需采取適當的ESD防護措施,以避免性能下降或功能喪失。

5.3 時鐘分配與終端匹配

LVPECL輸出需要直流終端來偏置輸出晶體管,推薦使用LVPECL遠端Thevenin終端或Y終端。在實際應用中,需根據接收緩沖器的VS和VS_LVPECL電壓進行匹配,必要時可采用交流耦合。

六、總結

AD9518-0作為一款高性能的6輸出時鐘發生器,憑借其低抖動、低相位噪聲、靈活的配置和豐富的功能,在高速網絡、數據轉換、無線通信等領域具有廣泛的應用前景。電子工程師在設計過程中,可根據具體應用需求,合理配置寄存器,優化電路布局,以充分發揮該器件的性能優勢。同時,在使用過程中要注意熱性能、ESD防護和時鐘分配等方面的問題,確保系統的穩定性和可靠性。

你是否在實際項目中使用過類似的時鐘發生器?在使用過程中遇到過哪些問題?歡迎在評論區分享你的經驗和見解。

-

時鐘發生器

+關注

關注

1文章

349瀏覽量

70106 -

低抖動

+關注

關注

0文章

73瀏覽量

6097

發布評論請先 登錄

AD9524:高性能時鐘發生器的深度剖析與應用指南

AD9522-1:高性能時鐘發生器的深度剖析與應用指南

AD9522-2:高性能時鐘發生器的深度剖析

AD9518-3 6 輸出時鐘發生器深度解析:設計要點與應用洞察

AD9518-4:6輸出時鐘發生器的全面解析

AD9518-2:6輸出時鐘發生器的詳細解析與應用指南

AD9518-1:高性能時鐘發生器的深度剖析與應用指南

AD9517-1:高性能12輸出時鐘發生器的深度解析

深入剖析AD9516-0:一款高性能的14輸出時鐘發生器

AD9520 - 2:高性能時鐘發生器的深度剖析

AD9520-0:高性能時鐘發生器的深度解析與應用指南

CDCE62005:高性能時鐘發生器與分配器的深度剖析

深度剖析CDCE62002:高性能時鐘發生器的卓越之選

AD9518-0 6路輸出時鐘發生器,集成2.8GHz VCO技術手冊

AD9518-0:高性能6輸出時鐘發生器的深度剖析

AD9518-0:高性能6輸出時鐘發生器的深度剖析

評論