AD9510:高性能時鐘分配IC的深度剖析與應(yīng)用指南

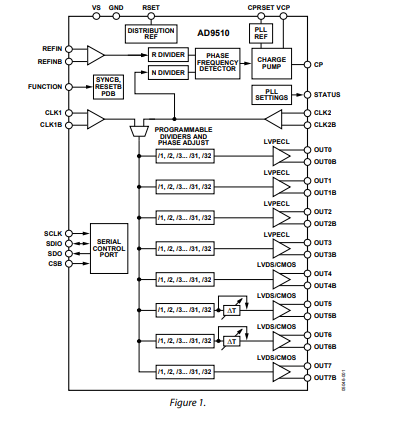

在電子設(shè)計領(lǐng)域,時鐘分配對于確保系統(tǒng)的穩(wěn)定性和高性能至關(guān)重要。AD9510作為一款1.2 GHz時鐘分配IC,憑借其低抖動、低相位噪聲等特性,在眾多應(yīng)用場景中展現(xiàn)出卓越的性能。本文將深入探討AD9510的特性、功能、工作模式以及應(yīng)用注意事項,為電子工程師們提供全面的設(shè)計參考。

文件下載:AD9510.pdf

一、AD9510的關(guān)鍵特性

1.1 低相位噪聲PLL核心

AD9510集成了低相位噪聲的鎖相環(huán)(PLL)核心,參考輸入頻率可達250 MHz。可編程的雙模數(shù)預(yù)分頻器和電荷泵電流設(shè)置,為頻率合成提供了靈活的配置選項。同時,獨立的電荷泵電源(VCPS)擴展了調(diào)諧范圍,確保在不同應(yīng)用場景下都能實現(xiàn)精確的頻率鎖定。

1.2 豐富的時鐘輸入與輸出

芯片具備兩個1.6 GHz的差分時鐘輸入(CLK1和CLK2),可適應(yīng)高速時鐘信號的輸入需求。輸出方面,提供了8個可編程分頻器,分頻比范圍為1至32,所有輸出均為整數(shù)分頻。其中,4個為1.2 GHz的LVPECL輸出,具有低抖動特性,附加輸出抖動僅為225 fs rms;另外4個輸出可選擇為800 MHz的LVDS或250 MHz的CMOS電平,LVDS和CMOS輸出的附加輸出抖動為275 fs rms。

1.3 靈活的相位與延遲調(diào)整

通過分頻器相位選擇功能,可實現(xiàn)輸出之間的粗延遲調(diào)整,方便用戶對時鐘信號的相位進行靈活配置。此外,兩個LVDS/CMOS輸出還具備精細延遲調(diào)整功能,全量程延遲范圍可達8 ns,具有5位分辨率,提供25種可能的延遲設(shè)置,滿足了對時鐘信號延遲精度要求較高的應(yīng)用場景。

1.4 其他特性

采用節(jié)省空間的64引腳LFCSP封裝,便于在緊湊的電路板設(shè)計中使用。支持串行控制端口,方便與微控制器或其他控制設(shè)備進行通信,實現(xiàn)對芯片的靈活配置。

二、AD9510的功能模塊詳解

2.1 PLL部分

PLL部分是AD9510的核心之一,主要由可編程參考分頻器(R)、低噪聲相位頻率檢測器(PFD)、精密電荷泵(CP)和可編程反饋分頻器(N)組成。通過連接外部壓控晶體振蕩器(VCXO)或壓控振蕩器(VCO)到CLK2和CLK2B引腳,可將高達1.6 GHz的頻率同步到輸入?yún)⒖夹盘枴LL的數(shù)字和模擬鎖定檢測功能,可實時監(jiān)測鎖定狀態(tài),確保系統(tǒng)穩(wěn)定運行。

2.2 時鐘輸入與分布部分

CLK1和CLK2輸入可用于驅(qū)動分布部分,輸入頻率可達1.6 GHz。較高的輸入擺率可改善抖動性能,輸入電平需控制在150 mV p - p至2 V p - p之間,以避免保護二極管開啟對抖動性能產(chǎn)生影響。每個輸出都有獨立的可編程分頻器,可實現(xiàn)1至32的整數(shù)分頻,還可對分頻比、相位和占空比進行靈活配置。

2.3 延遲塊

OUT5和OUT6輸出包含模擬延遲元件,可通過寄存器編程實現(xiàn)1 ns至8 ns的可變延遲。延遲量的設(shè)置需根據(jù)時鐘頻率進行合理調(diào)整,該延遲功能主要用于為數(shù)字芯片(如FPGA、ASIC等)提供時鐘信號,但由于會引入一定的抖動,不建議用于數(shù)據(jù)轉(zhuǎn)換器的時鐘。

三、AD9510的典型工作模式

3.1 PLL與時鐘分配模式

這是AD9510最常見的工作模式,外部振蕩器(VCXO/VCO)與REFIN輸入的參考頻率進行鎖相,通過PLL對參考信號進行處理后,將輸出信號提供給時鐘分布部分。在該模式下,可根據(jù)需要設(shè)置合適的分頻比,以滿足不同輸出頻率的要求。同時,可通過關(guān)閉未使用的功能和時鐘通道來節(jié)省功耗。

3.2 僅時鐘分配模式

當(dāng)不需要PLL功能時,可單獨使用分布部分。此時,CLK1和CLK2輸入可通過低抖動多路復(fù)用器直接將時鐘信號分配到輸出端。這種模式下,同樣可通過關(guān)閉PLL塊和未使用的時鐘通道來降低功耗,但由于沒有PLL的時鐘清理功能,輸入時鐘信號的抖動會直接傳遞到輸出端。

3.3 PLL與VCO及帶通濾波器的時鐘分配模式

使用外部帶通濾波器(BPF)可改善PLL輸出的相位噪聲和雜散特性。這種模式適用于選擇價格較低的VCO并結(jié)合中等價格濾波器以優(yōu)化成本的應(yīng)用場景。BPF輸出連接到CLK1,同樣可通過關(guān)閉未使用的功能和時鐘通道來節(jié)省功耗。

四、AD9510的電源與功耗管理

4.1 電源要求

AD9510需要一個3.3 V ± 5%的電源((V{s})),VS引腳的絕對最大電壓范圍為?0.3 V至 +3.6 V。同時,VCP引腳作為電荷泵的電源,電壓范圍為(V{s})至5.5 V,但不得超過6 V,且VCP不得低于VS或GND的?0.3 V。在PCB設(shè)計中,需遵循良好的工程實踐,對電源進行適當(dāng)?shù)呐月?a href="http://www.3532n.com/tags/電容/" target="_blank">電容配置,以確保芯片穩(wěn)定工作。

4.2 功耗管理

AD9510提供了豐富的功耗管理選項,可對PLL部分、分布部分、各個輸出以及其他電路塊進行單獨的電源關(guān)閉操作。例如,當(dāng)不使用PLL時可將其關(guān)閉;旁路分頻器時可降低功耗;當(dāng)不需要延遲功能時可關(guān)閉OUT5和OUT6的延遲塊等。關(guān)閉功能模塊不會導(dǎo)致寄存器中的編程信息丟失,但會失去同步,需要重新進行同步操作。

五、AD9510在不同應(yīng)用場景中的注意事項

5.1 ADC時鐘應(yīng)用

高速ADC對采樣時鐘的質(zhì)量極為敏感,時鐘的噪聲、失真和抖動會直接影響ADC的性能。AD9510的LVPECL和LVDS差分輸出可提供低抖動的時鐘信號,有助于提高ADC的信噪比(SNR)。在選擇時鐘輸出時,需考慮ADC的輸入要求(如差分或單端、邏輯電平、終端匹配等)。

5.2 CMOS時鐘分配

當(dāng)使用AD9510的CMOS輸出進行時鐘分配時,建議采用點對點網(wǎng)絡(luò)設(shè)計,盡量使驅(qū)動器只連接一個接收器,以減少阻抗不匹配導(dǎo)致的振鈴問題。同時,可采用源端串聯(lián)終端或遠端終端匹配的方式來改善信號傳輸質(zhì)量。由于CMOS輸出驅(qū)動電容負載和長走線的能力有限,建議走線長度小于3英寸。

5.3 LVPECL和LVDS時鐘分配

LVPECL輸出需要直流終端來偏置輸出晶體管,推薦使用標準的LVPECL遠端終端配置。LVDS輸出采用電流模式輸出級,具有多種可選的電流水平,推薦使用100 Ω的差分終端電阻。這兩種差分輸出方式具有較好的抗噪聲能力,適用于長走線和高速信號傳輸?shù)膽?yīng)用場景。

六、總結(jié)

AD9510作為一款高性能的時鐘分配IC,憑借其低相位噪聲、豐富的輸入輸出配置、靈活的相位和延遲調(diào)整功能以及有效的功耗管理選項,在眾多應(yīng)用領(lǐng)域中具有廣泛的應(yīng)用前景。電子工程師在設(shè)計過程中,需充分了解其特性和功能,結(jié)合具體應(yīng)用場景進行合理配置,以實現(xiàn)系統(tǒng)的最佳性能。同時,在PCB設(shè)計和電源管理方面,需遵循相關(guān)的工程實踐,確保芯片的穩(wěn)定運行。你在使用AD9510過程中遇到過哪些挑戰(zhàn)呢?歡迎在評論區(qū)分享你的經(jīng)驗和見解。

-

應(yīng)用指南

+關(guān)注

關(guān)注

0文章

109瀏覽量

6128

發(fā)布評論請先 登錄

探索ADN2816:高性能時鐘和數(shù)據(jù)恢復(fù)IC的深度剖析

AD9524:高性能時鐘發(fā)生器的深度剖析與應(yīng)用指南

AD9522-1:高性能時鐘發(fā)生器的深度剖析與應(yīng)用指南

AD9518-1:高性能時鐘發(fā)生器的深度剖析與應(yīng)用指南

AD9514:高性能多輸出時鐘分配IC的技術(shù)剖析與應(yīng)用

深入剖析AD9512:高性能時鐘分配IC的卓越之選

LTC3372:高性能多輸出電源IC的深度剖析與應(yīng)用指南

Texas Instruments CDC536:高性能時鐘驅(qū)動器的深度剖析

解析CDCL1810:高性能時鐘分配器的技術(shù)剖析與應(yīng)用指南

深入剖析LMK01000:高性能時鐘緩沖、分頻與分配器

CDCE62005:高性能時鐘發(fā)生器與分配器的深度剖析

解鎖高性能時鐘緩沖:LMK00304深度剖析

LMK1D1208I:高性能LVDS時鐘緩沖器的深度剖析與應(yīng)用指南

AD9510 1.2 GHz時鐘分配IC,PLL內(nèi)核,分頻器,延遲調(diào)整,8路輸出技術(shù)手冊

AD9510:高性能時鐘分配IC的深度剖析與應(yīng)用指南

AD9510:高性能時鐘分配IC的深度剖析與應(yīng)用指南

評論