解鎖高性能時鐘緩沖:LMK00304深度剖析

在電子設(shè)備高速發(fā)展的今天,時鐘信號的穩(wěn)定與精確對于系統(tǒng)性能至關(guān)重要。LMK00304作為一款高性能的時鐘緩沖器,在諸多領(lǐng)域有著廣泛應(yīng)用。本文將深入解析LMK00304的特性、應(yīng)用及設(shè)計要點,希望能為各位電子工程師在實際設(shè)計中提供一些有價值的參考。

文件下載:lmk00304.pdf

認識LMK00304

特性概覽

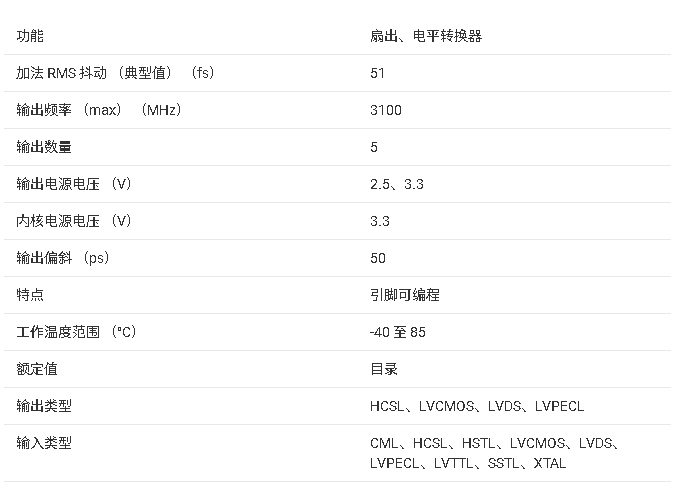

LMK00304是一款3 - GHz、4輸出的超低附加抖動差分時鐘緩沖器/電平轉(zhuǎn)換器。它具有以下幾個顯著特性:

- 輸入靈活:配備3:1輸入多路復(fù)用器,兩個通用輸入可處理高達3.1 GHz的信號,支持LVPECL、LVDS、CML、SSTL、HSTL、HCSL或單端時鐘。還有一個晶體輸入,可接受10 - 40 MHz的晶體或單端時鐘。

- 輸出多樣:擁有兩個輸出組,每組2個差分輸出,可配置為LVPECL、LVDS、HCSL或高阻態(tài)。此外,還有一個帶同步使能輸入的LVCMOS輸出。

- 低抖動性能:在156.25 MHz下,使用LMK03806時鐘源時,LVPECL附加抖動極低,10 kHz至1 MHz為20 fs RMS,12 kHz至20 MHz為51 fs RMS。

- 高電源抑制比:在156.25 MHz時,LVPECL/LVDS的PSRR分別為 - 65 / - 76 dBc。

- 寬工作范圍:工業(yè)溫度范圍為 - 40°C至 + 85°C,采用32引腳WQFN封裝(5 mm × 5 mm)。

應(yīng)用領(lǐng)域

LMK00304適用于多種高速、低抖動時鐘和數(shù)據(jù)分配及電平轉(zhuǎn)換的應(yīng)用場景,如ADC、DAC、多千兆以太網(wǎng)、XAUI、光纖通道、SATA/SAS、SONET/SDH、CPRI、高頻背板等。在交換機、路由器、線卡、定時卡、服務(wù)器、計算設(shè)備、PCI Express(PCIe 3.0)、遠程無線電單元和基帶單元等設(shè)備中都能發(fā)揮重要作用。

深入了解LMK00304的性能指標(biāo)

規(guī)格參數(shù)

LMK00304的各項規(guī)格參數(shù)是其性能的重要體現(xiàn),在設(shè)計中需要重點關(guān)注。

- 絕對最大額定值:電源電壓((V{CC}),(V{CCO}))范圍為 - 0.3至3.6 V,輸入電壓范圍為 - 0.3至((V_{CC}) + 0.3)V,存儲溫度范圍為 - 65至 + 150°C等。超出這些額定值可能會對器件造成永久性損壞。

- ESD額定值:人體模型(HBM)為 ± 2000 V,機器模型(MM)為 ± 150 V,帶電設(shè)備模型(CDM)為 ± 750 V。在使用和處理時需要注意靜電防護。

- 推薦工作條件:環(huán)境溫度范圍為 - 40至85°C,結(jié)溫不超過125°C,(V{CC}) 為3.15至3.45 V,(V{CCO}) 為2.5 ± 5%。

電氣特性

電氣特性涵蓋了電流消耗、電源紋波抑制、輸入輸出參數(shù)等多個方面。

- 電流消耗:不同輸出配置下,核心電源電流和輸出電源電流有所不同。例如,所有輸出禁用時,核心電源電流((I_{CC_CORE}))在CLKinX選擇時最大為10.5 mA,OSCin選擇時最大為13.5 mA。

- 電源紋波抑制(PSRR):PSRR是衡量時鐘輸出對電源紋波抗干擾能力的指標(biāo)。在不同頻率和輸出類型下,PSRR表現(xiàn)不同。如在156.25 MHz時,LVDS輸出的PSRR為 - 76 dBc。

- 時鐘輸入:輸入頻率范圍可達3.1 GHz,輸入差分電壓擺幅((V_{ID}))為0.15至1.3 V等。為了獲得最佳性能,建議輸入信號具有較高的轉(zhuǎn)換速率(≥3 V/ns)。

- 輸出特性:不同輸出類型(LVPECL、LVDS、HCSL、LVCMOS)的輸出頻率、抖動、噪聲等特性各不相同。例如,LVPECL輸出在不同條件下的最大輸出頻率和附加抖動都有明確的指標(biāo)。

LMK00304的設(shè)計要點

時鐘輸入設(shè)計

LMK00304的時鐘輸入部分有兩個通用輸入和一個晶體輸入。為了獲得最佳的相位噪聲和抖動性能,輸入信號應(yīng)具有較高的轉(zhuǎn)換速率(≥3 V/ns),且建議使用差分信號輸入。

- 單端輸入處理:當(dāng)使用單端時鐘輸入時,對于大信號輸入(如3.3V或2.5V LVCMOS),需要在輸入附近放置50Ω負載電阻進行信號衰減和線路終端匹配,以防止輸入過驅(qū)動和反射。

- 晶體輸入:如果選擇晶體輸入,需要注意晶體的特性,如等效串聯(lián)電阻(ESR)等。同時,要合理計算負載電容,以確保晶體振蕩器正常啟動和穩(wěn)定工作。

晶體接口設(shè)計

晶體接口部分支持基本模式、AT切割晶體。在設(shè)計時,需要根據(jù)晶體的負載電容((C{L}))、器件的OSCin輸入電容((C{IN}))和PCB雜散電容((C{STRAY}))來計算離散負載電容值((C{1})和(C{2}))。此外,還需要注意晶體的功耗,避免過度驅(qū)動晶體導(dǎo)致老化、頻率漂移甚至失效。可以使用外部電阻((R{LIM}))來限制晶體驅(qū)動電平。

輸出端接和時鐘驅(qū)動器使用

時鐘驅(qū)動器的端接對于優(yōu)化相位噪聲和抖動性能至關(guān)重要。需要遵循傳輸線理論進行良好的阻抗匹配,避免反射。不同輸出類型的端接方式不同:

- LVDS輸出:是電流驅(qū)動器,需要一個閉合的電流回路,通常在LVDS接收器附近端接100Ω電阻。

- HCSL輸出:是開關(guān)電流輸出,需要通過50Ω端接電阻連接到地的直流路徑,不允許在輸出驅(qū)動器和50Ω端接電阻之間進行交流耦合。

- LVPECL輸出:是開放發(fā)射極,需要連接到地的直流路徑,通常端接50Ω到(V_{cco}-2V)。

電源設(shè)計

電源設(shè)計方面,需要注意電源排序、電流消耗和功率耗散計算、電源旁路和熱管理。

- 電源排序:當(dāng)從不同的電源軌為(V{CC})和(V{CCO})引腳供電時,建議在電源上升或下降時同時達到穩(wěn)定點,以避免內(nèi)部電流從(V{CC})流向(V{CCO})引腳。

- 電流消耗和功率耗散計算:可以根據(jù)電氣特性中規(guī)定的電流消耗值來計算總功耗和IC功耗。不同的輸出配置會影響電流消耗,進而影響功率耗散。

- 電源旁路:(V{CC})和(V{CCO})電源應(yīng)在每個電源引腳附近放置高頻旁路電容(如0.1 μF或0.01 μF),并在器件附近放置1 - 10 μF的去耦電容,以減小電源噪聲。

- 熱管理:由于LMK00304的功耗可能較高,需要注意熱管理。可以通過在PCB上設(shè)計散熱焊盤和多個過孔連接到接地層,以及使用簡單的散熱片來降低結(jié)溫。

總結(jié)

LMK00304以其高性能、靈活性和低抖動特性,為電子工程師在高速時鐘分配和電平轉(zhuǎn)換設(shè)計中提供了一個優(yōu)秀的解決方案。在實際應(yīng)用中,我們需要深入理解其各項特性和設(shè)計要點,根據(jù)具體的應(yīng)用場景進行合理的設(shè)計和優(yōu)化,以確保系統(tǒng)的穩(wěn)定性和可靠性。各位工程師在使用LMK00304時是否遇到過一些特殊的問題?又是如何解決的呢?歡迎在評論區(qū)分享你的經(jīng)驗和見解。

-

時鐘緩沖器

+關(guān)注

關(guān)注

2文章

270瀏覽量

51910

發(fā)布評論請先 登錄

LMK00304 3GHz 4路輸出超低附加抖動差動時鐘緩沖器/電平轉(zhuǎn)換器數(shù)據(jù)表

LMK00304 3.1 GHz 差分時鐘緩沖器/電平轉(zhuǎn)換器技術(shù)手冊

解鎖高性能時鐘緩沖:LMK00304深度剖析

解鎖高性能時鐘緩沖:LMK00304深度剖析

評論