高開關頻率下的SiC三電平逆變器短路保護與故障容錯機制研究

1. 引言

在全球能源結構轉型與工業電氣化深度發展的背景下,高功率密度、高效率以及高電能質量的電能變換系統成為了電力電子技術的核心追求。以碳化硅(SiC)金屬氧化物半導體場效應晶體管(MOSFET)為代表的寬禁帶(WBG)半導體器件,憑借其高擊穿電場強度、低導通電阻以及卓越的高頻開關特性,正在全面取代傳統的硅(Si)基絕緣柵雙極型晶體管(IGBT)。在光伏逆變器、電動汽車(EV)主驅牽引逆變器以及大容量儲能系統(ESS)中,為了在提升開關頻率的同時有效降低開關管的電壓應力及輸出電壓的諧波畸變率(THD),三電平(3L)拓撲結構——特別是中性點鉗位型(NPC)與T型中性點鉗位型(T-Type NPC)逆變器——已成為行業的主流架構。傾佳電子力推BASiC基本半導體SiC碳化硅MOSFET單管,SiC碳化硅MOSFET功率模塊,SiC模塊驅動板,PEBB電力電子積木,Power Stack功率套件等全棧電力電子解決方案。?

傾佳電子楊茜致力于推動國產SiC碳化硅模塊在電力電子應用中全面取代進口IGBT模塊,助力電力電子行業自主可控和產業升級!

然而,SiC MOSFET的物理結構特性在賦予其極致性能的同時,也引入了嚴峻的可靠性挑戰。為了在相同的額定電流下實現更低的導通損耗,SiC芯片的設計面積通常遠小于同等規格的Si IGBT,這直接導致其內部熱容極大幅度降低。在發生短路故障時,瞬態極高的短路電流密度與微小的芯片體積相結合,使得SiC MOSFET的短路耐受時間(Short-Circuit Withstand Time, SCWT)急劇縮短。傳統Si IGBT的SCWT通常在10微秒(μs)左右,而現代商用SiC MOSFET的SCWT普遍低于2至3微秒,在極端母線電壓下甚至逼近1微秒。在結構復雜、元器件眾多的三電平逆變器系統中,任何單一器件的直通(Shoot-through)或開路故障都可能在極短時間內引發系統性的災難性損毀。

傾佳楊茜剖析高開關頻率下SiC三電平逆變器的短路保護與故障容錯機制。報告首先從SiC器件的底層物理限制出發,結合附件中BASiC Semiconductor(基本半導體)最新一代SiC分立器件與功率模塊的詳盡參數,量化分析其短路脆弱性;其次,系統性地對NPC與T-Type三電平拓撲中特有的直通短路模式進行分類與數理推演;進而,全面評估基于超快速退飽和(Desat)、羅氏線圈(Rogowski Coil)以及源極寄生電感(di/dt)的前沿高速短路檢測與保護電路設計方案;最后,深入探討在發生單管失效時,三電平逆變器如何通過軟硬件協同的容錯控制策略,無縫降級為兩電平(2L)拓撲維持降額運行,從而在極端工況下最大限度地保障關鍵任務系統的可用性與安全性。

2. SiC MOSFET 短路失效機理與器件特性分析

在探究系統級保護機制之前,必須深刻理解SiC MOSFET在短路極限工況下的物理演變過程。由于三電平逆變器內部換流回路的復雜性,器件在短路瞬間承受的不僅是靜態的電壓與電流極限,更是極高 dv/dt 與 di/dt 耦合下的動態電熱沖擊。

2.1 SiC器件的短路耐受時間(SCWT)瓶頸與失效物理

當逆變器橋臂發生短路時,SiC MOSFET被迫退出線性導通區,進入有源飽和區。此時,器件兩端同時承受直流母線的高電壓(VDS?)以及由器件溝道特性決定的極高飽和短路電流(ID,sat?)。這兩者的乘積在芯片內部產生兆瓦(MW)級別的瞬態焦耳熱。

SiC MOSFET在短路工況下的脆弱性主要源于以下三個物理機制: 第一,極高的飽和電流密度。為了克服SiC/SiO2界面處較高的界面陷阱密度對溝道載流子遷移率的不利影響,制造商普遍采用極短的溝道長度(通常約為0.5μm)設計。這種短溝道設計在短路工況下會引發嚴重的短溝道效應(如漏極誘導勢壘降低,DIBL),使得短路電流峰值極易飆升至額定工作電流的10至15倍。 第二,微小的熱容積。在額定電壓與電流相同的前提下,SiC芯片的面積通常僅為Si IGBT的五分之一至三分之一。這意味著在短路期間,產生的海量焦耳熱無法在微秒級時間內傳導至外部散熱基板,只能積聚在極薄的外延層和溝道區域,導致結溫(Tj?)在1至2微秒內從正常的運行溫度驟升至500°C甚至上千度。 第三,兩種主導失效模式。在較低的直流母線電壓下,急劇升高的溫度會產生巨大的熱機械應力,導致層間介質破裂或柵極氧化層(Gate Oxide)絕緣擊穿,表現為柵源極短路;而在較高的母線電壓(如800V或1000V以上)下,器件內部晶格溫度超過金屬鋁的熔點(約660°C),導致芯片表面的源極金屬鋁層熔化,甚至引發熱失控,最終表現為漏源極永久性燒毀短路。

2.2 基于BASiC Semiconductor SiC器件的電熱極限解析

為了將上述理論具體化,本報告對附件中提供的五款來自BASiC Semiconductor(基本半導體)的工業級與車規級SiC MOSFET分立器件及高電流功率模塊的電學參數進行了深度提取與交叉對比。這為后續短路保護電路的時間常數設計和容錯機制的電流余量計算提供了精確的工程基準。

| 關鍵參數特征 | B3M010C075Z (分立) | B3M011C120Y (分立) | B3M020120ZN (分立) | BMF540R12KHA3 (模塊) | BMF540R12MZA3 (模塊) |

|---|---|---|---|---|---|

| 擊穿電壓極限 (VDSS?) | 750 V | 1200 V | 1200 V | 1200 V | 1200 V |

| 連續漏極電流 (ID?) | 240 A (TC?=25°C) | 223 A (TC?=25°C) | 127 A (TC?=25°C) | 540 A (TC?=65°C) | 540 A (TC?=90°C) |

| 脈沖漏極電流 (IDM?) | 480 A | 1000 A | 225 A | 1080 A | 1080 A |

| 最大瞬態功耗 (PD?) | 750 W | 250 W | 600 W | 1563 W | 1951 W |

| 典型輸出電容 (Coss?) | 370 pF | 250 pF | 157 pF | 1.26 nF | 1.26 nF |

| 內部柵極電阻 (RG(int)?) | 1.7 Ω | 1.5 Ω | 1.4 Ω | 1.95 Ω | 1.95 Ω |

| 功率回路雜散電感 (Lσ?) | 封裝未列出具體值 | 封裝未列出具體值 | 具備Kelvin Source引腳 | 30 nH | 30 nH |

| 導通/關斷延遲 (td(on)? / td(off)?) | 參數缺失 | 參數缺失 | 參數缺失 | 119 ns / 205 ns (25°C) | 118 ns / 183 ns (25°C) |

表1:BASiC Semiconductor 典型SiC MOSFET分立器件與半橋功率模塊的核心電學極值與高頻動態參數比較。

通過對上述數據的多維解析,可以得出三電平高頻操作下的幾個核心工程洞察: 首先,極端的電流變化率(di/dt)挑戰。以工業級模塊BMF540R12MZA3為例,其在TC?=90°C時仍能維持540A的連續電流,其脈沖電流容限(IDM?)高達1080A。該模塊采用了先進的 Si3?N4? AMB陶瓷基板及內部低雜散電感設計,回路寄生電感僅為 30 nH。若在典型的800V直流母線電壓下發生直通短路,初始階段的電流變化率將達到驚人的 di/dt=V/Lσ?≈26.6kA/μs。這意味著在不到 50 納秒(ns)的時間內,短路電流就會突破其1080A的絕對物理極限,這對任何傳統的延遲保護電路而言都是致命的。 其次,瞬態功耗的非線性爆發。BMF540R12MZA3模塊的最大功率耗散能力為1951W(在TC?=25°C下測試)。在失效負載(FUL)短路工況下,器件瞬間承受800V母線電壓與可能高達3000A以上的非受控飽和電流,瞬時功耗將飆升至2.4兆瓦(MW)以上。即使AMB基板具有極佳的導熱性能,這種超出額定功耗三個數量級的瞬態能量若維持超過2微秒,依然會直接摧毀裸片結構。 最后,高頻開關引發的寄生參數耦合。分立器件如B3M010C075Z與B3M020120ZN均配備了Kelvin源極(Pin 3),用于在極高頻驅動時解耦主功率回路與門極驅動回路。在高頻三電平調制中,開關管所承受的共模與差模 dv/dt 極高。盡管SiC器件擁有極小的反向傳輸電容(例如B3M020120ZN的 Crss? 為 10 pF,相對其3850 pF的 Ciss? 較小),但超過 50 V/ns 的高 dv/dt 仍會通過米勒電容注入巨大的位移電流(IMiller?=Crss??dv/dt),如果未被驅動電路的次級有源鉗位功能有效抑制,將導致同一橋臂的互補管發生寄生導通(Parasitic Turn-on),從而誘發三電平逆變器中特有的局部直通短路故障。

3. 三電平拓撲中的短路與直通模式分類

在明確了SiC器件極窄的生存窗口后,必須將器件置于具體的三電平逆變器拓撲中進行系統級失效模式映射。傳統兩電平逆變器的短路模式相對單一(上、下管直通或相間短路),而三電平拓撲(無論NPC還是T-Type)由于引入了鉗位二極管或雙向中性點開關以及分裂的直流母線電容,其換流路徑成倍增加,直通短路模式也相應變得極其復雜。

3.1 HSF與FUL故障工況的定義

無論哪種具體的拓撲結構,短路發生時的電氣初始狀態可以嚴格分為兩類:

硬開關故障(Hard Switching Fault, HSF): 亦稱為Type I型短路。在驅動信號發出使SiC MOSFET開通之前,負載側或橋臂內部已經存在短路回路。當器件響應驅動指令瞬間開啟時,直接短接高壓母線。此時器件承受極高的 di/dt 與滿額母線電壓,處于最惡劣的電流階躍狀態。

負載下故障(Fault Under Load, FUL): 亦稱為Type II型短路。SiC MOSFET已經在正常導通狀態下攜帶負載電流運行(處于線性歐姆區),此時系統外部(如電機繞組絕緣失效)突然發生短路。器件電流急劇上升直至飽和,漏源極電壓(VDS?)由于電流退出線性區而迅速從導通壓降被強行拉升至母線電壓。FUL工況由于存在較長的預熱時間,對溫度高度敏感,且更易引發保護電路的誤判或檢測延遲。

3.2 NPC三電平逆變器的直通故障分類

標準NPC逆變器的每一相橋臂由四個串聯的功率管(定義為 Sx1? 至 Sx4?,其中x代表相別)及兩個連接至直流鏈路中性點的鉗位二極管組成。其直通故障不僅涉及跨越整個母線的短路,還涉及破壞局部直流電容平衡的短路。

全橋臂直通(Phase-Leg Short-Circuit): 極少發生但最具破壞性的故障。要求 Sx1? 到 Sx4? 全部處于導通狀態,或者部分管子發生永久性擊穿短路的同時其余管子被錯誤觸發。此時,正負母線被完全短接,巨大的電容放電電流將在微秒內引發爆炸性破壞。

上半橋/下半橋臂局部直通(Half-Arm Shoot-Through): 這是NPC拓撲特有的故障類型。例如,當外側開關 Sx1?、內側開關 Sx2? 以及上半臂鉗位二極管形成異常閉合回路時,上半部直流母線電容(C1?)被直接短路放電。同理,Sx3?、Sx4? 與下部鉗位二極管可構成針對下半部直流電容的局部短路。由于只有單側電容放電,這種短路會導致嚴重的直流中性點電位(NPV)偏移,將全母線電壓強加于未短路側的剩余健康器件上,引發級聯過壓擊穿失效。

3.3 T-Type三電平逆變器的直通故障分類

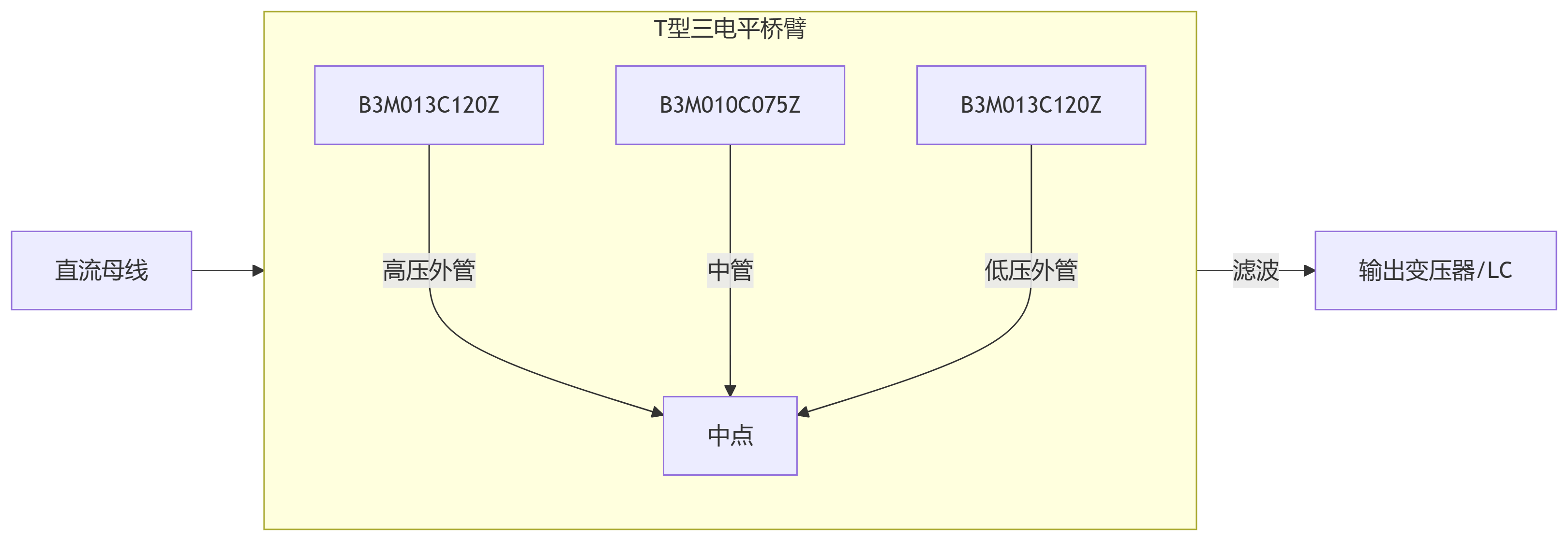

T型三電平逆變器由一個跨接在正負母線上的標準兩電平半橋(主開關 S1?, S4?)和一條由兩個反串聯器件(S2?, S3?)組成的中性點雙向箝位支路構成。這種架構在降低導通損耗的同時,使直通模式更加隱蔽。

主開關直通(Main Branch Shoot-Through): 類似于兩電平橋臂,當 S1? 與 S4? 同時導通時,直接短接正負直流母線。此時,由于T-Type主開關往往承載全母線電壓,此處的短路能量最為龐大。

中性點支路至母線直通(Neutral-Point to Bus Short-Circuit): 當系統指令輸出正電平(+Vdc/2)時,S1? 導通;此時如果中性點雙向支路(S2?, S3?)由于柵極干擾或邏輯錯誤而發生誤導通,正母線與中性點之間將形成直接短路回路,使得上半部電容瞬時放電。相應的,負母線短路發生于 S4? 與中性點支路同時導通之時。這種基于共模干擾誘發的半臂直通,是高頻驅動下T-Type拓撲需要防御的核心故障模式。

4. 應對高開關頻率的高速短路檢測與保護電路設計

面對SiC器件嚴格的 2-3 μs 甚至更短的SCWT邊界,傳統的基于毫秒或微秒級響應的保護邏輯已徹底失效。為保障高頻三電平逆變器的生存,前沿驅動設計必須在檢測傳感器的物理機制與信號處理的延遲控制上進行根本性革新。當前行業內最新的設計方案主要分為超快速退飽和檢測、羅氏線圈非侵入式測量以及源極寄生電感耦合檢測三大流派。

4.1 超快速退飽和(Ultrafast Desat)檢測優化

退飽和(Desat)檢測是工業界最成熟且低成本的保護方案,其基本原理是監測導通期間的漏源極電壓(VDS?)。正常情況下,處于線性區的SiC MOSFET的 VDS? 僅為數伏特;發生短路時,器件進入飽和區,VDS? 急速上升并觸碰保護比較器的閾值(通常設定為7V至9V)。

傳統Desat的痛點: 由于SiC器件在高頻開通瞬間會產生極高的 dvds?/dt(常常超過50 V/ns),這會在檢測電路的阻容網絡中產生巨大的共模位移電流。為了防止這種瞬態噪聲引發保護電路的誤觸發,傳統設計被迫并聯一個較大的消隱電容(Blanking Capacitor, Cblk?)以引入消隱時間(Blanking Time)。實驗數據表明,傳統Desat電路的消隱時間及濾波延遲通常高達 400 ns 至 500 ns。加上驅動關斷的物理延遲,器件在短路電流中裸奔的時間常常逼近 1.5 μs,極易導致模塊內部熱疲勞甚至引發災難性爆炸。此外,SiC MOSFET的 RDS(on)? 對溫度極度敏感,在 25°C 至 175°C 區間內可能翻倍(如BMF540R12MZA3模塊從2.2 mΩ升至3.8 mΩ ),這使得恒定閾值的Desat電路容易在高溫滿載時發生誤動。

最新Ultrafast Desat設計: 為突破這一局限,最新的超快速Desat方案摒棄了傳統的長RC時間常數設計。該設計巧妙地利用了SiC MOSFET正常開通時自身產生的極高負向 dvds?/dt (通常在 -30 V/ns 到 -100 V/ns 之間)。設計中大幅削減甚至完全去除了物理消隱電容 Cblk?,轉而僅利用PCB走線和高壓隔離二極管的寄生電容(等效電容被嚴格控制在極小的 15 pF 到 51.2 pF 范圍內)。 當器件正常開通時,極高的負向 dv/dt 會生成強烈的位移電流,瞬時抽干檢測節點的電荷,強行將 Vdesat? 鉗位至安全電壓以下,從而在極短的硬延遲下實現了“自適應的動態消隱”。在針對高壓SiC器件的嚴苛HSF和FUL測試中,這種優化方案將短路檢測時間(Tdet?)壓縮至驚人的 82 ns,系統總響應動作時間僅為 115 ns 至 155 ns。這一創新極大地提升了保護的實時性,同時維持了Desat方案的低成本優勢。

4.2 基于PCB微型羅氏線圈(Rogowski Coil)的寬頻電流檢測

與間接監測電壓的Desat方法相比,直接監測漏極或相電流是理論上最可靠的短路識別路徑。然而,傳統電流互感器體積龐大且由于高壓隔離要求,無法集成至空間緊湊的三電平逆變器橋臂中。

技術前沿: 最新的非侵入式測量技術是將微型羅氏線圈(Rogowski Switch-Current Sensor, RSCS)直接嵌入在驅動板的PCB疊層內部。這種設計圍繞連接直流母排與SiC MOSFET漏極(Drain)端子的功率銅排進行電磁耦合。 由于摒棄了磁芯,空氣芯羅氏線圈不存在磁飽和現象,其高頻響應極佳。通過先進的三維有限元分析(FEM)在COMSOL等軟件中優化走線幾何形狀,最新的PCB羅氏線圈能夠實現高達 0.175nH/mm3 的互感系數,這在保持線圈尺寸微小的同時,獲取了極高的靈敏度。更重要的是,緊湊的線圈設計推高了傳感器的固有自然諧振頻率(高達 469 MHz),賦予了檢測電路卓越的寬帶特性。 性能優勢: 在同步對比測試中,基于RSCS的短路保護系統無論是在常溫(25°C)還是高溫(175°C)下,均表現出極高的一致性。其檢測延遲被控制在 80 ns 以內。由于在短路電流上升的極早期便切斷了回路,RSCS保護下的SiC模塊在短路期間的耗散能量(Esc?)僅為傳統Desat方案的一半以下,有效扼殺了熱失控的萌芽。盡管需要額外的模擬積分電路并增加了驅動板的BOM成本,但其在航空推進、高頻工業母機等高附加值應用中已展現出不可替代的價值。

4.3 基于Kelvin源極寄生電感的無源 di/dt 檢測技術

為了兼顧檢測速度與系統成本,行業內目前最受矚目的創新方案是提取并利用SiC MOSFET封裝內部固有的寄生電感(Parasitic Inductance)。

原理與架構: 以附錄中的BASiC B3M020120ZN離散器件(采用TO-247-4NL封裝)以及BMF540系列高功率模塊為例,這些器件為了抑制柵極回路的共模干擾,均專門引出了開爾文源極(Kelvin Source, Pin 3)。功率源極(Power Source)與開爾文源極之間在物理鍵合線與引腳上存在一段微小的寄生電感(記為 Lp?),其感值通常在離散器件中為 3 nH,在功率模塊中約為幾十 nH(例如BMF系列模塊整體回路寄生電感為 30 nH)。 當三電平橋臂發生直通故障時,極高的電流上升率(did?/dt)流經功率回路。根據法拉第電磁感應定律,在Kelvin源極與功率源極之間會感應出一個與電流變化率成正比的微小瞬態電壓:VK?=Lp??(did?/dt) 。 電路設計實現: 檢測電路由跨接在該兩端點上的積分阻容網絡(Rs?, Cs?)構成。為了避免分流影響主功率回路,Rs?與Cs?支路的阻抗被設計得遠大于寄生電感Lp?支路。通過該RC積分網絡,高頻的 di/dt 尖峰電壓被精確重構為與主回路漏極電流 id? 成比例的輸出電壓信號:vo?≈(Lp?/Rs?Cs?)?id? 。 該方案完全不依賴外部傳感器磁性元件,具有極寬的傳感帶寬且完全不受結溫漂移的影響。其對于硬開關故障(HSF)的響應時間穩定在 80 ns 到 100 ns 之間,反應速度媲美昂貴的羅氏線圈方案,代表了下一代高集成度智能柵極驅動(Smart Gate Driver)的發展方向。

4.4 軟關斷(Soft Turn-Off)與過電壓抑制

無論采用何種極速檢測手段,保護電路在發出關斷指令時必須面對一個致命的物理約束:如果在高達1000A以上的短路電流下強行以最高速度硬關斷SiC MOSFET,三電平逆變器母排及模塊內部的雜散電感(如 30 nH)將依據 Vspike?=Lσ??(di/dt) 產生災難性的過電壓尖峰。這一尖峰極易超過器件的1200V耐壓極限,造成二次擊穿損毀。 因此,現代高頻短路保護電路均內置了多級軟關斷(STO)機制。當檢測到短路故障后,驅動器不會立即將柵極電壓拉至負偏壓(如 -5V),而是通過切換至一組較高阻值的關斷電阻(RG(off)?),或者啟動內部電流源將門極電荷按受控斜率緩慢泄放。這使得漏極電流以一個可控的低 di/dt 斜率下降,安全地將過電壓尖峰鉗位在器件的耐受裕度(SOA)之內。同時,為防止在軟關斷期間由于高 dv/dt 噪聲導致的米勒寄生導通,次級有源米勒鉗位(Active Miller Clamp)電路會被同步激活,死死咬住門極電位,確保關斷的絕對安全性。

5. 單管失效下的軟/硬件容錯機制:3L降級為2L運行策略

在航空航天、艦船電力推進、深海作業及關鍵醫療不間斷電源(UPS)等領域,系統對可用性的要求甚至超越了單純的組件保護。如果超快速保護電路成功切斷了短路電流,或者某個開關管發生了開路(Open-Circuit, OC)故障,直接封鎖整個三電平逆變器會導致全系統的動力喪失。因此,前沿的電力電子控制系統引入了復雜的故障容錯(Fault-Tolerant, FT)策略。當三電平逆變器某一相橋臂中的單管發生不可逆失效時,系統能夠通過硬件旁路與軟件算法的重構,將其從三電平(3L)平滑降級為兩電平(2L)拓撲,以犧牲部分波形質量和額定功率為代價,維持系統的不間斷運行。

5.1 在線故障診斷與拓撲定位

實施容錯降級的第一步是極速且精準地識別出故障開關的具體位置與失效類型。在閉環運行中,由于系統會自發嘗試糾正電流偏差,單純的電流幅值判斷往往會造成誤報。 先進的診斷機制通常結合相電流的軌跡畸變與中性點電位(NPV)的異常漂移進行聯合判別。例如,當指令要求輸出正電壓(P狀態)時,若相電流在穿越過零點后意外塌陷為零,且直流母線中性點電壓出現不可控偏移,則可精確定位到上橋臂主開關(如 S1?)發生了開路故障。為縮短診斷時間并提高抗干擾能力,最新的研究引入了改進型自適應滑模觀測器(IASMO)以及基于人工神經網絡(ANN)的模式識別算法。這些智能算法能夠提取電流諧波與功率波動的頻域特征,在不足 75% 的單個基波周期內,準確分離出單管失效乃至同一相內雙管同時失效的復雜故障組合。

5.2 基于輔助硬件的相臂解耦與重構

為了將損壞的三電平橋臂有效降級為兩電平運行,必須從物理電氣鏈路上隔離故障回路。這通常需要極少量的冗余硬件支撐。

NPC拓撲的重構: 在傳統的NPC逆變器中,如果是外側主開關(S1? 或 S4?)開路損壞,系統會失去輸出正向或負向全電壓的能力。如果內側開關(S2? 或 S3?)損壞,則失去了連接中性點輸出零電平(O狀態)的能力。為了實現硬件容錯,高可靠性系統會在NPC的交流輸出端與直流中性點之間并聯一組雙向晶閘管(TRIAC)或由繼電器構成的常開輔助通路。當內管失效時,激活輔助通路將負載直接旁路至中性點;若是更復雜的短路失效,則需結合快速熔斷器或固態斷路器強行切斷故障相的物理連接。

T-Type拓撲的降級演化: T-Type拓撲在降級容錯方面具有天然的結構優勢。T型逆變器的中性點支路具備獨立性。如果在中性點雙向開關(S2?, S3?)處發生故障,硬件重構僅需通過斷開串聯在中性點回路中的常閉繼電器(NC Relay)來徹底切除故障支路。此時,發生故障的這一相橋臂在物理上僅剩下上、下兩個主開關(S1? 和 S4?),完美等效為一個標準的兩電平(2L)半橋電路。這種演化不僅無需增加龐大的備用橋臂,還能極大限度地重用原有功率模塊的散熱與驅動資源。

5.3 軟件算法降維:SVPWM的空間矢量重映射

在硬件完成拓撲隔離后,核心控制器必須即時調整其調制策略。傳統的三電平空間矢量脈寬調制(SVPWM)依賴于27個離散的電壓矢量來合成理想的圓形旋轉磁場。而在降級模式下(例如A相降級為2L,而B、C相仍保持3L),可用的開關狀態集合發生了根本性的非對稱塌縮。

選擇性狀態屏蔽與空間重構: 最前沿的容錯控制普遍采用動態權重的有限集模型預測控制(FCS-MPC)或重構的SVPWM算法。控制器在軟件層面實施“選擇性狀態排除”(Selective State Exclusion)。以T-Type逆變器A相中性點開關失效為例,算法會在控制邏輯中永久屏蔽A相的‘O’(零電平)狀態,強迫A相只能在‘P’(+VDC?/2)和‘N’(?VDC?/2)狀態間跳轉。 在這種非對稱的混合調制(2L+3L運行)中,為了確保合成的三相線電壓依然保持嚴格的對稱正弦波形,消除負載端的直流偏磁偏置,控制器必須對參考電壓矢量進行重映射。然而,由于丟失了中電平狀態,系統合成最大電壓矢量的幾何邊界縮小,為了防止調制波形在六邊形邊界處發生嚴重的過調制失真,控制系統必須主動降低全系統的電壓利用率,將最大調制比(Modulation Index, MI)嚴格限制在原始正常狀態的 0.577 倍(即 1/3?)以內。這意味著逆變器進入了降壓降功率的跛行(Limp-home)模式。

5.4 零序電壓注入與中性點電位(NPV)強力平衡

在三電平逆變器運行中,由于上下兩個直流母線電容交替充放電,中性點電位(NPV)的漂移是一個固有的物理難題。在正常3L狀態下,SVPWM通過靈活調配成對出現的冗余小矢量(即作用時間相同但對中性點電流方向相反的矢量對)來維持直流電容的動態電壓平衡。 然而,在進入容錯降級模式后,由于大量開關狀態被禁用,用以平衡NPV的冗余小矢量極度匱乏,導致母線電容極易出現嚴重的電壓不平衡。如果任由其發展,未損壞的SiC管將承受超過額定值的過電壓。 為了在如此嚴苛的約束下鎖死中性點電位,軟件層面的容錯算法采用了重構零序電壓(Zero-Sequence Voltage, Vsn?)注入技術。在健康的3L系統中,加入的零序偏置電壓頻率通常為基波頻率的三倍(3×ffund?),以最大化直流電壓利用率。而在故障降級模式下,容錯控制器會在每一個開關周期重新計算相電壓的極值,并將零序電壓的注入頻率強制降頻至與基波頻率相同(1×ffund?)。這種基頻零序電壓注入策略,能夠在極度有限的矢量空間內,強行制造出持續且足夠的電荷補償電流,通過其它兩相仍然健康的3L橋臂對偏移的電容電荷進行反向抽取與補充,從而在不對稱的拓撲下奇跡般地實現了直流母線電壓的剛性平衡。這不僅挽救了殘存的功率半導體,還使得輸出電流的總諧波畸變率(THD)能夠重新被抑制到符合并網或驅動標準的3%以下。

6. 結論

高頻碳化硅(SiC)三電平逆變器代表了當前電力電子變換系統在功率密度與能效領域的最高水準。以BASiC Semiconductor(基本半導體)BMF540系列為代表的高端SiC功率模塊,在展現出極低寄生電感(30 nH)與千安級浪涌電流承載能力的同時,也凸顯了SiC材料微小熱容所帶來的脆弱短路耐受時間(< 2-3 μs)挑戰。

為了在如此嚴酷的工況下保障系統安全,傳統的保護范式已被徹底顛覆。基于微型羅氏線圈的高頻電磁測量與基于Kelvin源極寄生電感的 di/dt 積分技術,成功將短路檢測延遲壓縮至 100 ns 以下的納秒級區間;配合有源米勒鉗位與受控的軟關斷技術,有效遏制了極高 di/dt 帶來的致毀性過電壓。此外,通過融合智能故障診斷算法、微量硬件解耦干預以及SVPWM調制矢量的深度降維重映射,先進的容錯控制系統能夠在毫秒內將發生單管永久損壞的三電平橋臂重構為兩電平降級運行模式。在此模式下,輔以基頻零序電壓注入技術維持母線中性點平衡,系統能夠在保證電能質量的前提下安全平穩地實現降壓、降頻運行。這種將超快速底層硬件保護與高階軟件容錯自愈算法深度融合的體系化設計,徹底化解了SiC器件在復雜三電平拓撲中的應用風險,為下一代極端高可靠性電氣化應用鋪平了道路。

審核編輯 黃宇

-

逆變器

+關注

關注

304文章

5197瀏覽量

217214 -

SiC

+關注

關注

32文章

3818瀏覽量

69850 -

開關頻率

+關注

關注

2文章

427瀏覽量

22228 -

短路保護

+關注

關注

12文章

292瀏覽量

33846

發布評論請先 登錄

突破SiC模塊短路保護響應極限:基于源極寄生電感的 200ns 超快故障感知算法

SiLM8260ABCS-AQ 10A雙通道隔離驅動器,賦能電動汽車高可靠驅動

SiLM2648-AQ智能高邊開關:重新定義汽車電源的eFuse保護方案

SiC功率模塊的短路保護(Desat)響應速度優化:亞微秒級無誤觸發的實現

增強型電流控制VSG(CC-VSG)與高可靠SiC模塊協同的構網型變流器故障穿越與自保架構研究

傾佳電子碳化硅SiC MOSFET驅動特性與保護機制深度研究報告

高功率密度碳化硅MOSFET軟開關三相逆變器損耗分析

傾佳電子BTD5452R隔離型SiC碳化硅MOSFET門極驅動器米勒鉗位串擾抑制與DESAT短路保護的技術價值

基于SiC MOSFET的T型三電平數據中心UPS高效設計方案

高開關頻率下的SiC三電平逆變器短路保護與故障容錯機制研究

高開關頻率下的SiC三電平逆變器短路保護與故障容錯機制研究

評論