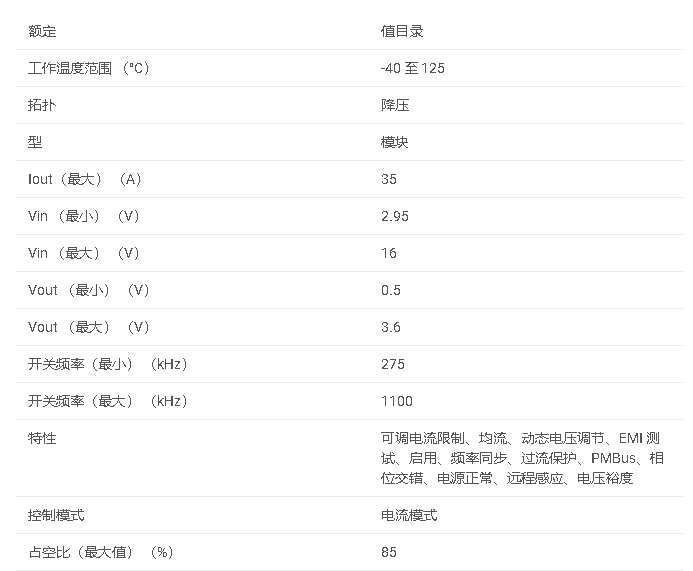

TPSM8D6C24:高集成DC/DC降壓模塊的深度解析

在電子設計領域,電源模塊的性能和可靠性至關重要。TPSM8D6C24作為一款高度集成、易于使用的非隔離式DC/DC降壓電源模塊,為數據中心、通信設備等眾多應用提供了強大的電源解決方案。本文將深入探討TPSM8D6C24的特性、工作原理、應用場景以及設計要點,幫助電子工程師更好地了解和應用這款產品。

文件下載:tpsm8d6c24.pdf

一、產品概述

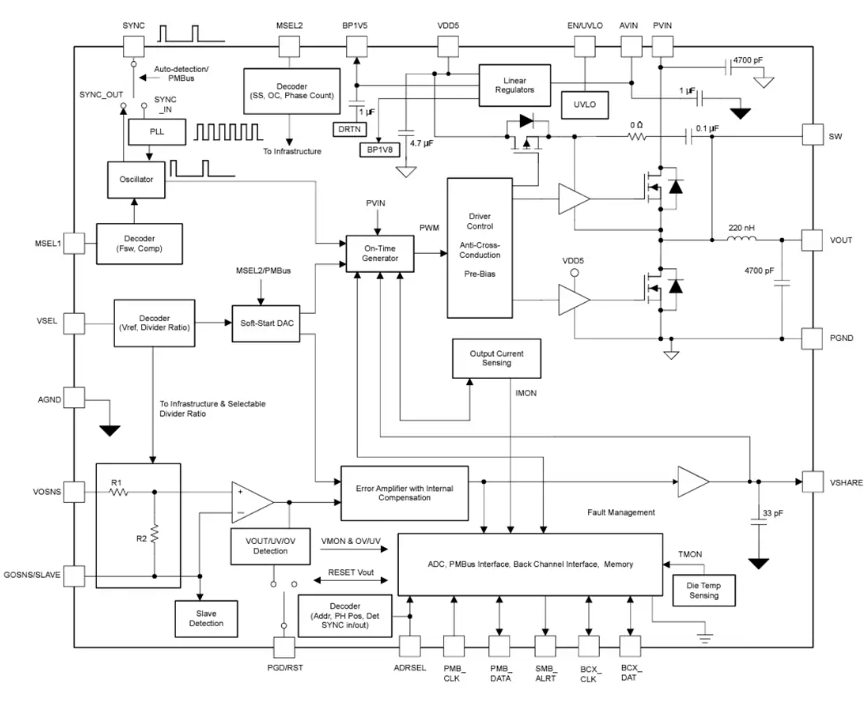

TPSM8D6C24能夠提供兩個35A的獨立輸出,或者一個堆疊的2相70A輸出,兩個模塊還可以堆疊實現4相140A輸出。它采用固定頻率的專有電流模式控制,具有多種可配置的功能和保護機制,通過PMBus接口實現便捷的數字配置和關鍵參數監測。

二、關鍵特性

2.1 輸入電壓范圍靈活

- 當PVIN連接到AVIN且使用內部LDO時,輸入電壓范圍為4.25V至16V;當PVIN和AVIN采用分離電源軌,或者在VDD5上使用外部偏置時,輸入電壓范圍可低至2.95V至16V。

- 這種靈活的輸入電壓范圍使得TPSM8D6C24能夠適應不同的電源環境,為設計帶來更多的可能性。

2.2 集成度高

內部集成了MOSFET、電感和基本無源元件,大大減少了外部元件的數量,簡化了設計過程,提高了系統的可靠性和穩定性。

2.3 輸出電壓范圍廣

輸出電壓范圍為0.5V至3.6V,通過引腳編程或PMBus配置可以輕松設置所需的輸出電壓,滿足不同負載的需求。

2.4 精確的控制和監測

采用平均電流模式控制,并具有可選的內部補償,能夠實現精確的輸出電壓調節。同時,通過PMBus接口可以實時監測輸出電壓、輸出電流和內部管芯溫度等關鍵參數,方便工程師進行系統監控和故障診斷。

2.5 豐富的保護功能

具備過流保護、過壓保護、欠壓保護、過溫保護等多種保護機制,能夠有效保護設備免受異常情況的損害,提高系統的可靠性和穩定性。

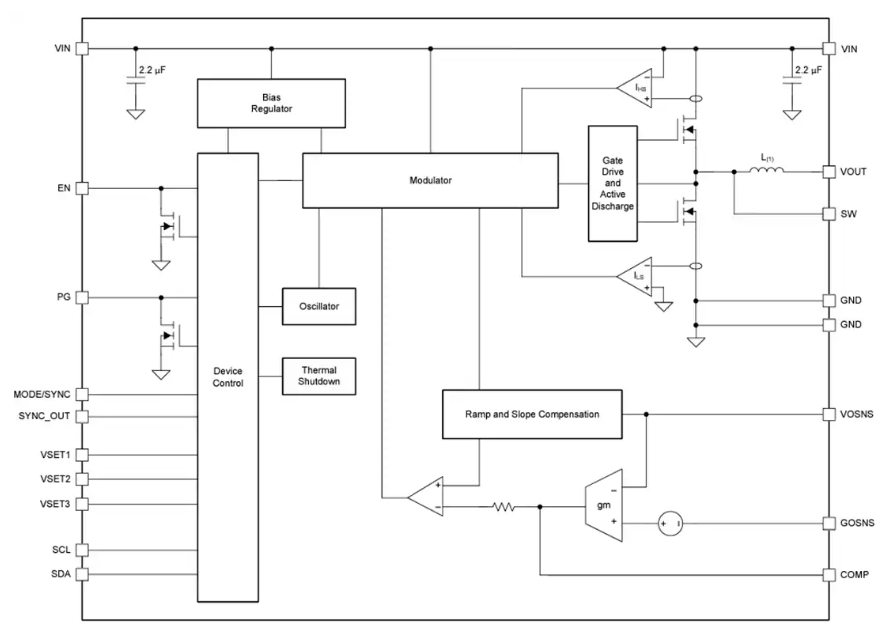

三、工作原理

3.1 平均電流模式控制

TPSM8D6C24采用平均電流模式控制架構,具有獨立可編程的電流誤差積分和電壓誤差積分回路。這種架構在不限制最小導通時間或最小關斷時間控制的情況下,提供了與峰值電流模式控制相似的性能,允許通過電流回路的增益選擇有效地設置斜率補償。

3.2 線性調節器

設備內部有三個線性調節器,從AVIN獲取電源,為內部電路提供合適的偏置電壓(1.5V、1.8V和5V)。VDD5調節器可以由外部4.75V至5.25V的電源供電,以減少內部功耗,提高效率。

3.3 輸入欠壓鎖定(UVLO)

提供四個獨立的UVLO功能,包括固定的AVIN UVLO、固定的VDD5 UVLO、可編程的PVIN UVLO和EN/UVLO引腳,為啟動控制提供了廣泛的靈活性。

3.4 輸出電壓設置和自適應電壓縮放(AVS)

初始輸出電壓可以通過VSEL引腳在AVIN上電時設置,之后可以通過PMBus通信進行更改。此外,還支持AVS和裕量調節功能,通過PMBus實現輸出電壓的動態調整。

四、應用場景

4.1 數據中心和服務器

在數據中心交換機、機架服務器等設備中,TPSM8D6C24能夠為ASIC、SoC、FPGA、DSP核心和I/O電壓提供穩定的電源供應,滿足高功率、高可靠性的需求。

4.2 通信設備

適用于有源天線系統、遠程無線電和基帶單元等通信設備,為其提供高效、穩定的電源解決方案。

4.3 自動化測試設備

在自動化測試設備中,TPSM8D6C24的精確控制和監測功能能夠確保測試設備的準確性和穩定性。

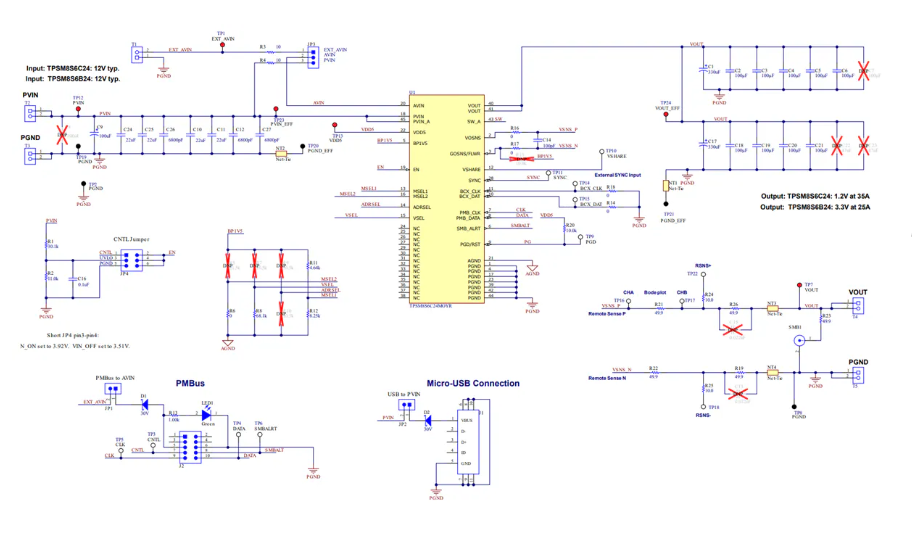

五、設計要點

5.1 引腳配置

TPSM8D6C24具有59個引腳,每個引腳都有特定的功能。在設計時,需要根據具體的應用需求正確配置引腳,例如GOSNS/FLWR引腳用于檢測設備是作為環路控制器還是環路跟隨器,VSEL引腳用于設置輸出電壓等。

5.2 輸入和輸出電容選擇

輸入電容需要足夠的容量和低ESR,以滿足高開關電流的需求,并提供最小的輸入電壓紋波。輸出電容的選擇要考慮輸出紋波要求和電壓環路的穩定性,通常需要結合電解電容和陶瓷電容來實現最佳性能。

5.3 軟啟動和軟停止設置

通過PMBus可編程的軟啟動時間(TON_RISE)和軟停止時間(TOFF_FALL)可以控制輸出電壓的上升和下降速率,減少浪涌電流和電壓過沖,保護設備和負載。

5.4 頻率同步和相位交錯

內部振蕩器可以與外部時鐘同步(SYNC IN)或輸出時鐘以同步其他設備(SYNC out),支持多軌交錯和多相操作的相移時鐘。在多相堆疊配置中,需要合理設置相位偏移,以實現電流共享和減少紋波。

5.5 布局注意事項

布局對于電源模塊的性能至關重要。需要最小化快速開關電壓或電流路徑形成的環路面積,將輸入旁路電容盡可能靠近PVIN和PGND引腳,將信號組件靠近相關引腳,并保持VOSNS和GOSNS線路作為緊密耦合的差分對,避免受到開關噪聲的干擾。

六、總結

TPSM8D6C24作為一款高性能的DC/DC降壓電源模塊,具有靈活的輸入輸出范圍、高集成度、精確的控制和豐富的保護功能,適用于多種應用場景。在設計過程中,工程師需要根據具體需求合理配置引腳、選擇合適的電容、設置軟啟動和軟停止時間,并注意布局的合理性,以充分發揮TPSM8D6C24的性能優勢,實現高效、穩定的電源設計。

希望本文能夠為電子工程師在使用TPSM8D6C24進行電源設計時提供有益的參考。在實際應用中,還需要根據具體情況進行進一步的測試和優化,以確保系統的可靠性和性能。如果你在設計過程中遇到任何問題,歡迎在評論區留言交流。

-

電源設計

+關注

關注

31文章

1819瀏覽量

69689

發布評論請先 登錄

2.95V至16V、雙路35A或單路70A、最多可堆疊4個相位、PMBus? 降壓電源模塊TPSM8D6C24數據表

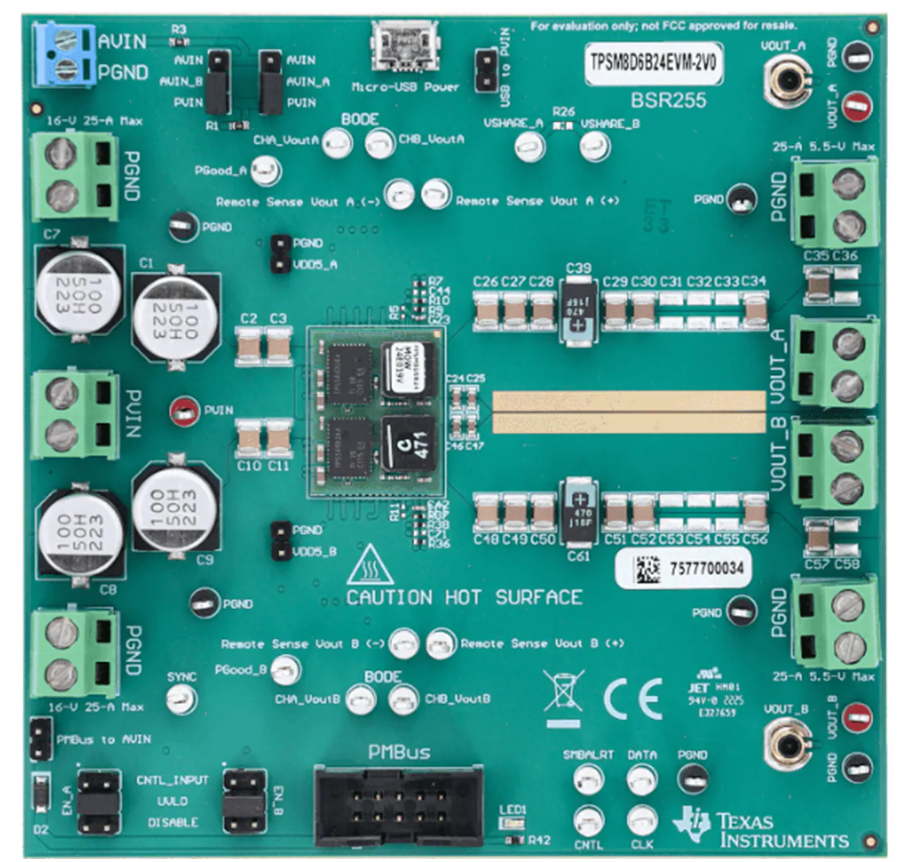

TPSM8D6C24EVM-2V0電源模塊評估模塊用戶指南

TPSM8D6C24 2.95V 至 16V 輸入、雙通道 35A、PMBus? 電源模塊數據手冊

Texas Instruments TPSM8287Axx DC-DC降壓電源模塊數據手冊

TPSM8S6C24SEVM-1PH評估模塊技術解析與設計指南

TPSM8D6B24EVM-2V0電源模塊評估模塊技術解析

TPSM8D6C24:高集成DC/DC降壓模塊的深度解析

TPSM8D6C24:高集成DC/DC降壓模塊的深度解析

評論