我們能將碳化硅 (SiC) 襯底厚度推進到多薄而不影響性能?這是我們幾十年來一直在追問的問題,同時我們也在不斷突破碳化硅 (SiC) 材料性能的極限——因為我們知道下一代碳化硅 (SiC) 器件技術正依賴于此。

這篇文章探討了 Wolfspeed 在碳化硅 (SiC) 襯底的成本、可擴展性和質量等最嚴峻挑戰方面的研究,包括了碳化硅 (SiC) 外延和襯底厚度如何影響高電壓器件。

該篇文章中文版刊登于《化合物半導體》雜志 2025 年第 10/11 月刊https://www.compoundsemiconductorchina.net/issue_show.asp。

英文版原文敬請訪問https://compoundsemiconductor.net/article/121811/Thick_homoepitaxy_on_200_mm_SiC。

200mm 碳化硅襯底厚度與外延厚度的多維度影響

碳化硅 (SiC) 襯底的成本需要降下來。但是,如果我們對這種基礎材料的厚度施加限制的話,會阻礙這些努力嗎?

作者: THOMAS KUHR,WOLFSPEED 公司工藝制程開發工程高級總監

碳化硅 (SiC) 正受益于電動汽車的蓬勃發展。基于這種寬禁帶半導體的功率器件的采用,使得更高效率的電子設備能夠將系統損耗降低 80% 甚至更多。然而,盡管這令人印象深刻,但這只是其好處的冰山一角。和其他寬禁帶材料一樣,碳化硅 (SiC) 還具有高熱導率和優異的飽和漂移速度,使得用這種材料制成的器件能夠在高電場密度下工作,并應用于許多技術領域,包括高電壓直流、脈沖功率和固態變壓器。使用可處理高達 10 kV 的單個碳化硅 (SiC) MOSFET 芯片,甚至更高電壓的雙極器件,為設計人員提供了簡化系統并在許多應用中降低電阻加熱損耗的機會。

隨著碳化硅 (SiC) 持續展現出優于現有技術的改進性能,其較高的成本正受到重點關注。在半導體行業內,應對這一挑戰的常見解決方案是轉向更大尺寸的晶圓,從而將固定的加工成本分攤到更多的器件上。這一轉變正在進行中,碳化硅 (SiC) 襯底目前正經歷從 150 mm 直徑向 200 mm 直徑的轉型。然而,與隨著直徑增加而增加晶圓厚度的硅 (Si) 行業不同,碳化硅 (SiC) 行業正在考慮為 200 mm 直徑晶圓保留現今 150 mm 直徑晶圓所使用的 350 μm 厚度。

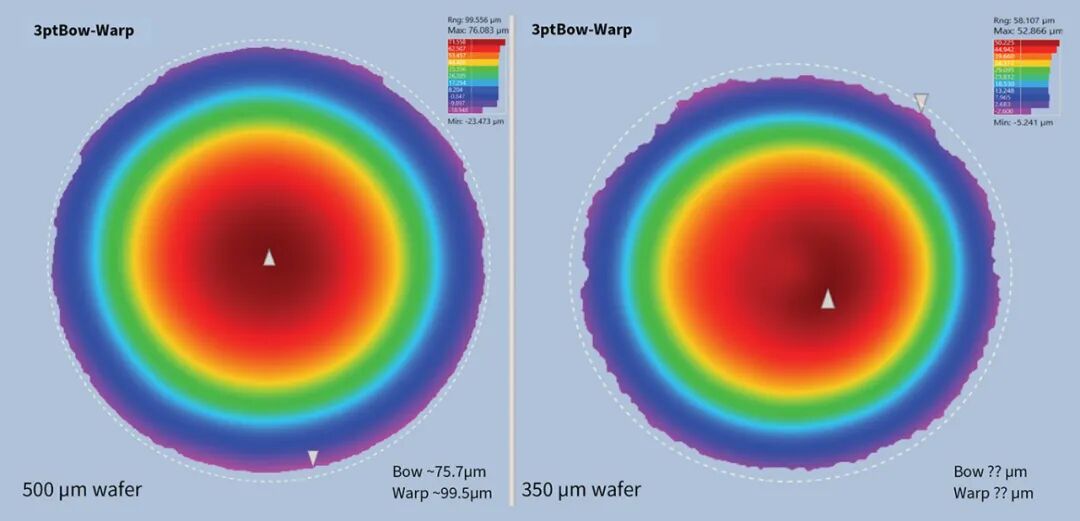

圖 1. 500 μm 厚度(左)和 350 μm 厚度(右)的晶圓形狀圖比較。請注意,在這兩種情況下都未生成完整的圖譜,不過左側的掃描更完整。350 μm 厚度晶圓的彎曲度(Bow)和翹曲度(Warp)明顯更高,超出了當前工具配置的測量范圍。

Wolfspeed 作為全球碳化硅 (SiC) 襯底和器件的領先企業,我們一直在研究,當采用 350 μm 厚度和 500 μm 厚度的晶圓時,不同厚度條件下的外延層在質量上有何差異。用于制造 650 V 和 1200 V 器件的“薄” 碳化硅 (SiC) 層的生長,往往不會因溫度情況或襯底與外延膜層之間摻雜差異而產生顯著應力。然而,當外延層更厚且摻雜濃度更低時——這是更高擊穿電壓器件的兩個關鍵要求——應力會被放大,產生新的缺陷并引發晶圓形狀問題。

此外,外延缺陷的尺寸和面積也會增加,因為它們通常在襯底界面處或附近產生,并隨著薄膜的生長而相應增大。更大的應力和更大的缺陷,加上高電壓器件通常尺寸更大,這些因素的復合效應導致晶圓的可使用面積大大降低,從而導致芯片良率降低和每個器件的成本升高。

圖 2. 用于估算 500 μm 厚度 200 mm 直徑襯底上生長 115 μm 厚度外延層的器件可用面積的拼接圖像圖(帶有初步墨跡標記)。使用了任意的 5 mm x 5 mm 網格進行可視化。請注意,并非所有缺陷都被正確識別,但可以看到宏觀缺陷(如三角形缺陷)的面積效應,如插入圖片所示。

可能會出現什么問題?

為了加深我們對更薄襯底和更厚外延層之間相互作用的理解,我們研究了三種不同厚度的同質外延層的性能對比。外延層在 350 μm 厚度和 500 μm 厚度的 200 mm SiC 襯底上進行生長,并采用了兩種已商用的反應器平臺。誠然,進行這種評估的最佳方法是將單個晶錠切割成多個不同厚度的襯底,因為這樣可以標準化襯底缺陷的起始點。但在這項工作中,我們使用了內部生產的晶圓因為它們已經可獲取的。我們根據特定的器件要求選擇了摻雜和厚度目標,旨在達到所需擊穿電壓下的最低電阻,并且通過利用我們標準生產流程中的一套測量方法,我們已經能夠確定是否存在任何潛在的制造限制。

外延生長過程中的一個擔憂是晶圓形狀在高溫生長條件下的穩定性。晶圓形狀在室溫和超過 1600 °C 時可能不同,更薄的晶圓可能會不可預測地改變形狀。任何變化都會通過厚度或摻雜不均勻性對生長產生不利影響。在最壞的情況下,晶圓可能會在加工過程中破裂或從承載器上彈出。

我們的結果消除了將晶圓厚度從 500 μm 減少到 350 μm 時的這種擔憂。如果說有什么不同的話,更薄的晶圓反而改善了薄膜厚度和摻雜均勻性,盡管這可能取決于反應器設備的設計。請注意,我們需要進行更多輪的生長實驗才能建立具有統計顯著性的結論。然而,我們的初步研究表明,在外延生長過程中使用更薄的 200 mm 晶圓不存在相關問題。

由于薄型和厚型碳化硅 (SiC) 器件在加工化學和器件設計方面的相似性,我們的器件制造團隊希望所有外延晶圓的表面狀態相似。為了驗證是否如此,我們使用原子力顯微鏡(AFM)和共聚焦成像技術仔細檢查了我們的材料。用于測量短程粗糙度的 AFM 顯示,粗糙度性能相匹配,薄膜和厚膜的平均粗糙度(Ra)均小于 0.2 nm。根據共聚焦成像,厚膜的長程粗糙度大于薄膜,平均粗糙度(Ra)約為 0.6 nm。

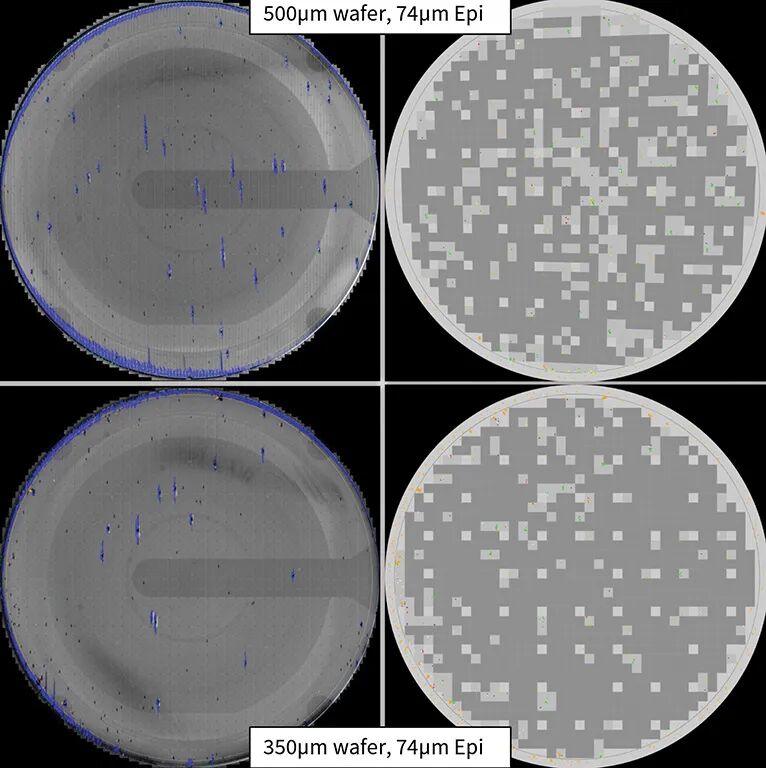

圖 3. 用于估算 500 μm 厚度和 350 μm 厚度 200 mm 襯底上生長 74 μm 厚度外延層的器件可用面積的拼接圖像圖(帶有初步墨跡標記)。顯示了 75-85% 的 5x5 可用區域。

這些發現與襯底厚度無關,盡管在共聚焦成像尺度上,稍微多一點的粗糙度在空間分布上略廣一些。這表明,就像摻雜和厚度均勻性一樣,表面粗糙度相對于晶圓厚度而言可能不是一個問題。然而,有必要減少厚膜的表面粗糙度,并進一步改進空間依賴性。

由于更厚的外延層會導致更大的缺陷和更高的薄膜應力,選擇更薄的襯底會加劇應力問題。因此,當在更薄的襯底上生長更厚的外延層時發現形狀問題,我們并不感到驚訝。使用直徑 200 mm 的碳化硅 (SiC),在 500 μm 厚度的襯底上生長 13 μm 厚度的外延層會導致 20-40 μm 的彎曲度 (Bow);將厚度增加到 115 μm,并將摻雜濃度降至 10^15 cm^-3 的中段,彎曲度會增加至 80 μm 左右。如果然后將襯底減薄至 350 μm,彎曲度會增加至 100 μm 以上,從而在器件制造過程中帶來處理錯誤和晶圓破裂的風險。雖然 100 μm 的晶圓彎曲度與離子注入過程中可能發生的數百 μm 彎曲度相比似乎微不足道,但并非所有的制造工具都能從那個起點開始處理。我們的觀點是,如果打算采用僅 350 μm 厚度的襯底來生長更厚的外延層,可能需要做更多的工作來補償晶圓形狀問題。

碳化硅 (SiC) 最大的缺點是其晶體生長過程中固有的缺陷性以及相對容易形成缺陷。在晶錠生長過程中產生并存在于襯底中的缺陷,要么通過生長的延續,要么通過轉化為其他類型的缺陷,傳播到外延層中。缺陷的來源可能是微管、穿透位錯 (threading dislocations)、堆垛層錯 (stacking faults)、表面制備造成的亞表面損傷,或者僅僅是清潔不充分導致的臟污表面;更一般地說,任何破壞晶格自然堆疊的因素都會導致缺陷。例如,一種稱為“三角形”的常見缺陷——它是一種晶體堆疊紊亂,表現為生長表面可見的三角形——其尺寸隨著外延生長而增大,從外延生長 13 μm 時的 0.4 mm 長增加到 115 μm 厚薄膜時的 3.2 mm。您可能會想,這有什么大不了的,因為器件通常尺寸為 25 mm^2 或更大,所以一個三角形缺陷應該只影響一兩個芯片。

正如我們已經提到的,薄膜應力隨著厚度以及薄膜與襯底之間的摻雜差異而增加。因此,加上碳化硅 (SiC) 基平面位錯 (basal plan dislocations) 非常低的形成能 (formation energy),諸如三角形之類的缺陷有可能產生基平面位錯。這些位錯從源缺陷處出現,沿著晶圓垂直滑移。因此,一個最初只影響一兩個器件的缺陷現在可能會影響五到十倍的芯片,從而大幅降低良率。

好消息是,通過精細管理外延生長過程中晶圓上的溫度分布,可以減少過度的薄膜應力。即使這種收益是以增加晶圓彎曲度為代價,這也使得能夠處理更薄的晶圓而不會增加薄膜缺陷。

不巧地是,并非我們所有的測量都特別順利。由于掃描不完整,我們最初關于帶有厚外延層的薄晶圓的最大彎曲度數值是不正確的。我們花了一點時間和精力,通過微小調整,克服了這個簡單工具限制,糾正了這個錯誤。

圖 4. 準備進行封裝的 10 kV 裸芯片。

我們還遇到了與缺陷自動檢測相關的問題,原因是檢測算法是針對不同尺寸的缺陷或更光滑的表面進行訓練的。這意味著我們將應用于更薄外延層的準確的缺陷分類和數據采集方法,用在更厚外延薄膜的初期階段會遇到困難。

我們遇到的與晶圓彎曲度掃描和缺陷檢測相關的問題并非不可克服。就缺陷而言,它們甚至與襯底厚度無關。然而,在這些技術能夠服務于大批量制造工藝之前,需要進行干預和開發。

總而言之,更薄的晶圓會導致形狀問題,必須在外延生長之前或生長期間解決。但如果溫度分布和應力得到有效管理,額外的應力誘導缺陷應該不會成為問題。這聽起來還不錯,除了預測的良率看起來并不那么高,而且成本仍然很高。

為了說明這一點,我們考慮用于 1200 V MOSFET 晶圓的 5 mm x 5 mm 器件。在這種情況下,可用面積超過 90%。但如果需要更厚的外延層,由于增大的面積效應,可用面積會下降到 70% 左右。如果器件尺寸增加,根據簡單的泊松統計,可用面積會進一步下降。現在,那片對于 1200 V MOSFET 可用面積超過 90% 的碳化硅 (SiC) 晶圓,對于 10 kV MOSFET 而言可能低于 40%,而這甚至是在外延片進入器件制造廠之前。

圖 5. 高性能半橋 10 kV、 50 mΩ 全碳化硅 (SiC) 功率模塊。

可行的厚度?

讓我們回到最初的問題:減薄碳化硅 (SiC) 襯底是否會限制使用更厚外延層制造高電壓器件的能力?嗯,也許吧……也許不會。很明顯,關鍵是要控制晶圓形狀并管理外延生長應力,以防止器件制造過程中的復雜情況,從而保持低成本。為了支持這些努力,需要進行調整以確保測量和計量方法與當前最佳實踐和行業標準保持連續性。但同樣非常重要的是,碳化硅 (SiC) 襯底制造商需要繼續專注于減少缺陷。如果沒有更低的缺陷濃度,器件尺寸和能力或器件良率將繼續需要權衡取舍,并且無論外延生長過程如何優化,成本都將保持高位。

最后,推動碳化硅 (SiC) 襯底變得更薄的努力將繼續下去,因為降低其成本仍然是一個巨大的動力。在此背景下,創新者將找到處理晶圓形狀的方法,襯底制造商將繼續降低缺陷密度,有助于提高器件良率并削減成本。

出于純粹的技術需求,對于更高電壓器件的使用將繼續提升,采用 10 kV MOSFET 或更高電壓的 IGBT 將為其鋪平道路。碳化硅 (SiC) 變革正逢其時!

此文章的中文翻譯僅供參考,相關信息請以英文原稿為準。

關于 Wolfspeed, Inc.

Wolfspeed(美國紐約證券交易所上市代碼:WOLF)在全球范圍內推動碳化硅技術采用方面處于市場領先地位,這些碳化硅技術為全球最具顛覆性的創新成果提供了動力支持。作為碳化硅領域的引領者和全球最先進半導體技術的創新者,我們致力于為人人享有的美好世界賦能。Wolfspeed 通過面向各種應用的碳化硅材料、功率模塊、分立功率器件和功率裸芯片產品,助您實現夢想,成就非凡(The Power to Make It Real)。了解更多詳情,敬請訪問 www.wolfspeed.com。

-

SiC

+關注

關注

32文章

3833瀏覽量

69944 -

襯底

+關注

關注

0文章

39瀏覽量

9634 -

碳化硅

+關注

關注

26文章

3526瀏覽量

52623 -

Wolfspeed

+關注

關注

0文章

102瀏覽量

8904

原文標題:200mm 碳化硅襯底厚度與外延厚度的多維度影響

文章出處:【微信號:WOLFSPEED,微信公眾號:WOLFSPEED】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

Soitec 發布首款 200mm SmartSiC? 優化襯底,拓展碳化硅產品組合

【新啟航】如何解決碳化硅襯底 TTV 厚度測量中的各向異性干擾問題

【新啟航】碳化硅襯底 TTV 厚度測量設備的日常維護與故障排查

激光干涉法在碳化硅襯底 TTV 厚度測量中的精度提升策略

碳化硅襯底 TTV 厚度測量數據異常的快速診斷與處理流程

【新啟航】國產 VS 進口碳化硅襯底 TTV 厚度測量儀的性價比分析

【新啟航】碳化硅襯底 TTV 厚度測量中表面粗糙度對結果的影響研究

【新啟航】探針式碳化硅襯底 TTV 厚度測量儀的操作規范與技巧

探針式碳化硅襯底 TTV 厚度測量儀的操作規范與技巧

碳化硅襯底 TTV 厚度測量中邊緣效應的抑制方法研究

碳化硅襯底 TTV 厚度不均勻性測量的特殊采樣策略

【新啟航】碳化硅襯底 TTV 厚度不均勻性測量的特殊采樣策略

【新啟航】碳化硅 TTV 厚度與表面粗糙度的協同控制方法

【新啟航】碳化硅外延片 TTV 厚度與生長工藝參數的關聯性研究

200mm碳化硅襯底厚度與外延厚度的多維度影響

200mm碳化硅襯底厚度與外延厚度的多維度影響

評論