汽車級時鐘緩沖器與乘法器 CDCS504-Q1 設計指南

引言

在汽車電子應用中,時鐘信號的精準處理至關重要。CDCS504-Q1 作為一款專為汽車應用設計的時鐘緩沖器和時鐘乘法器,憑借其出色的性能和易于使用的特點,在相關領域備受關注。本文將深入剖析 CDCS504-Q1 的特性、應用及設計要點,為電子工程師們提供全面的設計參考。

文件下載:cdcs504-q1.pdf

一、CDCS504-Q1 特性解析

(一)汽車級認證與寬溫范圍

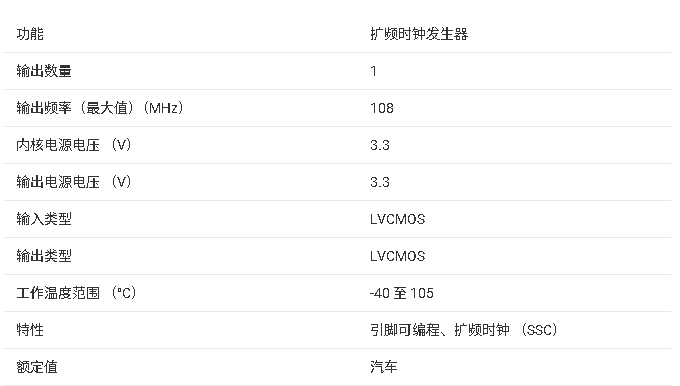

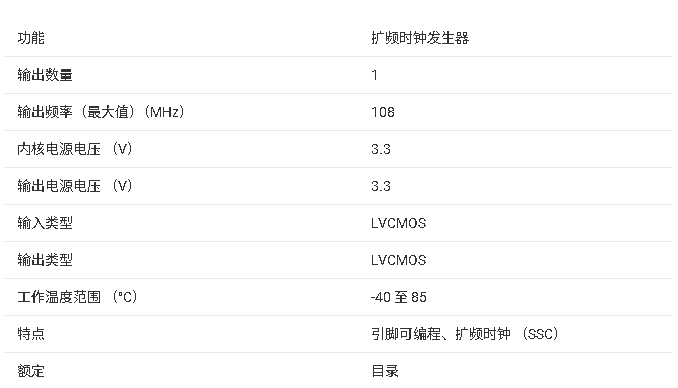

CDCS504-Q1 通過了 AEC-Q100 測試,符合汽車應用標準。其環境工作溫度范圍為 -40°C 至 105°C,能在各種惡劣的汽車環境中穩定工作。同時,該器件的 HBM ESD 分類等級為 H2,CDM ESD 分類等級為 C3B,具備良好的靜電防護能力。

(二)靈活的時鐘乘法與輸出控制

它是時鐘乘法器,可通過一個外部控制引腳在 x1 或 x4 之間選擇輸出頻率。此外,還能通過控制引腳實現輸出禁用功能,方便工程師根據實際需求靈活配置。

(三)低功耗與小封裝設計

采用單一 3.3V 電源供電,功耗較低。并且采用 8 引腳 TSSOP 封裝,占用空間小,適合對空間要求較高的汽車電子設計。

二、應用場景

CDCS504-Q1 主要應用于需要時鐘乘法的汽車應用中,例如汽車放大器和信息娛樂系統。當應用中沒有可用的 MCLK 時,它可以與 TAS6424-Q1 四通道 D 類數字輸入音頻放大器完美配合,為系統提供穩定的時鐘信號。

三、詳細技術參數

(一)絕對最大額定值

| 參數 | 最小值 | 最大值 | 單位 |

|---|---|---|---|

| VDD(電源電壓) | -0.5 | 4.6 | V |

| VIN(輸入電壓) | -0.5 | 4.6 | V |

| Vout(輸出電壓) | -0.5 | 4.6 | V |

| IIN(輸入電流) | - | 20 | mA |

| Iout(連續輸出電流) | - | 50 | mA |

| TJ(最大結溫) | - | 125 | °C |

| Tstg(存儲溫度) | -65 | 150 | °C |

(二)ESD 額定值

| 類型 | 數值 | 單位 |

|---|---|---|

| 人體模型(HBM) | ±1500 | V |

| 帶電器件模型(CDM) | ±750 | V |

(三)推薦工作條件

| 參數 | 最小值 | 標稱值 | 最大值 | 單位 |

|---|---|---|---|---|

| VDD(電源電壓) | 3 | - | 3.6 | V |

| fIN(輸入頻率,FS = 0) | 2 | - | 27 | MHz |

| fIN(輸入頻率,FS = 1) | 2 | - | 27 | MHz |

| VIL(LVCMOS 低電平輸入電壓) | - | 0.3 × VDD | - | V |

| VIH(LVCMOS 高電平輸入電壓) | - | VDD | - | V |

| VIT(LVCMOS 輸入電壓閾值) | - | 0.5 × VDD | - | V |

| CLOAD(輸出負載測試,LVCMOS) | - | 15 | pF | |

| IOH/IOL(輸出電流) | - | ±12 | mA | |

| TA(工作環境溫度) | -40 | - | 105 | °C |

(四)電氣特性

在推薦工作溫度范圍內,該器件具有一系列電氣特性,例如:

- 當 fin = 3.072 MHz 且 FS = 1 時,器件電源電流典型值為 24 mA。

- 輸出頻率方面,FS = 0 時為 2 - 27 MHz,FS = 1 時為 8 - 108 MHz。

四、功能模式與工作原理

(一)功能模式

CDCS504-Q1 的輸出狀態和頻率由引腳 7(OE)和引腳 5(FS)控制。當 OE 為低電平時,輸出為三態;當 OE 為高電平時,輸出時鐘信號,輸出頻率取決于 FS 的狀態。FS 為高電平時啟用頻率 ×4 模式,FS 為低電平時輸出頻率等于輸入頻率。

(二)工作原理

該器件是 LVCMOS 輸入時鐘緩沖器,輸入信號由鎖相環(PLL)處理。PLL 的輸出頻率可以等于輸入頻率或乘以 4,從而使器件能夠生成 2 MHz 至 108 MHz 的輸出頻率。

五、設計與應用要點

(一)電源設計

CDCS504-Q1 需要 3.3V 電源供電,在設計電源電路時,要確保電源的穩定性和純凈度,可在 VDD 引腳附近放置一個 0.01μF 的旁路電容,以減少電源噪聲的影響。

(二)布局設計

由于該器件的典型供電電流僅為 20 mA,熱設計方面沒有太大挑戰。在布局時,要注意輸入輸出引腳的布線,避免信號干擾。可參考文檔中的布局示例進行設計。

(三)應用曲線參考

在不同的工作模式和溫度條件下,器件的輸出周期抖動會有所不同。例如,在 X1 模式下,8 MHz 輸入和輸出且 VDD = 3.3V 時,典型的周期抖動與溫度的關系可參考相關應用曲線。工程師可以根據這些曲線來評估器件在不同環境下的性能。

(四)WEBENCH 工具輔助設計

借助 WEBENCH? 電源設計工具,工程師可以輕松創建自定義設計。只需輸入輸入電壓、輸出電壓和輸出電流要求,即可優化設計的效率、尺寸和成本等關鍵參數。該工具還能提供定制化的原理圖、實時定價和組件可用性信息,同時支持電氣和熱仿真等功能,方便工程師進行全面的設計驗證。

六、總結

CDCS504-Q1 作為一款專門為汽車應用設計的時鐘緩沖器和乘法器,具有豐富的功能和出色的性能。在實際設計過程中,工程師們需要充分了解其特性和參數,合理運用電源設計、布局設計和輔助工具等手段,以確保設計的穩定性和可靠性。你在使用 CDCS504-Q1 進行設計時,遇到過哪些挑戰呢?歡迎在評論區分享你的經驗和見解。

-

汽車電子

+關注

關注

3045文章

8956瀏覽量

172796 -

時鐘緩沖器

+關注

關注

2文章

270瀏覽量

51910

發布評論請先 登錄

MPY600 具有負載驅動功能的乘法器

使用verilogHDL實現乘法器

乘法器原理_乘法器的作用

CDCL6010 1.8V 11輸出時鐘乘法器、分配器、抖動消除器和緩沖器數據表

CDCS503帶可選SSC的時鐘緩沖器/時鐘乘法器數據表

?CDCS503-Q1 時鐘緩沖器/時鐘倍頻器技術文檔總結

汽車級時鐘緩沖器與乘法器 CDCS504-Q1 設計指南

汽車級時鐘緩沖器與乘法器 CDCS504-Q1 設計指南

評論