PCM3500:低功耗16位調制解調器編解碼器的卓越之選

在電子設備不斷追求小型化、低功耗和高性能的今天,編解碼器(CODEC)作為連接模擬世界和數字世界的橋梁,其性能的優劣直接影響著整個系統的表現。PCM3500作為一款專為調制解調器模擬前端(AFE)和語音處理應用設計的低功耗16位編解碼器,憑借其出色的性能和豐富的功能,成為了眾多便攜式設備和通信系統的理想選擇。

文件下載:pcm3500.pdf

一、產品概述

PCM3500集成了調制解調器或語音編解碼器所需的所有功能,包括Δ - Σ數模轉換器(DAC)和模數轉換器(ADC)、輸入抗混疊濾波器、用于直流阻塞的數字高通濾波器以及輸出低通濾波器。它支持高達56kbps的操作,采樣頻率范圍為7.2kHz至26kHz,動態范圍在(f{S}=8kHz)、(f{IN}=1kHz)時典型值為88dB。系統時鐘為(512f_{S}),支持主從模式操作,具有片上晶體振蕩器電路、ADC到DAC的回環模式以及時隙模式,可在單個串行接口上支持多達四個編解碼器。此外,它還具備低功耗特性,掉電模式下典型電流僅為60μA,電源電壓范圍為單+2.7V至+3.6V,采用SSOP - 24小型封裝,非常適合便攜式應用。

二、關鍵特性分析

(一)高精度轉換

PCM3500采用16位Δ - Σ DAC和ADC,為調制解調器模擬前端提供了高精度的信號轉換能力。在常見的操作條件下,其分辨率可達16位,能夠滿足大多數應用對信號精度的要求。在直流精度方面,輸入電壓增益誤差、失調誤差以及輸入電阻等參數都表現出色,保證了信號在轉換過程中的準確性。在交流精度方面,總諧波失真加噪聲(THD + N)、動態范圍、信噪比等指標也顯示出了其優秀的性能,能夠有效抑制噪聲和失真,提供清晰、純凈的信號。

(二)靈活的工作模式

- 主從模式:通過M/S輸入(引腳6)可以選擇主模式或從模式。在從模式下,FS和BCK引腳作為輸入,適合由DSP或控制器生成時鐘信號的應用;在主模式下,FS和BCK作為時鐘輸出,由PCM3500根據系統時鐘輸入生成,內部管理時鐘的時序和相位關系,提供最佳的同步性能。

- 時隙模式:通過TSC輸入(引腳7)可以啟用或禁用時隙模式。時隙模式定義了一個64位長的幀,由四個16位的時隙組成,每個時隙對應一個編解碼器。這種模式允許在單個4線串行總線上共享多達四個編解碼器,提高了系統的集成度和資源利用率。

- 回環模式:通過LOOP輸入(引腳19)可以啟用ADC到DAC的回環模式,該模式主要用于診斷測試和系統調整。在回環模式下,ADC的數據直接饋送到DAC輸入,同時串行接口仍可正常工作,方便主機在DOUT引腳讀取ADC數據。

(三)低功耗設計

PCM3500的低功耗特性使其成為便攜式應用的理想選擇。它可以在+2.7V至+3.6V的電源電壓下工作,并且具有集成的掉電模式。在掉電模式下,當系統時鐘移除時,典型電源電流僅為60μA,大大降低了系統的功耗,延長了電池續航時間。

三、系統時鐘與復位/掉電

(一)系統時鐘

PCM3500需要一個系統時鐘來操作數字濾波器和Δ - Σ數據轉換器。系統時鐘可以由外部主時鐘提供,也可以使用片上晶體振蕩器電路生成。系統時鐘必須以采樣頻率(f_{S})的512倍運行,采樣頻率范圍為7.2kHz至26kHz,對應的系統時鐘頻率范圍為3.6864MHz至13.312MHz。在選擇時鐘源時,無論是外部時鐘還是晶體振蕩器,都應確保時鐘信號的穩定性和低噪聲,以獲得PCM3500的最佳動態性能。

(二)復位與掉電

PCM3500支持上電復位、外部復位和掉電操作。上電復位由內部電路在電源上電時自動執行,外部復位通過PDWN輸入(引腳20)實現。在復位過程中,DAC輸出被強制為AGND,ADC輸出被強制為高阻抗狀態,復位完成后,DAC和ADC輸出需要一定的延遲才能輸出有效信號或數據。掉電模式通過設置(overline{PDWN} = '0')啟用,在掉電模式下,移除系統時鐘可使電流消耗最小化。

四、串行接口

PCM3500的串行接口是一個4線同步串行端口,包括FS(引腳9)、BCK(引腳8)、DIN(引腳10)和DOUT(引腳11)。FS作為幀同步時鐘,BCK作為位時鐘,DIN用于向DAC寫入16位數據,DOUT用于輸出ADC的16位數據。串行接口支持主從模式操作,并且在不同模式下,FS和BCK的輸入輸出方向會相應改變。在數據傳輸過程中,需要嚴格遵循接口的時序要求,以確保數據的準確傳輸。例如,在從模式下,BCK周期、脈沖寬度以及FS的相關時序參數都有明確的規定,這些參數的準確設置對于系統的正常運行至關重要。

五、應用電路設計

(一)基本電路連接

在基本電路連接中,需要注意電源旁路和參考去耦電容的使用。(V{COM})、(V{REF}1)和(V{REF}2)引腳需要通過電容接地進行去耦,DAC輸出(V{OUT})和ADC輸入(V_{IN})應與外部電路進行交流耦合。同時,為了保證系統的穩定性和性能,應合理選擇電容的類型和參數。

(二)PCB布局

PCB布局對于PCM3500的性能也有著重要影響。推薦采用分割接地平面的布局方式,將模擬和數字部分分開,PCM3500應完全位于模擬部分。電源引腳應使用寬銅跡線或電源平面直接連接到+2.7V至+3.6V的模擬電源,并且電源旁路和參考去耦電容應盡可能靠近PCM3500放置。數字連接應盡量短而直接,以減少高頻輻射和耦合。此外,可以在系統時鐘、FS、BCK和FSO線路中串聯電阻,以減少時鐘邊緣的過沖和輻射發射。

(三)軟件調制解調器應用

PCM3500非常適合軟件調制解調器應用,它可以與數據訪問裝置(DAA)和主機CPU配合使用,提供完整的調制解調器功能。DAA提供了編解碼器與兩線電話線之間的接口,主機CPU執行調制解調器軟件代碼,實現數據泵和監督功能。在實際應用中,需要根據具體的需求和系統要求,合理配置PCM3500的參數和工作模式,以確保調制解調器的性能和穩定性。

六、總結與展望

PCM3500以其高精度的信號轉換、靈活的工作模式、低功耗設計以及豐富的應用功能,為調制解調器和語音處理應用提供了一個優秀的解決方案。在實際設計過程中,電子工程師需要充分理解其各項特性和工作原理,合理進行電路設計和布局,以充分發揮其性能優勢。隨著電子技術的不斷發展,我們可以期待PCM3500在更多的領域得到應用,并且在性能和功能上不斷得到提升,為電子設備的發展做出更大的貢獻。

各位工程師朋友,你們在使用PCM3500的過程中遇到過哪些問題或有什么獨特的經驗呢?歡迎在評論區分享交流。

-

低功耗

+關注

關注

12文章

3438瀏覽量

106685 -

PCM3500

+關注

關注

0文章

3瀏覽量

8423

發布評論請先 登錄

CML推出DTMF編解碼器/FSK調制解調器復合IC

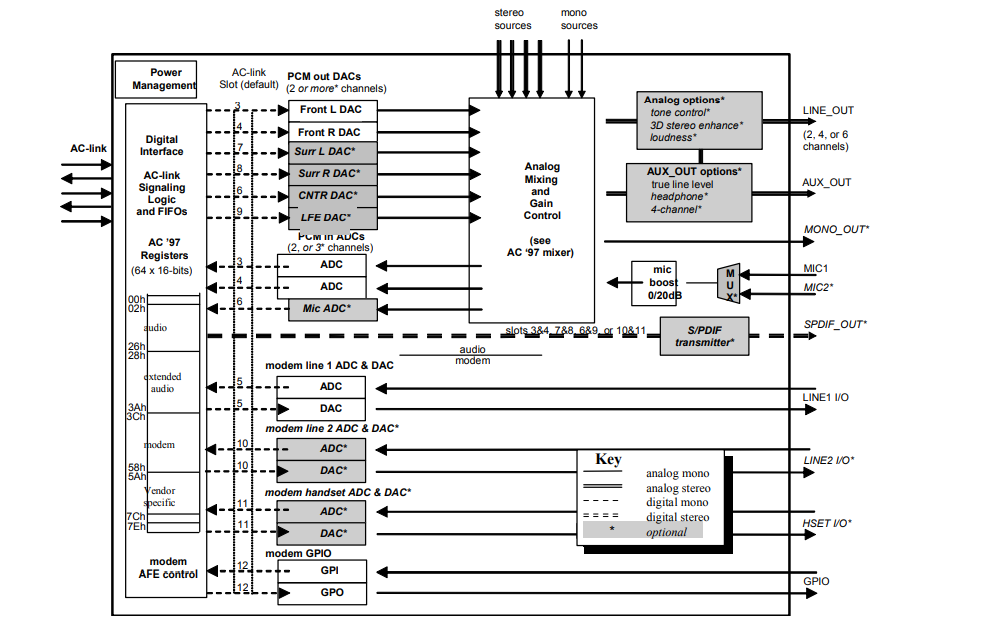

AC97音頻編解碼器的規格標準免費下載

PCM3500:低功耗16位調制解調器編解碼器的卓越之選

PCM3500:低功耗16位調制解調器編解碼器的卓越之選

評論