在AI大模型、自動駕駛和智能終端等應用驅動的算力革命中,隨著SoC集成度突破百億晶體管、工藝節點進入3nm以下,以及存儲器定制化、存內計算等架構的不斷涌現,晶體管級電路仿真與全芯片驗證(Full-Chip Verification)已成為高性能計算和存儲芯片設計流程中最為關鍵且耗時的環節之一。傳統驗證方法在效率、容量與方法學上面臨三重瓶頸,嚴重制約著芯片的上市進度、良率與市場競爭力:

效率與速度的瓶頸:模塊級仿真,特別是含超大規模電源/地網絡(PDN)的后仿,單次仿真時間從幾小時激增至數天甚至數周。

容量與資源的瓶頸:面對幾千萬乃至上億晶體管,疊加數十倍寄生參數,仿真器內存消耗陡增。在合理時間內,利用現有服務器資源完成任務,成為實際工程化的關鍵。

方法學演進的需求:單純依賴仿真器提速已難滿足爆炸式增長的需求。

而全芯片級晶體管仿真更是瓶頸中的瓶頸,涉及存儲器(SRAM/DRAM/Flash/新型存儲器)、全芯片SoC(如電源管理、汽車電子MCU、CIS圖像傳感器)以及數字芯片中的高精度模塊(如時鐘樹后仿),其驗證周期直接決定產品上市時間。

業界亟需新的驗證范式——根據不同電路模塊的工作頻率、精度要求,動態采用最適宜的建模與仿真策略,在可控精度范圍內實現高效簡化,支撐PVT、可靠性與良率分析等全流程驗證。

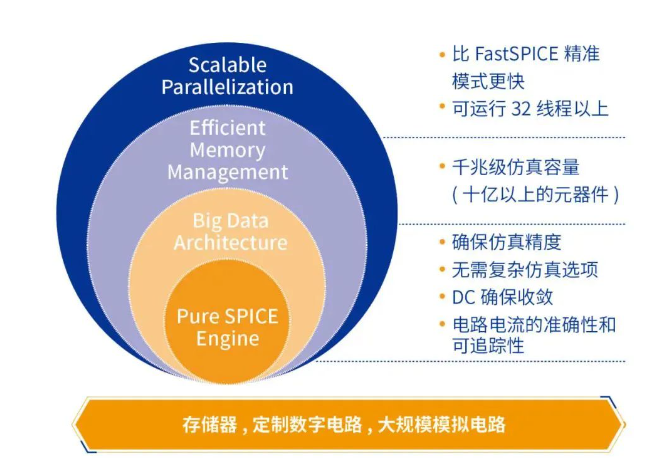

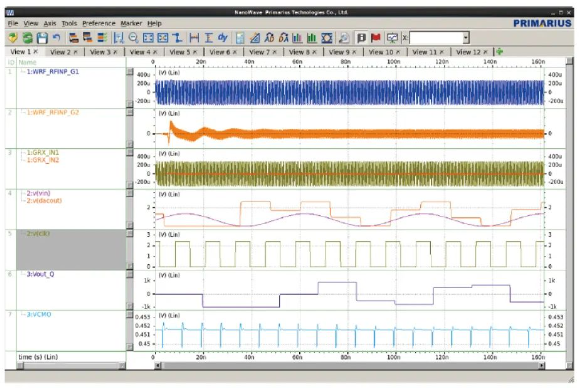

概倫電子的電路仿真解決方案——NanoSpice系列,旨在系統性破解定制和先進工藝下全場景仿真和驗證的困局。根據芯片電路的不同特性與驗證需求,NanoSpice智能匹配最適宜的仿真策略,實現“專通結合”的最優解。

專用的FastSPICE優化:全芯片數模混合電路和存儲器電路

Verilog行為級:數字邏輯

NanoSpice X

確保SPICE級精度,通過高效并行計算,處理上億器件的全芯片后仿真,有效應對容量瓶頸;

輔以卓越的內存管理能力,在主流服務器集群上可完成超大規模PDN與時鐘樹的后仿。

NanoSpice Pro X:創新雙引擎架構基于電路拓撲智能決策,在保證精度的同時實現效率躍升。

在存儲器設計中,自動識別規整結構并應用高度優化的FastSPICE算法,顯著提升陣列驗證效率;

在高精度模擬電路中,無縫切換至SPICE引擎,確保結果精度;

“專通結合”,成為CPU、GPU、AI加速器等復雜SoC的理想選擇,得到客戶的硅后驗證。

更為關鍵的是,NanoSpice Pro X支持先進的3D-IC和多工藝協同仿真技術:

涵蓋從TSV、微凸塊到混合鍵合的復雜互連結構,并完整支持后仿真的反標流程;

顯著優化仿真結果輸出、波形保存、measure語句執行及電路檢查等后處理功能的效率。

確保用戶在面對超大規模仿真結果時,既保留關鍵分析數據,又將電路仿真性能的影響和內存的額外消耗降至最低,有效應對先進封裝和異構集成帶來的驗證挑戰。

NanoSpice MS:打破數模界限,針對數模混合芯片驗證中“數字等模擬”難題。

通過創新的同步算法,實現模擬與數字域的高效協同仿真;

數字部分通過Verilog/System Verilog進行行為級建模,與晶體管級模擬電路聯合仿真,達成真正的全芯片驗證,大幅提升整體效率;

無縫銜接概倫電子自主研發的數字仿真器VeriSim。

概倫電子堅信,單一工具的突破無法解決系統性的驗證困局。因此,我們正致力于構建一個以NanoSpice仿真家族為核心的全場景驗證環境,覆蓋從設計早期到簽核量產的完整流程:

設計早期:通過靜態電路檢查(Static Circuit Check)快速識別潛在設計規則與拓撲問題;

仿真階段:結合動態電路檢查與SOA(Safe Operation Area)分析,確保電路在各種工藝角(Corner)和工作條件下的功能與可靠性;

簽核階段:依托電路良率分析平臺NanoYield與high-sigma分析,精準預測量產良率;同時,通過可靠性晶體管老化分析與信號完整性分析(SI),為芯片的長期穩定運行保駕護航。

概倫電子也相信,驗證的目標是讓設計師能更自由地探索架構創新,更從容地應對設計迭代。NanoSpice仿真家族旨在幫助設計團隊建立高效、無損的驗證流程,避免因工具割裂導致的數據轉換與精度損失。

為探索這一環境的實踐路徑與技術細節,我們將推出“NanoSpice應用解決方案”系列專題,敬請期待以下內容:

首期聚焦:基于NanoYield的電路設計良率優化與高西格瑪(high-sigma)分析方法論;

可靠性初步:靜態與動態電路檢查、SOA分析的進階技巧與實戰案例;

方法學前沿:數模混合仿真與先進驗證策略的深度解析;

可靠性基石:晶體管級老化模型與壽命預測;

信號護航:信號完整性(SI)與電源完整性(PI)的協同驗證方案。

讓我們一同開啟這場關于驗證方法學的深度對話,共同定義全場景仿真的未來。

-

仿真

+關注

關注

55文章

4527瀏覽量

138592 -

晶體管

+關注

關注

78文章

10428瀏覽量

148373 -

概倫電子

+關注

關注

1文章

133瀏覽量

9580

原文標題:概倫電子NanoSpice?系列:定制電路全場景的仿真和驗證方案

文章出處:【微信號:khai-long_tech,微信公眾號:概倫電子Primarius】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

概倫電子與您相約SEMICON China 2026

概倫電子與Fabless芯片設計廠商矽創電子達成技術合作

概倫電子NanoYield斬獲2025全球電子成就獎之年度EDA產品獎

2025概倫電子用戶大會圓滿舉辦

概倫電子將亮相第62屆設計自動化大會DAC 2025 已連續15年參與這一全球EDA頂級盛會

概倫電子先進高速FastSPICE仿真器NanoSpice Pro X介紹

概倫電子先進數字仿真器VeriSim介紹

概倫電子亮相2025慕尼黑上海電子展

概倫電子以AI技術驅動EDA革新

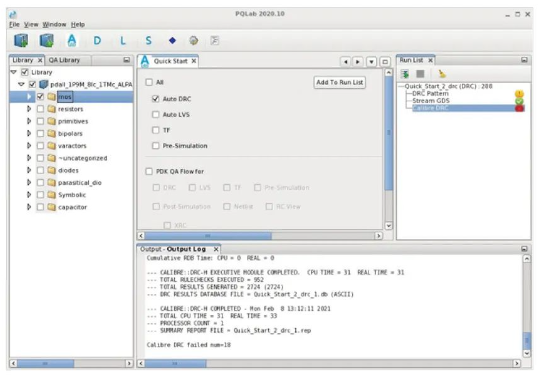

概倫電子先進PDK驗證平臺PQLab介紹

概倫電子NanoSpice系列電路仿真解決方案介紹

概倫電子NanoSpice系列電路仿真解決方案介紹

評論