22.2

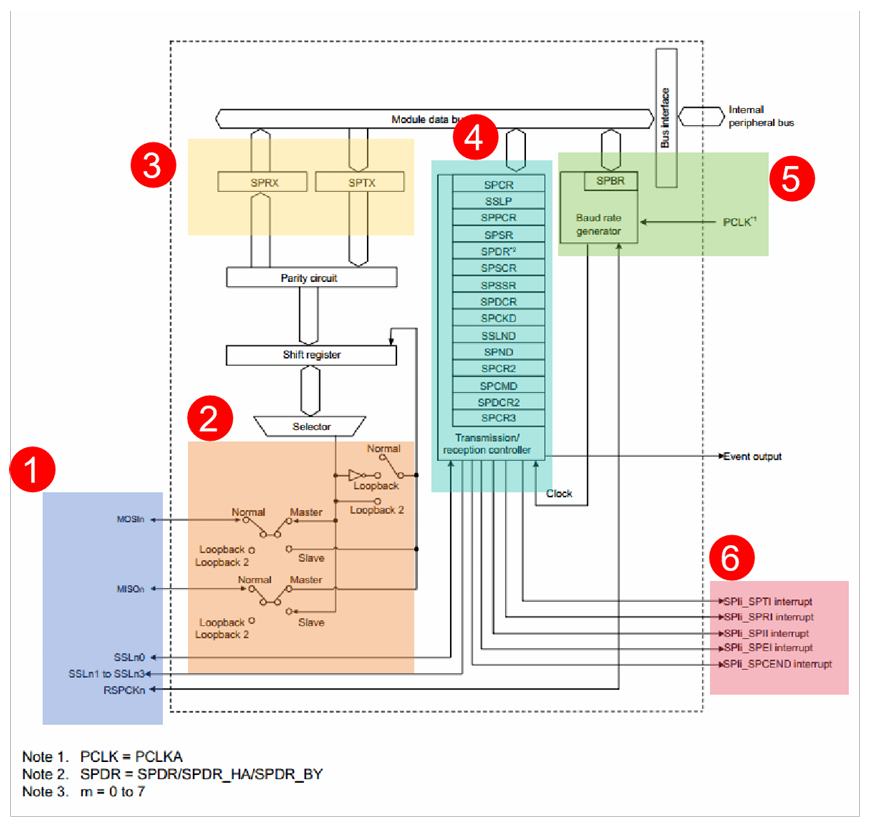

瑞薩SPI功能框圖

以RA6M5為例,SPI的功能結構框圖如下圖所示。接下來我們大致地研究一下它的結構和功能。

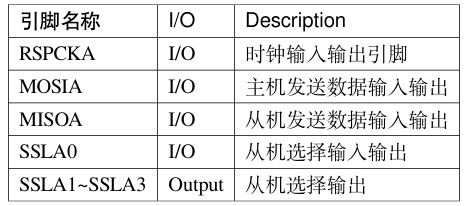

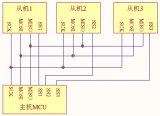

見圖注1,瑞薩RA6M5有兩個SPI外設,分別是SPI0,SPI1,每個SPI都有2~3組,下面是關于SPI各引腳的說明,以SPI0_A為例,見下表,其中值得一提的是,當MCU作為主機時,有多個從機時,從機可通過SSLA0~SSLA3作為片選信號線來連接主機,而當MCU作為從機時,則通過SSLA0作為片選線連接主機。

SPI_0的IO引腳描述:

注

SPI0的引腳名稱表示為“?A”或“?An”,SPI1的引腳名稱表示為“?B”或“?Bn”(n=0、1、2或3)。

見圖注2,其中:

? Master:主機通訊模式

? Slave:從機通訊模式

? Normal:正常通訊模式

? Loopback:環回模式1(接受數據=反轉發送數據)

? Loopback:環回模式2(接受數據=發送數據)

見圖注3,其中:

? SPTX:發送緩沖器

? SPRX:接受緩沖器

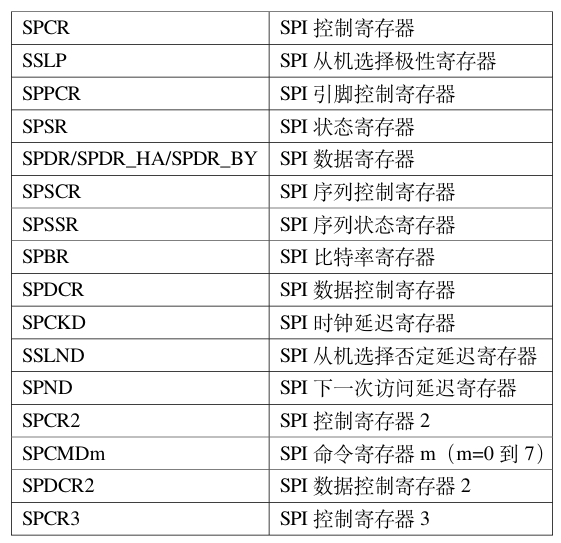

見圖注4,對于瑞薩RA6M5的SPI外設的寄存器介紹,見下表:

SPI的寄存器

注

我們這里主要介紹的是瑞薩的fsp庫的使用,所以在這里寄存器我們在這里做一些簡單的介紹。

見圖注5,SPI波特率設置由寄存器SPBR與SPMDm.BRDV[1:0]設置的組合在主模式下設置。當SPI處于從機模式時,比特率取決于輸入時鐘PCLKA的比特率,與SPBR和SPMDm.BRDV[1:0]位(比特率分頻設置)的設置無關。

見圖注6,其中:

? SPIi_SPRI:接收緩沖區滿事件輸出。

? SPIi_SPTI:發送緩沖區空事件輸出。

? SPIi_SPEI:模式故障、欠載、溢出或奇偶校驗錯誤事件輸出。

? SPIi_SPII:SPI空閑事件輸出。

? SPIi_SPCEND:傳輸完成事件輸出。

-

mcu

+關注

關注

147文章

19036瀏覽量

401438 -

瑞薩

+關注

關注

37文章

22503瀏覽量

91060 -

SPI

+關注

關注

17文章

1893瀏覽量

101709 -

引腳

+關注

關注

16文章

2115瀏覽量

55930

原文標題:SPI物理層及協議層——瑞薩RA系列FSP庫開發實戰指南(71)

文章出處:【微信號:瑞薩嵌入式小百科,微信公眾號:瑞薩嵌入式小百科】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

瑞薩RA系列FSP庫開發實戰指南之QSPI控制FLASH的指令

瑞薩RA系列FSP庫開發實戰指南之SPI通訊協議的物理層和協議層簡介

瑞薩RA系列FSP庫開發實戰指南之SPI通訊協議的結構和功能

瑞薩RA系列FSP庫開發實戰指南之SPI通訊協議的結構和功能

評論