RA芯片的SPI分為簡單SPI和普通SPI,簡單SPI就是SCI模塊(Serial Communications Interface)中的SPI模式,它是使用串行總線來模擬SPI,而我們本章我們所要學習的是普通的SPI,是全功能的SPI,它在RA芯片內部實際存在的一個硬件SPI控制器模塊。

22.1

SPI協議簡介

SPI協議是由摩托羅拉公司提出的通訊協議(Serial Peripheral Interface),即串行外圍設備接口,是一種高速全雙工的通信總線。它被廣泛地使用在ADC、LCD等設備與MCU間,要求通訊速率較高的場合。

在瑞薩RA6M5芯片中,SPI外設可用作通訊的主機及從機,數據傳輸可達到最大的50Mbps速率,信號允許通過SPI操作(4線方法)或時鐘同步操作(3-線方法),支持事件鏈接功能,并具有數據校驗功能。

下面我們分別對SPI協議的物理層及協議層進行講解。

22.1.1

SPI物理層

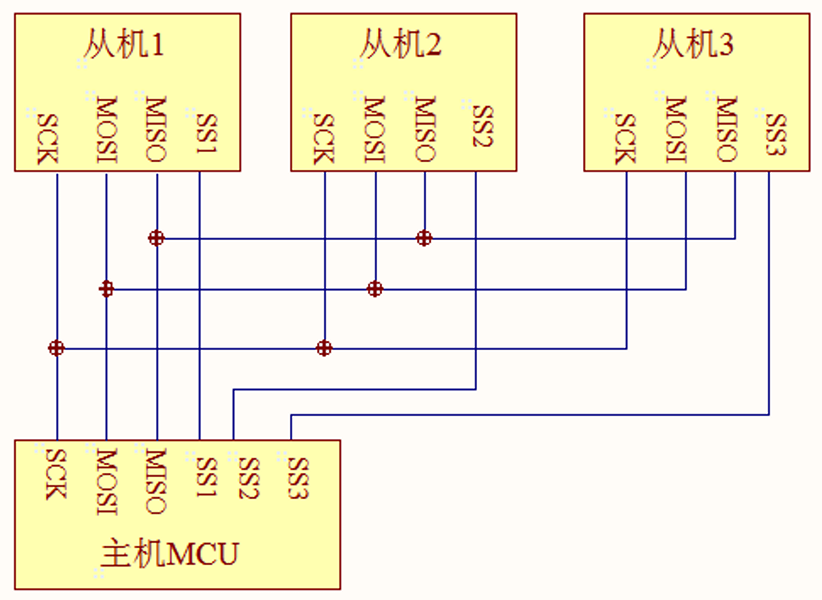

SPI通訊設備之間的常用連接方式見下圖。

SPI通訊使用3條總線及片選線,3條總線分別為SCK、MOSI、MISO,片選線,它們的作用介紹如下:

(1)從設備選擇信號線(SlaveSelect):常稱為片選信號線,也稱為NSS、CS,以下用NSS表示。當有多個SPI從設備與SPI主機相連時,設備的其它信號線SCK、MOSI及MISO同時并聯到相同的SPI總線上,當主機要選擇從設備時,把該從設備的NSS信號線設置為低電平,該從設備即被選中,即片選有效,接著主機開始與被選中的從設備進行SPI通訊。所以SPI通訊以NSS線置低電平為開始信號,以NSS線被拉高作為結束信號。

(2)SCK(Serial Clock):時鐘信號線,用于通訊數據同步。它由通訊主機產生,決定了通訊的速率,不同的設備支持的最高時鐘頻率不一樣,如RA6M5的SPI時鐘頻率最大為fpclkA/2,兩個設備之間通訊時,通訊速率受限于低速設備。

(3)MOSI(Master Output,Slave Input):主設備輸出/從設備輸入引腳。主機的數據從這條信號線輸出,從機由這條信號線讀入主機發送的數據,即這條線上數據的方向為主機到從機。

(4)MISO(Master Input,,Slave Output):主設備輸入/從設備輸出引腳。主機從這條信線讀入數據,從機的數據由這條信號線輸出到主機,即在這條線上數據的方向為從機到主機。

22.1.2

協議層

22.1.2.1

SPI基本通訊過程

SPI通訊的通訊時序,見下圖:

圖22?18 EEPROM數據讀取時序

這是一個主機的通訊時序。NSS、SCK、MOSI信號都由主機控制產生,而MISO的信號由從機產生,主機通過該信號線讀取從機的數據。MOSI與MISO的信號只在NSS為低電平的時候才有效,在SCK的每個時鐘周期MOSI和MISO傳輸一位數據。

以上通訊流程中包含的各個信號分解如下:

22.1.2.2

通訊的起始和停止信號

在上圖SPI通訊時序中的標號1處,NSS信號線由高變低,是SPI通訊的起始信號。NSS是每個從機各自獨占的信號線,當從機在自己的NSS線檢測到起始信號后,就知道自己被主機選中了,開始準備與主機通訊。在標號6處,NSS信號由低變高,是SPI通訊的停止信號,表示本次通訊結束,從機的選中狀態被取消。

22.1.2.3

數據有效性

SPI使用MOSI及MISO信號線來傳輸數據,使用SCK信號線進行數據同步。MOSI及MISO數據線在SCK的每個時鐘周期傳輸一位數據,且數據輸入輸出是同時進行的。數據傳輸時,MSB先行或LSB先行并沒有作硬性規定,但要保證兩個SPI通訊設備之間使用同樣的協定,一般都會采用圖SPI通訊時序中的MSB先行模式。

觀察圖中的標號處,MOSI及MISO的數據在SCK的上升沿期間變化輸出,在SCK的下降沿時被采樣。即在SCK的下降沿時刻,MOSI及MISO的數據有效,高電平時表示數據“1”,為低電平時表示數據“0”。在其它時刻,數據無效,MOSI及MISO為下一次表示數據做準備。

SPI每次數據傳輸可以8位或16位為單位,每次傳輸的單位數不受限制。

22.1.2.4

CPOL/CPHA及通訊模式

SPI一共有四種通訊模式,它們的主要區別是總線空閑時SCK的時鐘狀態以及數據采樣時刻,它們由CPOL與CPHA來決定。

時鐘極性CPOL是指SPI通訊設備處于空閑狀態時,SCK信號線的電平信號(即SPI通訊開始前、NSS線為高電平時SCK的狀態)。CPOL=0時,SCK在空閑狀態時為低電平,CPOL=1時,則相反。

時鐘相位CPHA是指數據的采樣的時刻,當CPHA=0時,MOSI或MISO數據線上的信號將會在SCK時鐘線的“奇數邊沿”被采樣。當CPHA=1時,數據線在SCK的“偶數邊沿”采樣。

見下圖CPHA=0時的SPI通訊模式:

我們來分析這個CPHA=0的時序圖。首先,根據SCK在空閑狀態時的電平,分為兩種情況。SCK信號線在空閑狀態為低電平時,CPOL=0;空閑狀態為高電平時,CPOL=1。

無論CPOL=0還是=1,因為我們配置的時鐘相位CPHA=0,在圖中可以看到,采樣時刻都是在SCK的奇數邊沿。注意當CPOL=0的時候,時鐘的奇數邊沿是上升沿,而CPOL=1的時候,時鐘的奇數邊沿是下降沿。所以SPI的采樣時刻不是由上升/下降沿決定的。MOSI和MISO數據線的有效信號在SCK的奇數邊沿保持不變,數據信號將在SCK奇數邊沿時被采樣,在非采樣時刻,MOSI和MISO的有效信號才發生切換。

類似地,當CPHA=1時,不受CPOL的影響,數據信號在SCK的偶數邊沿被采樣,見下圖CPHA=1時的SPI通訊模式:

由CPOL及CPHA的不同狀態,SPI分成了四種模式,見下表:

SPI的四種模式

SPI的四種模式

主機與從機需要工作在相同的模式下才可以正常通訊,上圖SPI通訊時序就是采用的模式1,而我們本次OLED的SPI通訊實驗就是采用的是模式3。

-

瑞薩

+關注

關注

37文章

22481瀏覽量

90847 -

SPI

+關注

關注

17文章

1885瀏覽量

101207 -

物理層

+關注

關注

1文章

170瀏覽量

35649 -

通訊協議

+關注

關注

10文章

298瀏覽量

21483

原文標題:SPI物理層及協議層——瑞薩RA系列FSP庫開發實戰指南(70)

文章出處:【微信號:瑞薩嵌入式小百科,微信公眾號:瑞薩嵌入式小百科】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

瑞薩RA系列FSP庫開發實戰指南之I2C通訊協議的物理層和協議層簡介

瑞薩RA系列FSP庫開發實戰指南之SPI通訊協議的物理層和協議層簡介

瑞薩RA系列FSP庫開發實戰指南之SPI通訊協議的物理層和協議層簡介

評論