電子發燒友網綜合報道 日前,瀾起科技正式宣布,在國內率先推出基于PCIe 6.x/CXL 3.x標準的高性能有源電纜(AEC)解決方案。這一突破不僅填補了國內高端高速互聯領域的技術空白,更精準契合AI時代數據中心多機架協同的核心需求,提供了高帶寬、低延遲的國產化互聯方案,為國產算力基建突破“血管梗阻”難題筑牢關鍵支撐。

隨著ChatGPT、Sora等生成式AI應用爆發,全球數據中心正加速從“單機架算力聚合”向“多機架超節點協同”迭代升級。AI大模型訓練過程中,數千顆GPU需不間斷進行海量數據交互,對互聯鏈路的帶寬、延遲及穩定性提出指數級增長需求,驅動機柜及相鄰機柜間的互連帶寬從400G向800G乃至1.6T快速演進,這一變革對數據中心內部互連技術提出了前所未有的嚴苛要求。

傳統無源銅纜(DAC)在224 Gb/s PAM4調制模式下,傳輸距離僅為1-2米,雖功耗較低但距離限制顯著;可插拔光模塊雖能突破傳輸距離瓶頸,卻存在功耗高、成本高昂及散熱壓力大等痛點。瀾起科技總裁Stephen Tai指出:“數據中心向多機架復雜架構演進,使得穩定高效的系統級互連成為核心剛需。”這一行業趨勢,正是有源電纜(AEC)技術加速落地的核心驅動力。

從技術演進來看,PCIe 5.0及此前標準的無源電纜已逼近物理傳輸極限,信號在長距離傳輸中衰減嚴重;光模塊方案雖能解決距離問題,但成本居高不下且部署靈活性不足。更為嚴峻的是,高速互聯芯片領域長期被國際巨頭壟斷,國產化率偏低,成為制約我國算力基建自主可控的核心短板。在此背景下,瀾起科技PCIe 6.x/CXL 3.x AEC方案應運而生,精準卡位下一代數據中心互聯的核心賽道。

瀾起此次發布的AEC解決方案,以自研重定時器(Retimer)芯片為核心,融合多項尖端技術,構建起高性能互聯鏈路。作為高速信號的“智能增強器”,該方案通過三大技術創新打破傳輸桎梏:

其一,自研SerDes技術與創新DSP架構深度融合。依托在高速串行接口領域的深厚積累,瀾起SerDes技術可實現信號精準重構,搭配DSP架構的自適應均衡算法,有效抵消傳輸過程中的信號衰減與干擾,確保PCIe 6.0 x16模式下的穩定傳輸,系統時延躋身行業領先梯隊。相較于PCIe 5.0,PCIe 6.0帶寬翻倍至64GT/s,而CXL 3.x標準實現了內存與外設的高效共享,二者協同為異構計算提供靈活的互聯支撐。

其二,采用OSFP-XD高密度接口封裝。該封裝形式在有限機柜空間內實現更高端口密度,精準適配數據中心機柜空間緊張的行業痛點,同時支持多規格電纜配置,可靈活滿足單機架內部、跨機架等不同場景的連接需求,為超節點架構提供多樣化部署選擇。

其三,搭建完善的鏈路監控與診斷體系。方案內置全鏈路監測模塊,可實時捕捉傳輸狀態、信號質量等關鍵參數,提前預警潛在故障,大幅提升數據中心運維效率,這一特性對7x24小時連續運行的AI算力集群而言至關重要。

高速互聯方案的商業化落地,生態兼容性是核心門檻。目前,瀾起科技已完成該方案的全流程開發與系統驗證,順利通過與CPU、xPU、PCIe Switch、網卡等主流設備的互操作測試,完全滿足數據中心超節點系統對PCIe互連的嚴苛要求。這意味著該方案可快速融入現有算力生態,無需對下游設備進行大規模改造,顯著降低商業化落地成本。

Stephen Tai表示,瀾起科技憑借在高速互連領域的長期技術沉淀,精準把握行業機遇推出此方案,助力客戶從容應對下一代算力基建的挑戰。未來,瀾起科技將持續深耕高速互連技術,重點推進PCIe 7.0 Retimer芯片及高速以太網PHY Retimer芯片等下一代產品的研發,為國產算力基建自主化升級持續賦能。

隨著ChatGPT、Sora等生成式AI應用爆發,全球數據中心正加速從“單機架算力聚合”向“多機架超節點協同”迭代升級。AI大模型訓練過程中,數千顆GPU需不間斷進行海量數據交互,對互聯鏈路的帶寬、延遲及穩定性提出指數級增長需求,驅動機柜及相鄰機柜間的互連帶寬從400G向800G乃至1.6T快速演進,這一變革對數據中心內部互連技術提出了前所未有的嚴苛要求。

傳統無源銅纜(DAC)在224 Gb/s PAM4調制模式下,傳輸距離僅為1-2米,雖功耗較低但距離限制顯著;可插拔光模塊雖能突破傳輸距離瓶頸,卻存在功耗高、成本高昂及散熱壓力大等痛點。瀾起科技總裁Stephen Tai指出:“數據中心向多機架復雜架構演進,使得穩定高效的系統級互連成為核心剛需。”這一行業趨勢,正是有源電纜(AEC)技術加速落地的核心驅動力。

從技術演進來看,PCIe 5.0及此前標準的無源電纜已逼近物理傳輸極限,信號在長距離傳輸中衰減嚴重;光模塊方案雖能解決距離問題,但成本居高不下且部署靈活性不足。更為嚴峻的是,高速互聯芯片領域長期被國際巨頭壟斷,國產化率偏低,成為制約我國算力基建自主可控的核心短板。在此背景下,瀾起科技PCIe 6.x/CXL 3.x AEC方案應運而生,精準卡位下一代數據中心互聯的核心賽道。

瀾起此次發布的AEC解決方案,以自研重定時器(Retimer)芯片為核心,融合多項尖端技術,構建起高性能互聯鏈路。作為高速信號的“智能增強器”,該方案通過三大技術創新打破傳輸桎梏:

其一,自研SerDes技術與創新DSP架構深度融合。依托在高速串行接口領域的深厚積累,瀾起SerDes技術可實現信號精準重構,搭配DSP架構的自適應均衡算法,有效抵消傳輸過程中的信號衰減與干擾,確保PCIe 6.0 x16模式下的穩定傳輸,系統時延躋身行業領先梯隊。相較于PCIe 5.0,PCIe 6.0帶寬翻倍至64GT/s,而CXL 3.x標準實現了內存與外設的高效共享,二者協同為異構計算提供靈活的互聯支撐。

其二,采用OSFP-XD高密度接口封裝。該封裝形式在有限機柜空間內實現更高端口密度,精準適配數據中心機柜空間緊張的行業痛點,同時支持多規格電纜配置,可靈活滿足單機架內部、跨機架等不同場景的連接需求,為超節點架構提供多樣化部署選擇。

其三,搭建完善的鏈路監控與診斷體系。方案內置全鏈路監測模塊,可實時捕捉傳輸狀態、信號質量等關鍵參數,提前預警潛在故障,大幅提升數據中心運維效率,這一特性對7x24小時連續運行的AI算力集群而言至關重要。

高速互聯方案的商業化落地,生態兼容性是核心門檻。目前,瀾起科技已完成該方案的全流程開發與系統驗證,順利通過與CPU、xPU、PCIe Switch、網卡等主流設備的互操作測試,完全滿足數據中心超節點系統對PCIe互連的嚴苛要求。這意味著該方案可快速融入現有算力生態,無需對下游設備進行大規模改造,顯著降低商業化落地成本。

Stephen Tai表示,瀾起科技憑借在高速互連領域的長期技術沉淀,精準把握行業機遇推出此方案,助力客戶從容應對下一代算力基建的挑戰。未來,瀾起科技將持續深耕高速互連技術,重點推進PCIe 7.0 Retimer芯片及高速以太網PHY Retimer芯片等下一代產品的研發,為國產算力基建自主化升級持續賦能。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

數據中心

+關注

關注

18文章

5647瀏覽量

75008 -

瀾起科技

+關注

關注

0文章

132瀏覽量

15641

發布評論請先 登錄

相關推薦

熱點推薦

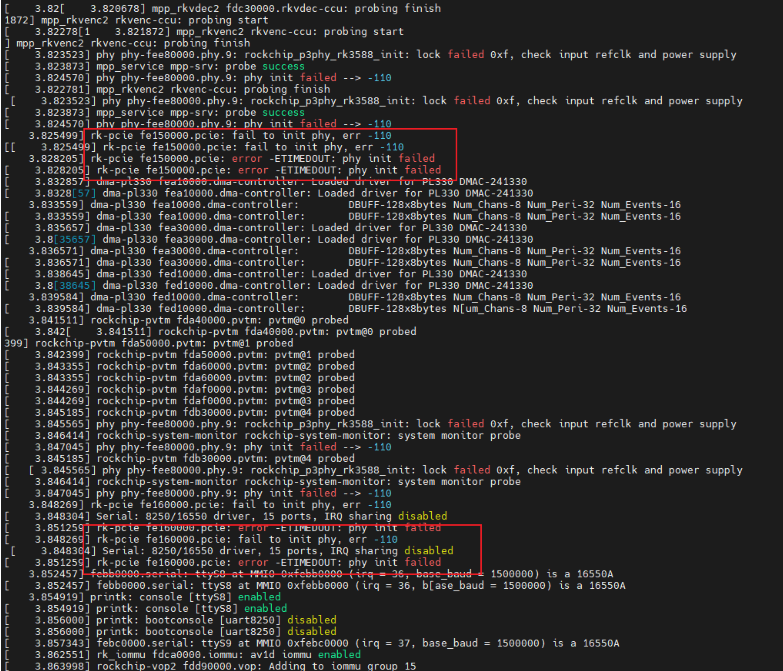

請問是否有支持 M2/SSD 的可用 6.x 內核?

我嘗試過從GitHub - starfive-tech/linux 在 JH7110_VisionFive2_upstream.不幸的是它無法啟動。

唯一可用的 6.x 內核是 ubuntu 6.2.6 中的 23.04。它運行良好,但缺乏對 PCIe 和 USB

發表于 02-12 07:15

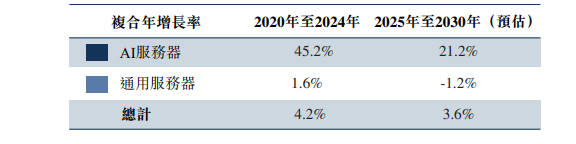

從內存接口到PCIe/CXL、以太網及光互連,高速互連芯片市場分析

黃晶晶 綜合整理 ? 高速互連芯片定義及分類高速互連芯片是支撐數據中心、服務器及計算機實現高速數據交互的必備芯片,主要解決智能算力系統持續升級背景下各類

實戰復盤:RK3588 SPI+PCIe3x4方案啟動修復,從節點配置到驅動適配全解析

? ? ? 在 RK3588 嵌入式項目中, “ 接口配置不匹配 ” 是高頻踩坑點 —— 近期 基于 linux6.1 內核 調試 SPI 閃存 +PCIe3x4 外設 方案時,就遇到了 “eMMC

Amphenol LTW:數據中心互連解決方案的創新先鋒

Amphenol LTW:數據中心互連解決方案的創新先鋒 在當今數據驅動的時代,數據中心的高效運行至關重要。Amphenol LTW作為一家

Amphenol LTW:數據中心互連解決方案的創新先鋒

在當今數據驅動的時代,數據中心的高效運行至關重要。Amphenol LTW(ALTW)作為一家專注于為惡劣環境提供卓越互連解決方案的企業,憑借其創新技術和豐富產品線,在

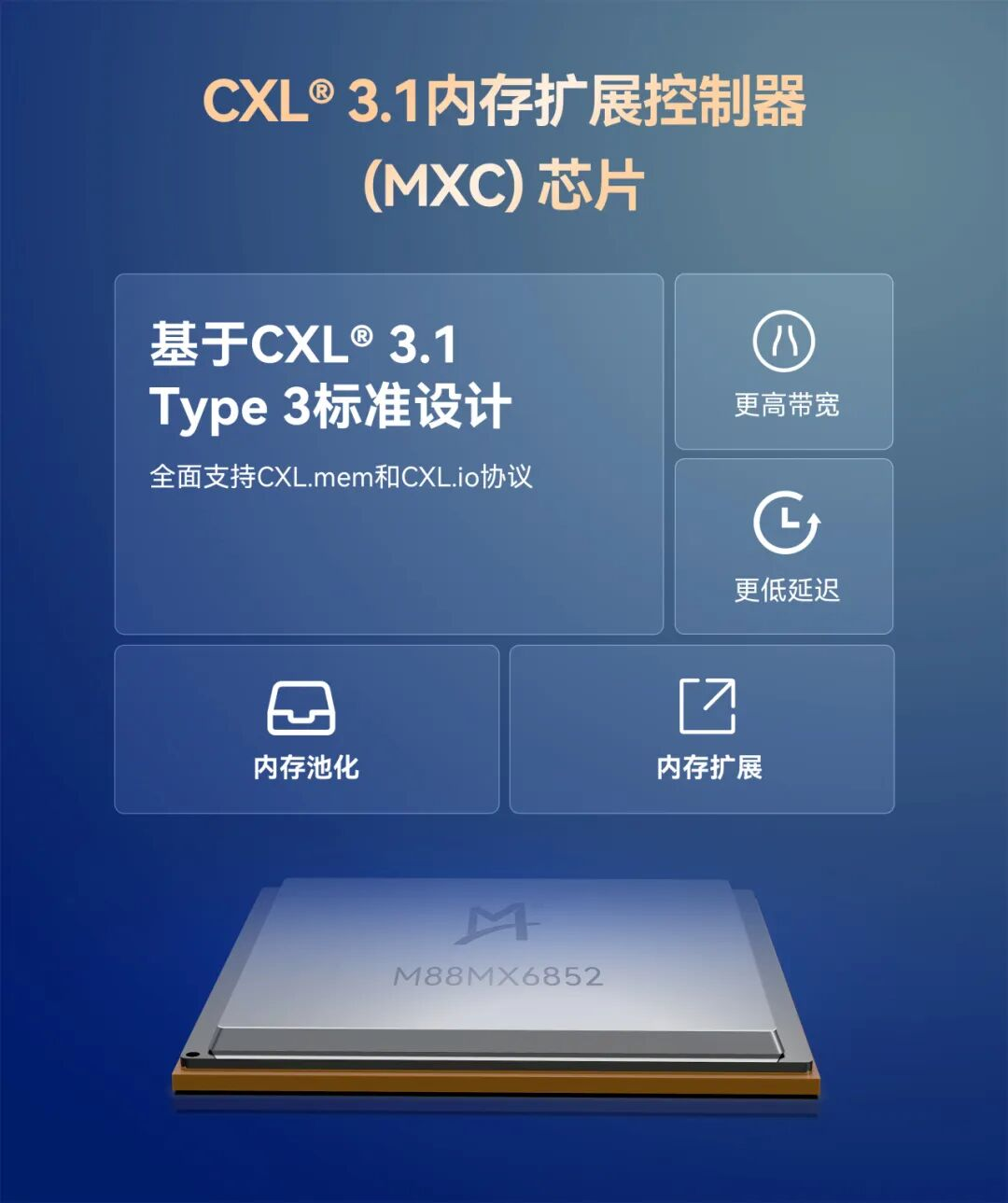

64GT/s+8000MT/s:瀾起CXL 3.1芯片破解數據中心內存瓶頸

。 ? ? M88MX6852:性能卓越,滿足多元需求 ? M88MX6852芯片全面支持CXL.mem和CXL.io協議,其核心使命是為下一代數據中心服務器打造更高帶寬、更低延遲的內存擴展和池化解決

金升陽如何破解數據中心供電難題

在數據中心的龐大能耗版圖中,服務器作為核心業務載體,其電力消耗占比突出且對供電穩定性、持續性有著極高要求。而電源作為能源轉換的關鍵零部件,其能效表現直接決定著數據中心的能源利用效率。

瀾起科技推出CXL? 3.1內存擴展控制器,助力下一代數據中心基礎設施性能升級

下一代數據中心服務器提供更高帶寬、更低延遲的內存擴展和池化解決方案。 瀾起科技CXL 3.1內存擴展控制器采用

PCIe協議分析儀在數據中心中有何作用?

升數據中心的整體可靠性。以下是其核心作用及具體應用場景的詳細分析:一、性能優化:突破帶寬瓶頸,提升計算效率

鏈路帶寬利用率分析

場景:在AI訓練集群中,GPU通過PCIe與CPU交換數據

發表于 07-29 15:02

PCIe協議分析儀能測試哪些設備?

操作性。

應用價值:推動CXL技術在數據中心和AI領域的落地。

光互連模塊

測試場景:測試PCIe over Optical等新興互連技術

發表于 07-25 14:09

中型數據中心中的差分晶體振蕩器應用與匹配方案

關鍵業務平臺,需高IO能力、低時延響應與高并發處理,具備容災與跨區域同步能力。

使用設備: 數據中心級交換機、光模塊、RAID控制器、企業級SSD陣列、PCIe HBA/NIC、高精度差分振蕩器、時間

發表于 07-01 16:33

優化800G數據中心:高速線纜、有源光纜和光纖跳線解決方案

的三大主流布線解決方案——高速線纜(DAC)、有源光纜(AOC)和光纖跳線,并分析它們如何提高性能并支持現代數據中心不斷增長的需求。

800G數據中心高速線纜和

發表于 03-24 14:20

瀾起發布國內首個PCIe 6.x/CXL 3.x有源電纜方案,破解數據中心互連瓶頸

瀾起發布國內首個PCIe 6.x/CXL 3.x有源電纜方案,破解數據中心互連瓶頸

評論