在RK3588嵌入式項目中,“接口配置不匹配”是高頻踩坑點——近期基于linux6.1內(nèi)核調(diào)試SPI閃存+PCIe3x4外設(shè)方案時,就遇到了“eMMC方案正常,切換后系統(tǒng)卡死”的問題。核心癥結(jié)不僅是驅(qū)動適配,更在于PCIe3x4節(jié)點的硬件參數(shù)未對齊。本文將聚焦pcie3x4接口的關(guān)鍵配置,結(jié)合驅(qū)動優(yōu)化與系統(tǒng)掛載同步,完整拆解解決方案,幫你避開同類陷阱。

一、問題背景:PCIe3x4接口成“啟動瓶頸”

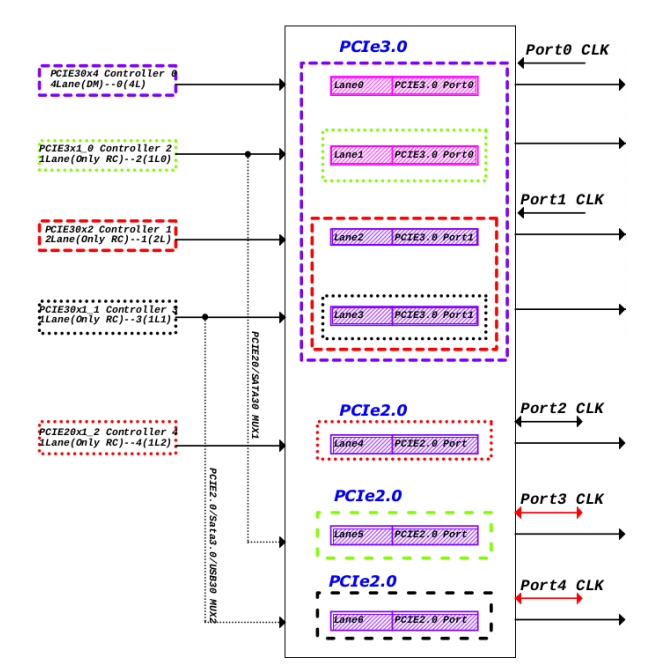

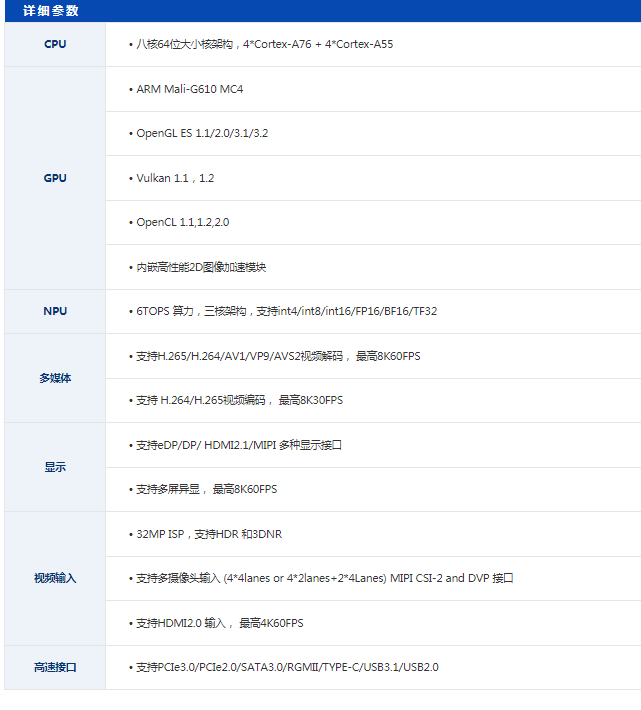

RK3588支持多組PCIe接口(如pcie3x2、pcie3x4),不同接口的lane數(shù)、復(fù)位引腳、供電要求差異極大。我們的項目需求是:

?存儲介質(zhì):SPI閃存(存儲uboot);

?擴展接口:PCIe3x4(需工作在2 lane模式,存儲kernel和rootfs)。

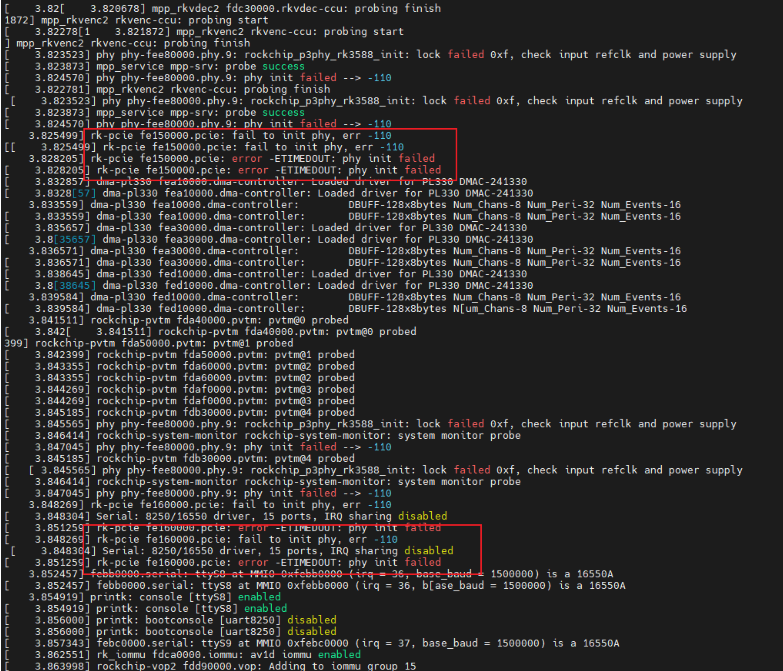

但實際調(diào)試時,系統(tǒng)啟動直接卡死,串口日志報兩類關(guān)鍵錯誤:

1.PCIe相關(guān):rk-pcie fe150000.pcie: fail to init phy, err -110(PHY初始化失敗)、PCIe Link Fail, LTSSM is 0x0(鏈路未建立);

2.系統(tǒng)掛載:Waiting for root device PARTUUID=614e0000-0000...(根分區(qū)UUID不匹配)。

對比eMMC方案,問題根源清晰:PCIe3x4節(jié)點配置未識別硬件,且存儲的根分區(qū)配置未同步。

二、排查與修復(fù):三步搞定PCIe3x4+SPI啟動

1.第一步:修正PCIe3x4節(jié)點配置——硬件參數(shù)必須“對齊”

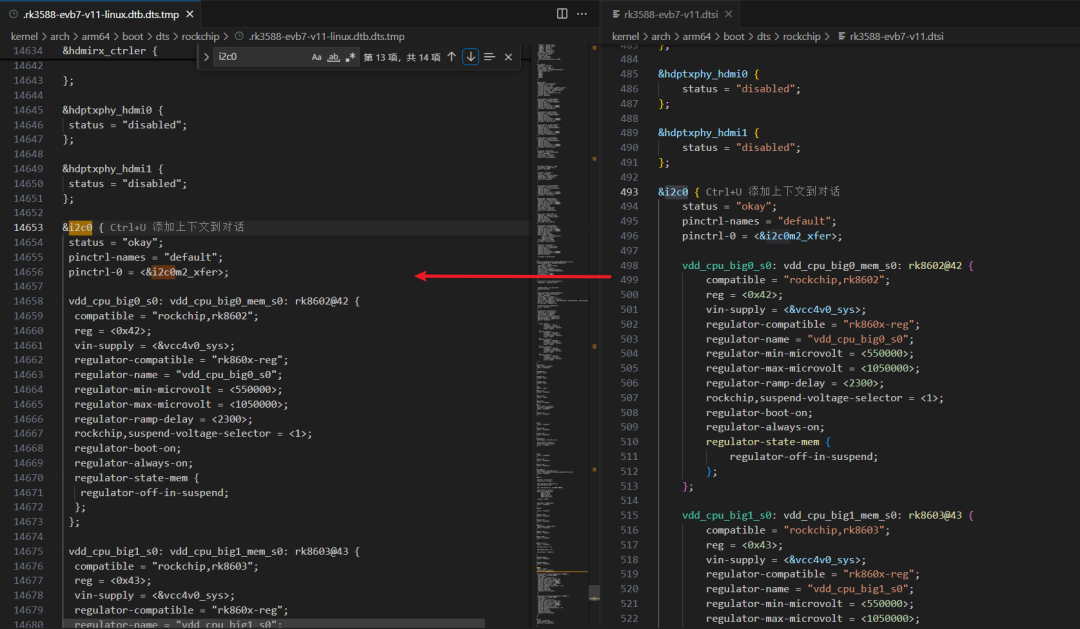

RK3588的PCIe接口需通過設(shè)備樹(DTS)指定“硬件參數(shù)”,默認配置往往與實際版型不匹配。我們最終確定的pcie3x4節(jié)點正確配置如下,每一項參數(shù)都需對應(yīng)硬件設(shè)計:

&pcie3x4 {num-lanes = <2>; //關(guān)鍵:根據(jù)硬件設(shè)計設(shè)為2lane(非默認4lane)//reset-gpios = <&gpio4 RK_PB6 GPIO_ACTIVE_HIGH>;//適配“RK57”版型,當前不用reset-gpios = <&gpio1 RK_PB2 GPIO_ACTIVE_HIGH>;//關(guān)鍵:“RN01”版型的復(fù)位引腳vpcie3v3-supply = <&vcc3v3_pcie30>;//供電:PCIe3.0標準3.3V供電pinctrl-names ="default";//啟用默認引腳控制status ="okay";//啟用接口(默認可能為“disabled”)};

關(guān)鍵參數(shù)解讀(避坑重點):

?num-lanes = <2>:PCIe3x4接口支持1/2/4 lane,但硬件若只布了2 lane線路,設(shè)為4 lane會導(dǎo)致鏈路協(xié)商失敗;

?reset-gpios:復(fù)位引腳必須與硬件原理圖一致,錯配會導(dǎo)致PCIe設(shè)備無法復(fù)位初始化;

?vpcie3v3-supply:必須關(guān)聯(lián)正確的3.3V電源域(vcc3v3_pcie30),供電缺失會直接報PHY初始化錯誤(err -110)。

2.第二步:優(yōu)化PCIe驅(qū)動——解決PHY初始化與DMA適配

僅配置節(jié)點還不夠,需修復(fù)驅(qū)動中“適配性問題”,確保pcie3x4接口穩(wěn)定工作:

(1)修復(fù)PCIe PHY初始化邏輯(phy-rockchip-snps-pcie3.c)

原驅(qū)動中SRAM初始化判斷與超時定義存在問題,導(dǎo)致PHY啟動超時:

// 原代碼:判斷條件過嚴,超時定義不通用--// 修改后:寬松且準確的判斷,通用超時宏++// 新增PHY校準函數(shù)(適配pcie3x4的信號校準)+staticintrockchip_p3phy_rk3588_calibrate(structrockchip_p3phy_priv *priv)+{+intret =0;+u32 reg;+// 等待PHY0初始化完成(pcie3x4核心PHY)+ret = regmap_read_poll_timeout(priv->phy_grf,+ RK3588_PCIE3PHY_GRF_PHY0_STATUS1,+ reg, RK3588_SRAM_INIT_DONE(reg),+ 100, RK_PCIE_SRAM_INIT_TIMEOUT);+// 若為聚合模式,需同時校準PHY1+if(priv->pcie30_phymode == PHY_MODE_PCIE_AGGREGATION) {+ret |= regmap_read_poll_timeout(priv->phy_grf,+RK3588_PCIE3PHY_GRF_PHY1_STATUS1,+reg, RK3588_SRAM_INIT_DONE(reg),+100, RK_PCIE_SRAM_INIT_TIMEOUT);+}+if(ret)+pr_err("pcie3x4 PHY calibrate failed, check refclk/powern");+returnret;+}// 關(guān)聯(lián)校準函數(shù)到RK3588操作集staticconststructrockchip_p3phy_ops rk3588_ops = {.phy_init = rockchip_p3phy_rk3588_init,+.phy_calibrate = rockchip_p3phy_rk3588_calibrate,// 啟用校準};

(2)適配PCIe DMA初始化(pcie-dw-rockchip.c)

原驅(qū)動未處理“無DMA對象”的場景,導(dǎo)致驅(qū)動異常退出,需補充判斷:

staticintrk_pcie_init_dma_trx(structrk_pcie *rk_pcie){if(IS_ERR(rk_pcie->dma_obj)) {dev_err(rk_pcie->pci->dev,"failed to prepare dmatestn");return-EINVAL;+// 新增:無DMA對象時正常返回(避免驅(qū)動崩潰)+}elseif(!rk_pcie->dma_obj) {/* !CONFIG_ROCKCHIP_PCIE_DMA_OBJ */+return0;}// 啟用客戶端讀寫中斷(保留原邏輯)...}

修改后重新編譯內(nèi)核,串口日志顯示pcie3x4接口正常啟動:

rk-pcie fe150000.pcie: PCIe Link up, LTSSM is 0x30011——鏈路協(xié)商成功。

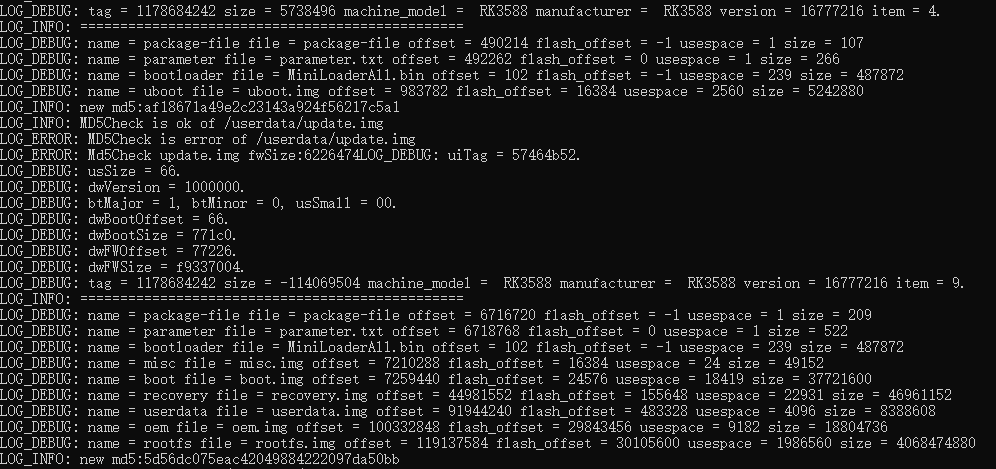

3.第三步:同步pcie根分區(qū)UUID——解決“找不到根設(shè)備”

pcie的根分區(qū)UUID與eMMC完全不同,需從“編譯日志”獲取真實UUID,并同步到兩處配置:

(1)從編譯日志取UUID(關(guān)鍵!避免手動猜測)

生成根文件系統(tǒng)(rootfs)時,編譯日志會明確輸出UUID:

FilesystemUUID: c2ebb35f-b6ea-47ac-94e7-eeb1c99df3cb // 這是ssd根分區(qū)的真實UUID

(2)同步修改parameter.txt與bootargs

?修改device/rockchip/.chips/rk3588/parameter.txt:更新rootfs的UUID:

-uuid:rootfs=4b74bac5-ff38-46be-ae91-7452df777ae8 // 原eMMC的UUID+uuid:rootfs=c2ebb35f-b6ea-47ac-94e7-eeb1c99df3cb // ssd的UUID(來自編譯日志)uuid:boot=7A3F0000-0000-446A-8000-702F00006273

?修改kernel-6.1/arch/arm64/boot/dts/rockchip/rk3588-linux.dtsi:同步bootargs的根分區(qū)配置,并添加ssd的UUID:

chosen: chosen {- bootargs ="earlycon=uart8250,mmio32,0xfeb50000 ... root=PARTUUID=614e0000-0000 ... mtdparts=sfc_nor:0x00040000@0x00180000(vnvm),0x00800000@0x00800000(uboot)";+ bootargs ="earlycon=uart8250,mmio32,0xfeb50000 ... root=PARTUUID=c2ebb35f-b6ea ... mtdparts=sfc_nor:0x00040000@0x00180000(vnvm),0x00800000@0x00800000(uboot),-@0x00A00000(test_data:grow)";};

注:root=PARTUUID只需填前16位(c2ebb35f-b6ea),系統(tǒng)即可識別;test_data:grow是SPI的擴展分區(qū),主要用于測試,按需添加。

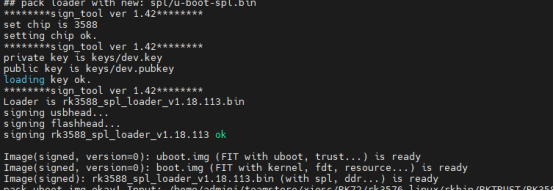

三、最終驗證:PCIe3x4+SPI方案正常工作

完成上述修改后,燒錄鏡像測試,結(jié)果符合預(yù)期:

1.PCIe3x4外設(shè):lspci命令能識別到PCIe設(shè)備(如NVMe硬盤),讀寫速度正常;

2.系統(tǒng)啟動:無“等待根設(shè)備”報錯;

3.穩(wěn)定性:PCIe鏈路無斷開,ssd存儲讀寫無異常。

四、關(guān)鍵修改總結(jié)

本次修復(fù)的核心是“硬件參數(shù)對齊+配置同步”,關(guān)鍵修改點整理如下:

|

模塊

|

修改文件路徑

|

核心修改內(nèi)容

|

|

PCIe3x4節(jié)點配置

|

kernel-6.1/arch/arm64/boot/dts/rockchip/xxx.dtsi(如rk3588-evb7-v11.dtsi)

|

設(shè)置num-lanes=2、reset-gpios=gpio1 RK_PB2,status="okay"

|

|

PCIe PHY驅(qū)動

|

kernel-6.1/drivers/phy/rockchip/phy-rockchip-snps-pcie3.c

|

修復(fù)SRAM初始化判斷,新增rockchip_p3phy_rk3588_calibrate校準函數(shù)

|

|

PCIe DMA驅(qū)動

|

kernel-6.1/drivers/pci/controller/dwc/pcie-dw-rockchip.c

|

補充“無DMA對象”的判斷邏輯,避免驅(qū)動崩潰

|

|

根分區(qū)UUID同步

|

device/rockchip/.chips/rk3588/parameter.txt

|

更新uuid:rootfs為pcie根分區(qū)UUID(來自編譯日志)

|

|

系統(tǒng)啟動參數(shù)

|

kernel-6.1/arch/arm64/boot/dts/rockchip/rk3588-linux.dtsi

|

同步bootargs的root=PARTUUID

|

|

內(nèi)核配置優(yōu)化

|

kernel-6.1/arch/arm64/configs/rk3588_linux.config

|

新增CONFIG_RCU_FAST_NO_HZ=y,提升系統(tǒng)實時性

|

五、嵌入式開發(fā)啟示:細節(jié)決定適配成敗

1.PCIe接口配置“硬軟必須對齊”:lane數(shù)、復(fù)位引腳、供電域需1:1對應(yīng)硬件原理圖,尤其是不同版型的引腳差異,錯配必出問題;

2.UUID從編譯日志取,不猜不試:pcie/eMMC的根分區(qū)UUID不同,手動填寫易出錯,直接從rootfs編譯日志復(fù)制最準確;

3.驅(qū)動調(diào)試“抓日志,看關(guān)鍵值”:PHY初始化失敗(err -110)先查供電/復(fù)位,鏈路失敗(LTSSM=0x0)先查lane數(shù)與引腳配置,日志是最佳線索。

如果你的RK3588項目也在PCIe+SPI方案上卡殼,不妨對照本文檢查節(jié)點配置與UUID同步——多數(shù)時候,問題都藏在這些“細節(jié)”里。歡迎在評論區(qū)分享你的調(diào)試經(jīng)驗~

審核編輯 黃宇

-

SPI

+關(guān)注

關(guān)注

17文章

1885瀏覽量

101210 -

PCIe

+關(guān)注

關(guān)注

16文章

1460瀏覽量

88391 -

RK3588

+關(guān)注

關(guān)注

8文章

556瀏覽量

7318

發(fā)布評論請先 登錄

RK3588操控終端

RK3588 CPU?隔離:AB/非?AB?系統(tǒng)雙方案適配實戰(zhàn)

RK3588 PCIe?壓測:從崩潰到排障的全流程解析

一文打通Rockchip DP調(diào)試:從原理到實戰(zhàn),覆蓋RK3399/RK3576/RK3588全平臺

調(diào)試RK3588必看!這個臨時設(shè)備樹文件,藏著你要的所有配置答案

RK3588平臺雙存儲(SPI+PCIE)OTA升級方案教學文檔

保姆級教程!RK3588 Linux6.1?固件簽名完整實現(xiàn)方案(不含rootfs)

一文搞懂?RK3588 PCIe:從硬件資源到拆分配置?+?避坑指南(含腦圖)

開發(fā)者必備,10 分鐘搞定 RK3588 PCIE 拆分!

實戰(zhàn)復(fù)盤:RK3588 SPI+PCIe3x4方案啟動修復(fù),從節(jié)點配置到驅(qū)動適配全解析

實戰(zhàn)復(fù)盤:RK3588 SPI+PCIe3x4方案啟動修復(fù),從節(jié)點配置到驅(qū)動適配全解析

評論