剖析IDT74SSTUBF32865A:28位1:2帶奇偶校驗的寄存器緩沖器

在DDR2內存模塊的設計中,一款優秀的寄存器緩沖器至關重要。今天我們就來深入了解Renesas的IDT74SSTUBF32865A,一款28位1:2帶奇偶校驗的寄存器緩沖器,看看它有哪些特性和優勢,以及在實際應用中需要注意的地方。

一、產品概述

IDT74SSTUBF32865A專為1.7V - 1.9V的VDD電壓操作而設計。它的所有時鐘和數據輸入都符合SSTL_18的JEDEC標準,控制輸入為LVCMOS,輸出則是經過優化的1.8V CMOS驅動器,能夠很好地驅動DDR2 DIMM負載。該器件采用差分時鐘(CLK和CLK)工作,數據在CLK上升沿和CLK下降沿進行寄存。

二、特性亮點

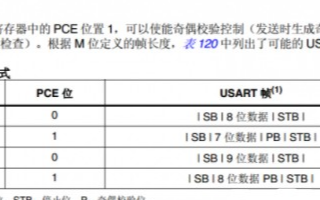

2.1 奇偶校驗功能

這是該器件的一大特色。通過PARIN引腳接收來自內存控制器的奇偶校驗位,并與D0 - D21輸入的數據進行比較,在PTYERR引腳(開漏輸出,低電平有效)指示是否發生奇偶校驗錯誤。這一功能有助于提高數據傳輸的準確性,在對數據可靠性要求較高的應用中尤為重要。

2.2 低電壓操作

支持1.7V - 1.9V的低電壓工作范圍,這不僅降低了功耗,還能適應更多對電源要求較為嚴格的應用場景。

2.3 多種輸入輸出標準支持

數據輸入輸出支持SSTL_18 JEDEC規范,CSGateEN和RESET輸入支持LVCMOS切換電平,這種兼容性使得它能夠與多種不同類型的設備進行良好的配合。

2.4 低功耗待機操作

當復位輸入(RESET)為低電平時,差分輸入接收器被禁用,所有寄存器復位,除PTYERR外的所有輸出被強制為低電平,有效降低了功耗。

三、引腳配置與功能

3.1 主要引腳

- 數據輸入引腳(D0 - D21):接收來自DRAM的輸入數據。

- 時鐘輸入引腳(CLK和CLK):差分時鐘輸入,控制數據的寄存。

- 復位引腳(RESET):異步復位輸入,對器件進行復位操作。

- 奇偶校驗輸入引腳(PARIN):接收奇偶校驗位。

- 奇偶校驗錯誤輸出引腳(PTYERR):指示奇偶校驗錯誤。

3.2 引腳功能詳解

不同的引腳組具有不同的功能,如未門控輸入、片選門控輸入、片選輸入、重驅動輸出、奇偶輸入、奇偶錯誤輸出、編程輸入等。例如,CSGateEN引腳用于控制片選門的使能,當為高電平時,D0 - D21輸入僅在至少一個片選輸入為低電平時在時鐘上升沿被鎖存;當為低電平時,D0 - D21輸入在每個時鐘上升沿都會被鎖存和重驅動。

四、工作模式與操作要點

4.1 復位操作

在電源上電期間,必須將RESET保持在低電平狀態,以確保在提供穩定時鐘之前寄存器輸出的確定性。在DDR2 RDIMM應用中,RESET與CLK和CLK完全異步,進入復位時寄存器會快速清除并使輸出為低電平,退出復位時寄存器會快速恢復工作。

4.2 片選控制

器件會監測DCS0和DCS1輸入,當兩者都為高電平時,Qn輸出狀態將被鎖定;只要其中一個為低電平,Qn輸出將正常工作。RESET輸入優先級高于DCS0和DCS1控制,可強制Qn輸出為低電平,PTYERR輸出為高電平。如果不需要DCS控制功能,可將CSGateEN輸入硬接地。

五、電氣特性與參數

5.1 絕對最大額定值

規定了器件能夠承受的最大應力,如電源電壓范圍為 -0.5V至2.5V,輸入電壓范圍為 -0.5V至VDD + 2.5V等。超過這些額定值可能會對器件造成永久性損壞。

5.2 工作特性

包括電源電壓、參考電壓、輸入輸出電壓范圍、電流等參數。例如,I/O電源電壓VDD為1.7V - 1.9V,參考電壓VREF為0.49 VDD - 0.51 VDD。

5.3 時序要求

對時鐘頻率、脈沖持續時間、建立時間、保持時間、傳播延遲等時序參數進行了規定。例如,最大輸入時鐘頻率fMAX為410MHz,CLK上升沿/下降沿到Qn的傳播延遲為1.1 - 1.5ns。

六、應用場景

該器件主要應用于DDR2內存模塊,能夠與ICS98ULPA877A或IDTCSPUA877A配合提供完整的DDR DIMM解決方案,適用于DDR2 400、533、667和800等不同速率的內存模塊。

七、總結與思考

IDT74SSTUBF32865A憑借其豐富的功能和良好的電氣特性,在DDR2內存模塊設計中具有很大的優勢。然而,在實際應用中,我們需要根據具體的設計需求合理設置各個引腳的參數,嚴格遵守其電氣特性和時序要求,以確保器件的正常工作。例如,在復位操作和片選控制方面,如何根據系統的工作模式進行靈活配置,是我們需要深入思考的問題。同時,對于奇偶校驗功能,如何進一步優化其檢測機制以提高數據的可靠性,也是值得我們探索的方向。

你在使用類似的寄存器緩沖器時,是否也遇到過一些挑戰?你是如何解決的呢?歡迎在評論區分享你的經驗和見解。

發布評論請先 登錄

74SSTUB32868A 28位至56位寄存器緩沖器數據表

74SSTUB32868 28位至56位寄存器緩沖器數據表

剖析IDT74SSTUBF32865A:28位1:2帶奇偶校驗的寄存器緩沖器

剖析IDT74SSTUBF32865A:28位1:2帶奇偶校驗的寄存器緩沖器

評論