SN74SSTU32864:25位可配置寄存器緩沖器的全面剖析

在DDR - II DIMM PCB布局設計中,一款性能出色的寄存器緩沖器至關重要。今天我們就來詳細探討德州儀器(Texas Instruments)的SN74SSTU32864這款25位可配置寄存器緩沖器,了解它的特性、功能及相關設計要點。

文件下載:sn74sstu32864.pdf

產品概述

SN74SSTU32864是德州儀器Widebus +?系列的成員,專為1.7 - 1.9V的(V_{CC})操作而設計。它具有以下顯著特點:

- 可配置性強:可配置為25位1:1或14位1:2寄存器緩沖器,能靈活滿足不同的應用需求。

- 優化布局:引腳排列優化了DDR - II DIMM PCB布局,有助于提高設計的效率和性能。

- 低功耗:芯片選擇輸入可控制數據輸出狀態,減少系統功耗。同時,輸出邊緣控制電路可降低未端接線中的開關噪聲。

- 高可靠性:閂鎖性能超過每JESD 78、II類的100 mA,ESD保護也超過相關標準,包括5000 - V人體模型(A114 - A)、200 - V機器模型(A115 - A)和1000 - V充電設備模型(C101)。

功能特性詳解

輸入輸出特性

- 輸入:除LVCMOS復位(RESET)和LVCMOS控制(Cn)輸入外,所有輸入均為SSTL_18。

- 輸出:所有輸出都是為未端接DIMM負載優化的邊緣控制電路,符合SSTL_18規范。

時鐘與配置控制

- 時鐘:該器件采用差分時鐘(CLK和CLK)輸入,數據在CLK上升沿和CLK下降沿交叉時進行寄存。

- 配置控制:C0和C1輸入用于控制引腳配置。C0控制1:2引腳從寄存器A配置到寄存器B配置,C1控制從25位1:1配置到14位1:2配置。在正常操作期間,C0和C1不應切換,應硬連線到有效的低或高電平,以將寄存器配置為所需模式。

低功耗操作模式

- 待機模式:當RESET為低電平時,差分輸入接收器禁用,允許未驅動(浮動)的數據、時鐘和參考電壓(VREF)輸入。同時,所有寄存器復位,所有輸出被強制為低電平。

- 主動低功耗模式:通過監控系統芯片選擇(DCS和CSR)輸入,當DCS和CSR輸入均為高電平時,可鎖存Qn輸出狀態不變。如果DCS或CSR輸入為低電平,Qn輸出正常工作。RESET輸入優先于DCS和CSR控制,可強制輸出為低電平。

VREF引腳處理

該器件有兩個VREF引腳(A3和T3),內部通過約150Ω連接。實際使用中,只需將其中一個VREF引腳連接到外部VREF電源,未使用的VREF引腳應用(V_{REF})耦合電容器端接。

引腳配置與邏輯圖

引腳配置

根據不同的配置模式,SN74SSTU32864有三種引腳分配方式:

- 25位1:1寄存器((C0 = 0),(C1 = 0)):特定的引腳連接方式以滿足單設備驅動九個SDRAM負載的需求。

- 14位1:2寄存器A((C0 = 0),(C1 = 1)):適用于需要雙設備驅動18 SDRAM負載的情況。

- 14位1:2寄存器B((C0 = 1),(C1 = 1)):提供另一種配置選擇,以適應不同的系統設計。

邏輯圖

文檔中給出了三種配置模式下的正邏輯邏輯圖,有助于工程師理解器件內部的信號處理流程和邏輯關系。

電氣特性與參數

絕對最大額定值

了解器件在不同條件下的絕對最大額定值非常重要,如電源電壓范圍、輸入輸出電壓范圍、輸入輸出鉗位電流、連續輸出電流等。超出這些額定值可能會對器件造成永久性損壞。

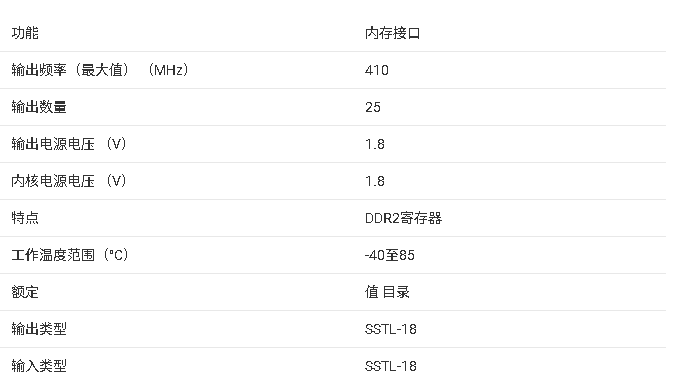

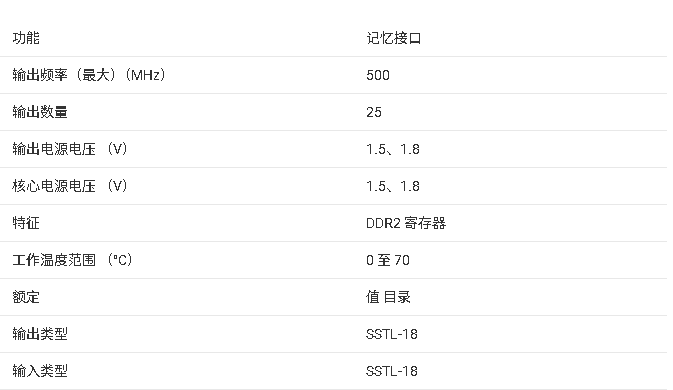

推薦工作條件

為確保器件正常工作,需要遵循推薦的工作條件,包括電源電壓、參考電壓、輸入電壓、時鐘頻率等參數的范圍。例如,電源電壓(V{CC})推薦范圍為1.7 - 1.9V,參考電壓(V{REF})為0.49 x (V{CC}) - 0.51 x (V{CC})。

電氣參數

文檔還提供了詳細的電氣參數,如不同測試條件下的輸出電壓(VOH、VOL)、電源電流(ICC、ICCD、ICCDLP)、輸入電容(Ci)等。這些參數有助于工程師評估器件的性能和功耗。

時序要求

明確了時鐘頻率、脈沖持續時間、差分輸入激活和非激活時間、建立時間和保持時間等時序要求。例如,時鐘頻率最大可達500 MHz,DCS、DODT、DCKE和數據在CLK上升沿和CLK下降沿前的建立時間為0.5 - 0.7 ns。

開關特性與輸出擺率

開關特性包括最大頻率(fmax)、傳輸延遲時間(tpdm、tpdmss、tRPHL)等。輸出擺率規定了上升沿和下降沿的變化速率范圍,如上升沿和下降沿的擺率在1.9 - 4.9 V/ns之間。

封裝信息

SN74SSTU32864有不同的封裝選項,如文中提到的NFBGA(NMJ)封裝。同時還提供了封裝尺寸、包裝數量、載帶信息、物料類型、RoHS合規性、防潮等級、操作溫度范圍和部件標記等詳細信息,方便工程師進行PCB設計和生產組裝。

總結與思考

SN74SSTU32864作為一款功能強大的可配置寄存器緩沖器,在DDR - II DIMM設計中具有很大的優勢。其豐富的功能特性和詳細的參數說明為工程師提供了全面的設計支持。然而,在實際應用中,工程師還需要根據具體的系統需求,合理配置器件的工作模式,關注電氣特性和時序要求,以確保系統的穩定性和可靠性。大家在使用這款器件的過程中,有沒有遇到過一些特殊的問題或者獨特的解決方案呢?歡迎在評論區分享交流。

發布評論請先 登錄

SN74SSTU32864:25位可配置寄存器緩沖器的全面剖析

SN74SSTU32864:25位可配置寄存器緩沖器的全面剖析

評論