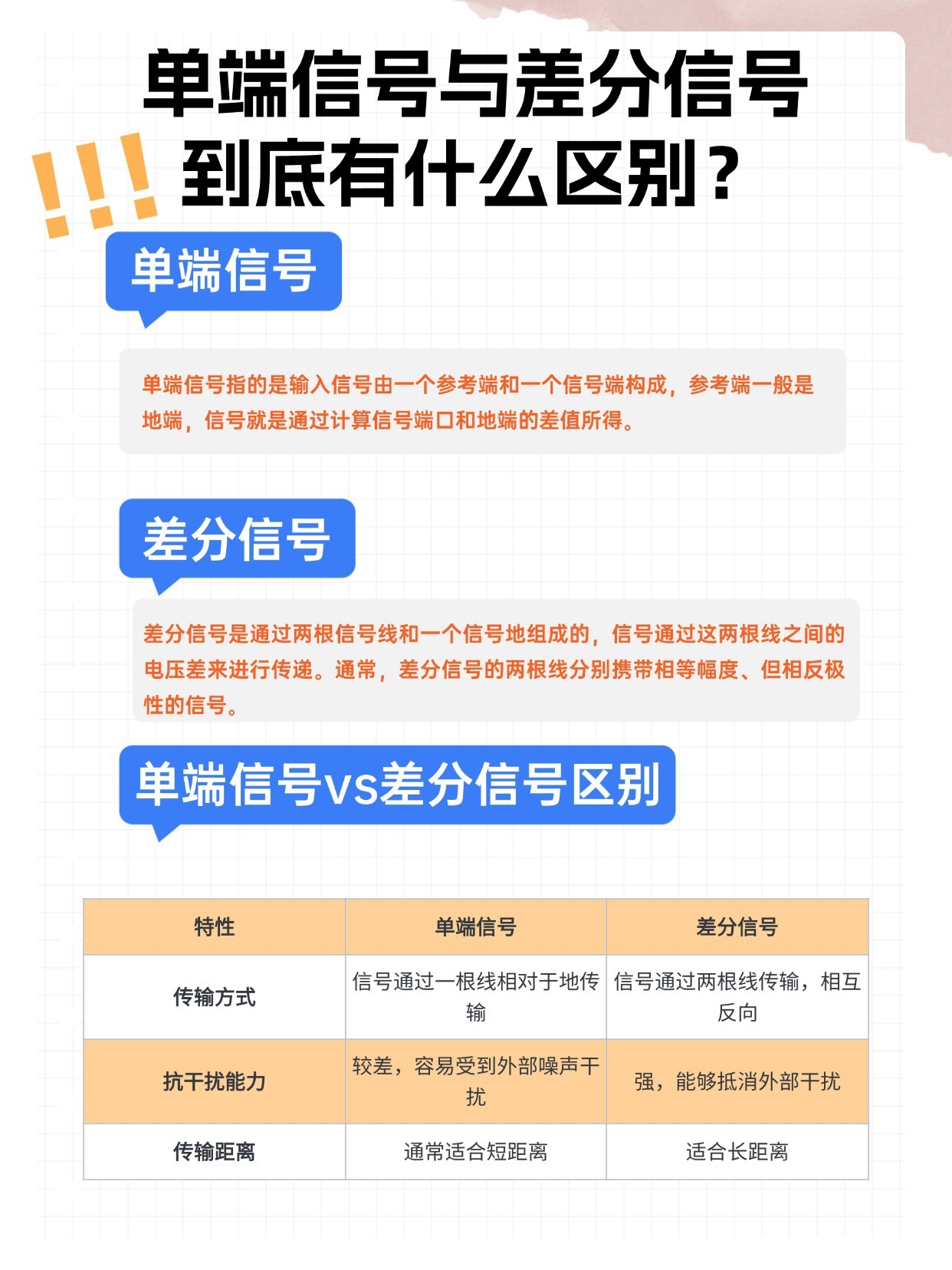

在電子電路設計中,差分信號負端接地是很常見的兼容改造或簡化方案,但這么做會讓信號從差分模式變成單端-地參考模式,原本的共模抑制能力直接喪失,很容易被地環路噪聲、電源紋波這些干擾影響。濾波設計是解決這類干擾的核心,而截止頻率的設定直接決定濾波效果——既要保住有用信號不失真,又要把干擾牢牢抑制住。今天就給大家分享一套實用方法,把理論和工程實踐結合起來,輕松定好截止頻率。

核心前提要摸清,避免盲目算錯數

定截止頻率前,先把兩個關鍵參數搞清楚,這是后續所有計算的基礎,少了這一步很容易走彎路。

先明確有用信號參數,重點抓「信號最高頻率f_signal」。比如傳感器輸出的0~1kHz信號、高速數據傳輸的50MHz信號,這個數值直接關系到信號完整性。截止頻率必須覆蓋信號的高頻成分,要是低于這個數值,信號波形就會出現拖尾、上升沿變緩的問題,影響電路正常工作。

再梳理干擾信號參數,找出主要干擾的「最低頻率f_noise」。像工頻干擾的50Hz、開關電源紋波的10kHz、EMI高頻干擾的1MHz,都屬于常見干擾類型。截止頻率的設定要能讓這類干擾被顯著衰減,不然濾波就失去了意義。

截止頻率的核心設定原則

核心邏輯很明確:截止頻率fC要大于等于信號最高頻率的1.5-2倍,同時小于等于干擾最低頻率的0.8~0.9倍。

之所以要留1.5-2倍的信號頻率余量,是因為濾波器在截止頻率處會有3dB衰減,足夠的余量能避免有用信號的高頻成分被過度濾除,保證信號的幅度和相位都不失真。而限定在干擾最低頻率的0.8~0.9倍以內,是為了讓干擾信號落在截止頻率以上,這樣濾波器才能對其進行有效衰減,而且頻率越高,干擾衰減效果通常越好。

4步搞定截止頻率,工程場景直接用

第一步:鎖定關鍵頻率值

結合實際場景找對數值,計算才有用。低頻場景比如傳感器差分信號,頻率范圍0~1kHz(f_signal=1kHz),現場存在10kHz的開關電源紋波(f_noise=10kHz);高頻場景像高速差分信號,頻率0~50MHz(f_signal=50MHz),伴隨100MHz的電磁干擾(f_noise=100MHz),這兩種都是典型情況。

第二步:算出兩個基準值

信號側基準fC1按1.5-2倍f_signal計算,優先取中間值,這樣能兼顧信號完整性和干擾抑制效果;干擾側基準fC2按0.8~0.9倍f_noise計算,確保干擾能被有效過濾。

第三步:確定最終截止頻率fC

取fC1和fC2的交集范圍即可。如果交集過窄,優先滿足fC≥fC1——畢竟信號完整性比單純抑制干擾更重要,信號失真了,再強的抗干擾能力也沒用。

還是結合前面的例子,低頻場景中fC1在1.5kHz-2kHz之間,fC2在8kHz-9kHz之間,最終fC選2-5kHz(比如3kHz)就很合適;高頻場景里fC1為75MHz-100MHz,fC2為80MHz-90MHz,交集范圍80~90MHz,選85MHz就能兼顧兩者。

第四步:實測驗證并調整

計算出的fC只是理論值,實際應用中必須用示波器驗證效果。如果濾波后還有明顯干擾,可適當降低fC,比如從3kHz調到2kHz;要是信號出現失真、波形變鈍,就提高fC,比如調到4kHz。另外高頻場景(頻率>1MHz)要注意濾波器的寄生參數,像RC濾波中電阻的寄生電感,這類因素會影響帶寬,可借助仿真工具輔助調整。

不同濾波拓撲的截止頻率計算補充

1. RC低通濾波(低頻信號首選)

計算公式為fC = 1/(2πRC),其中τ=RC是時間常數。選型方面,電阻建議取1kΩ-100kΩ,電容選1nF~1μF(低頻場景),材質優先NP0/C0G,溫漂小且性能穩定。

2. LC低通濾波(高頻信號首選)

計算公式為fC = 1/(2π√(LC))。選型時電感取1μH~10μH(高頻場景),電容選X7R材質,高頻特性更優,同時要規避寄生參數對帶寬的影響。

新手避坑提醒,這些錯誤別犯

別為了抗干擾犧牲信號質量,要是一味降低fC抑制干擾,只會導致信號失真,反而影響整個系統性能。接地設計要配合濾波,差分負端必須單點接地,濾波器件的接地端就近連接信號地,避免形成地環路引入新干擾。高頻場景下,示波器和探頭的帶寬要≥3倍fC,不然沒法準確觀測濾波效果,后續調整也會偏離方向。

審核編輯 黃宇

-

濾波

+關注

關注

10文章

706瀏覽量

58032 -

差分信號

+關注

關注

4文章

409瀏覽量

29037

發布評論請先 登錄

探索LTC1063:高性能時鐘可調濾波器的卓越之選

【「玩轉高速電路:基于ANSYS HFSS的無源仿真實例」閱讀體驗】+差分信號

高帶寬雙路 SPDT 差分信號開關 TS3DS26227 詳解

TDK TCM0403T薄膜共模濾波器:高速差分信號的EMC解決方案

TDK TCM06U系列共模濾波器:高速信號的噪聲克星

單片機的差分信號到底是什么?

Sallen-KEY濾波器傳遞函數問題

M12電纜接頭針腳定義:差分信號引腳配置里的 “傳輸密碼”

差分信號負端接地:濾波截止頻率怎么確定?附步驟+ 案例?

差分信號負端接地:濾波截止頻率怎么確定?附步驟+ 案例?

評論