在電信設備高頻化、高功率需求日益迫切的今天,電源傳輸網絡(PDN)的穩定性直接決定了芯片能否在復雜工況下正常運行。而 “目標阻抗” 作為 PDN 設計的核心基準,更是衡量供電可靠性的關鍵指標 —— 它能確保芯片即便面臨最差瞬態電流,電源軌電壓噪聲也能控制在可接受范圍。

今天就來拆解 PDN 優化的核心邏輯,分享如何用MPQ8785負載點(PoL)器件實現阻抗容限要求,還附實戰案例喔!

先搞懂:什么是 PDN 目標阻抗?

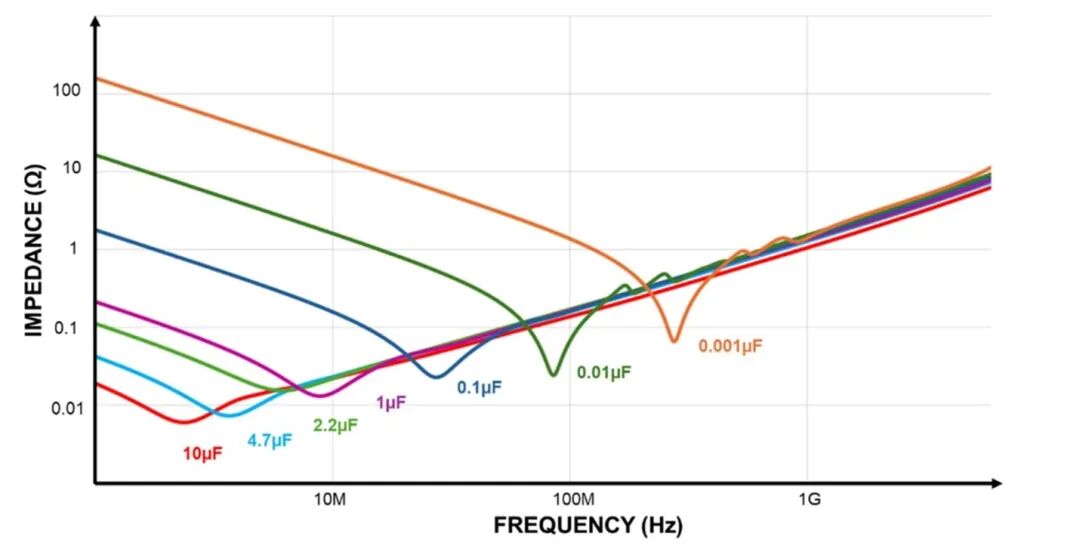

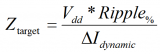

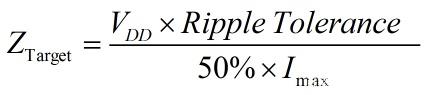

簡單說,目標阻抗(Z (TARGET))是電源軌允許的最大阻抗閾值,核心作用是 “壓制噪聲”。它的計算邏輯很直接:目標阻抗 = 最大允許紋波電壓 ÷ 最大預期電流階躍負載

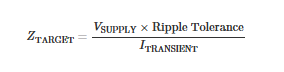

要讓全頻段阻抗都低于這個閾值,需要兩大關鍵:低頻段靠電源調節器支撐,中高頻段則依賴去耦電容的精準選型與布局(比如 MLCC 多層陶瓷電容,其阻抗會隨頻率變化,需針對性匹配)。

圖1:MLCC的阻抗頻率特性

不同頻段對阻抗的要求不同,配電網中每個元件都得在對應頻段優化—— 這也是 PDN 設計的核心難點之一。

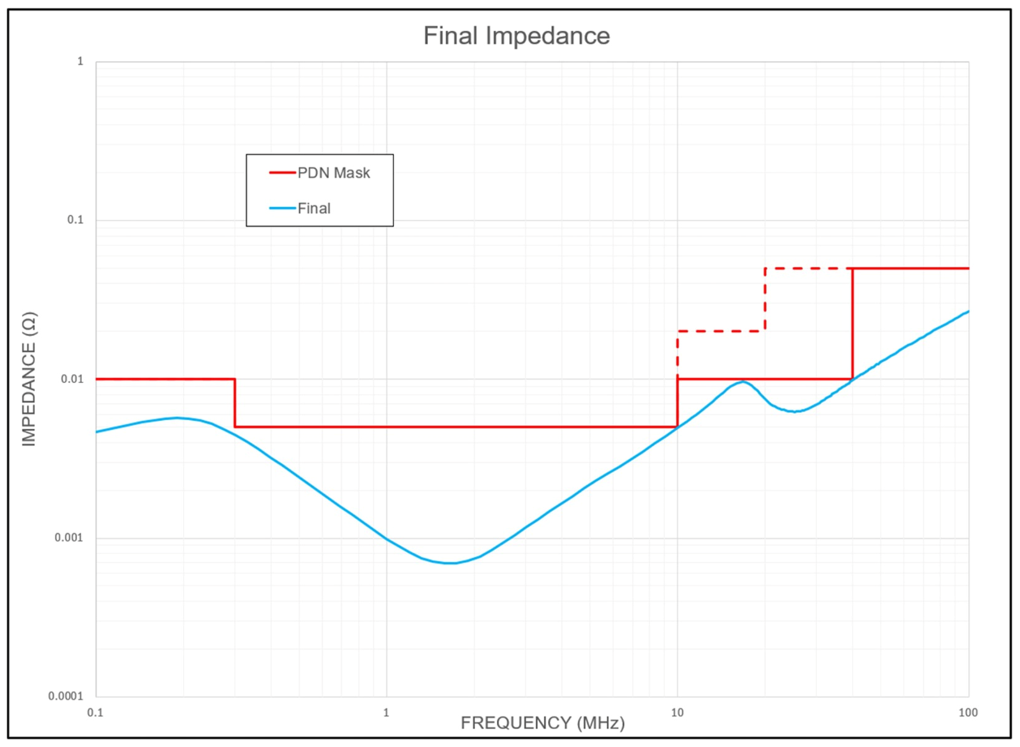

圖2:目標阻抗示例

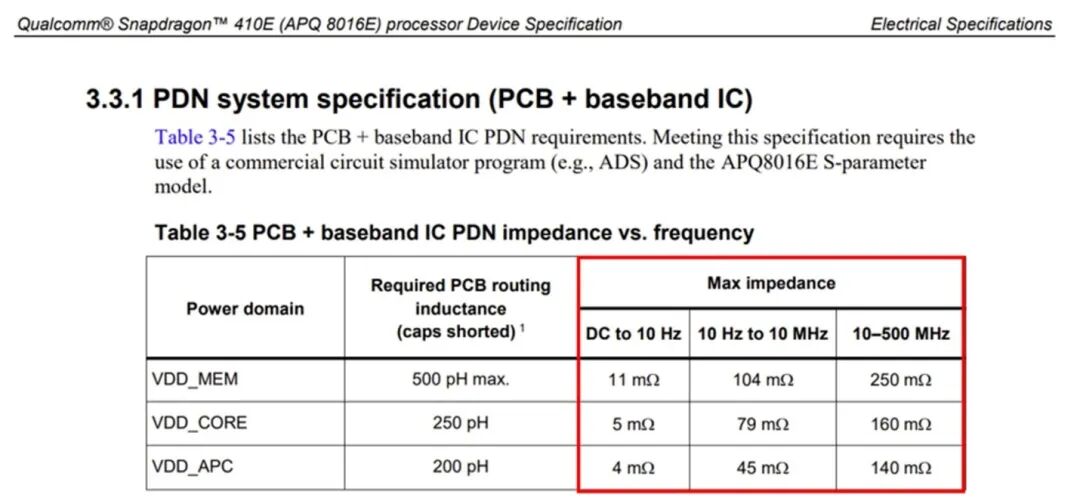

PDN 優化新思路:三級低通濾波器法

理想的 “零阻抗” PDN 不現實,傳統堆去耦電容的方式也未必高效。其實可以把 PDN 看作三級低通濾波器,每一級各司其職,針對性降低不同頻段阻抗:

圖3:將PDN概念化為三級低通濾波器

1封裝濾波:電流的 “第一道降噪門”

從 SoC 晶片汲取的電流,會先經過封裝與晶片側電容(DSC)的配合,初步降低電流斜率,相當于給瞬態電流 “減速”,減少噪聲傳導。

2PCB 層 + MLCC:中高頻段的 “核心濾波層”

電流通過 BGA 后,會流經 PCB 電源層并與 MLCC 作用。這里的關鍵是:電容要選對頻率特性 —— SoC 下方的高頻電容只對特定頻段有效,對低頻調節作用甚微,無需盲目堆砌。

3電壓調節器(VR)+ 大電容:低頻噪聲 “穩定器”

最后一級由 VR 和大電容聯手,重點壓制低頻噪聲,為電源軌提供基礎穩定性,確保整體供電的平穩性。

這種結構化設計,能讓每個組件都精準覆蓋對應頻段,比無序堆電容更高效、更可靠。

實戰案例:MPQ8785 評估板如何達標?

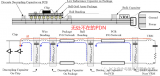

光說理論不夠,我們用 MPS 電信專用評估板(搭載高頻同步降壓變換器MPQ8785)做實測,看看如何通過電容選型與布局,讓 PDN 阻抗滿足容限要求。

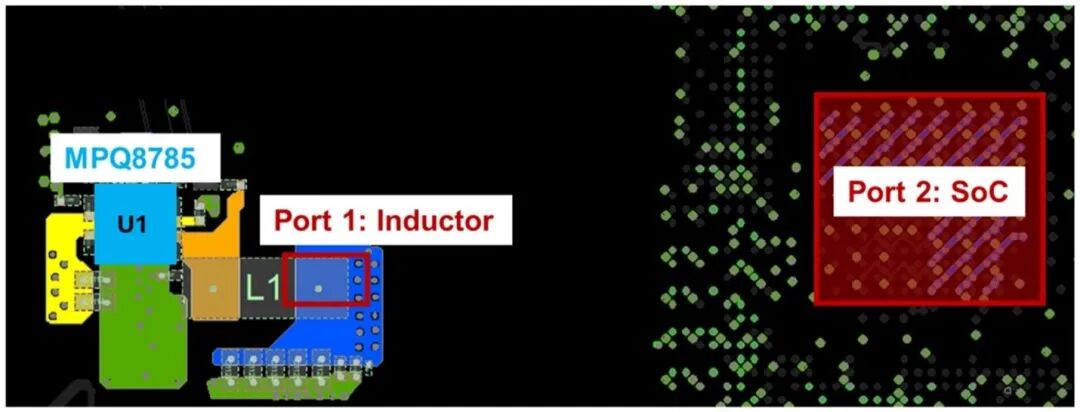

圖4:MPS電信評估板

第一步:提取參數,發現問題

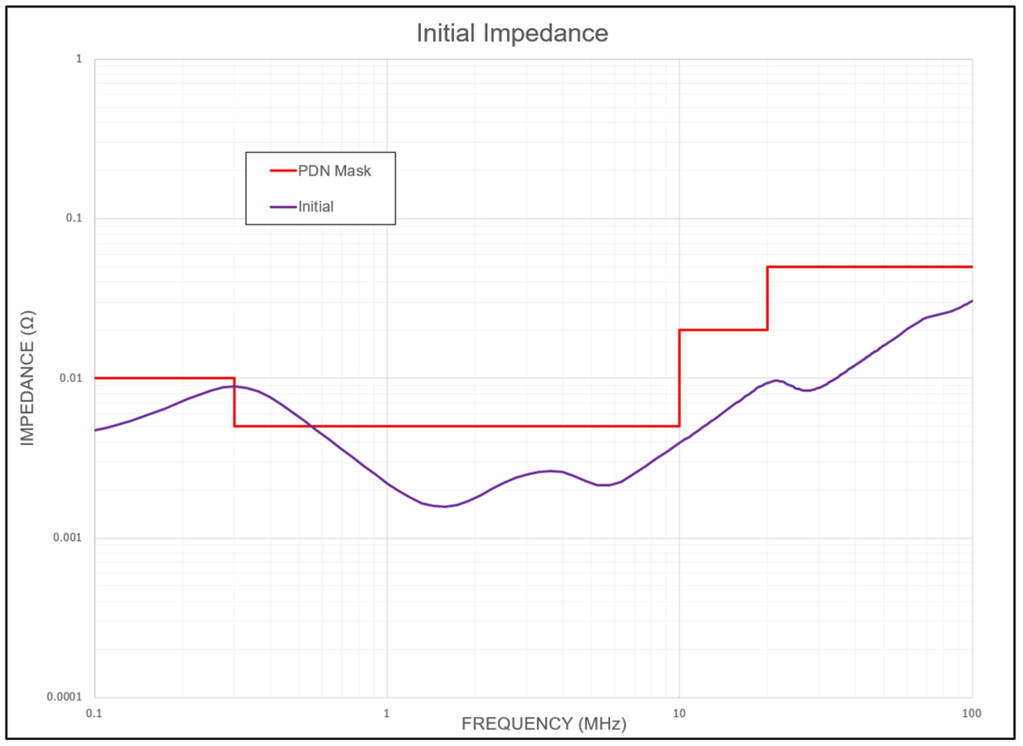

先獲取 PCB 寄生參數(含電容的 ESL、ESR 等),選擇兩個關鍵端口分析:端口 1 在電感后方,端口 2 連接 SoC BGA。通過實測發現:初始電容配置下,300kHz~600kHz 頻段的阻抗超出了規定限值,這是核心優化點。

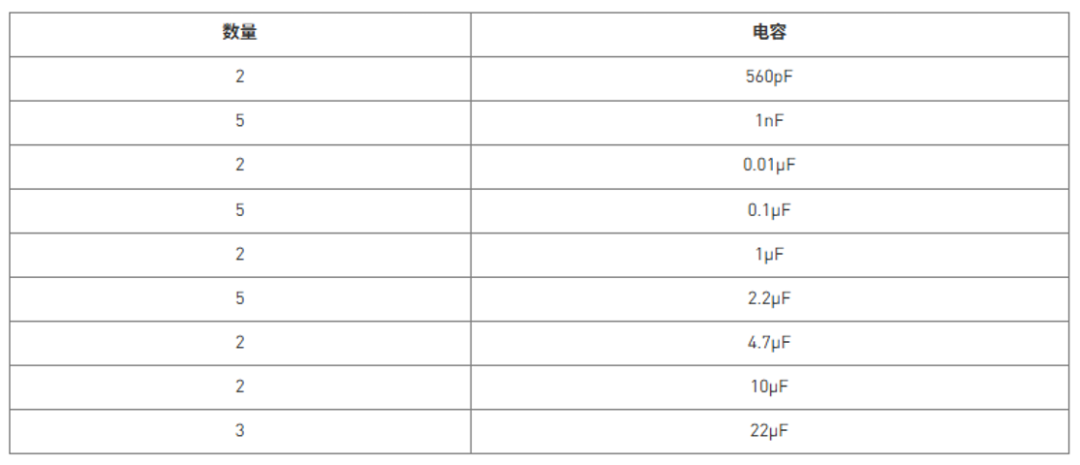

表1:初始電容選型方案

圖5:目標阻抗曲線與初始阻抗的對比

第二步:迭代選型,精準優化

高頻電容只對特定頻段有效,盲目增加沒用。我們通過多次仿真,篩選出最佳電容組合(兼顧數量與類型):

針對超標頻段,補充特定規格電容,直接拉低阻抗;

10MHz 以上頻段有充足裕度,果斷省去多余高頻電容,既節省板面積,又降低成本。

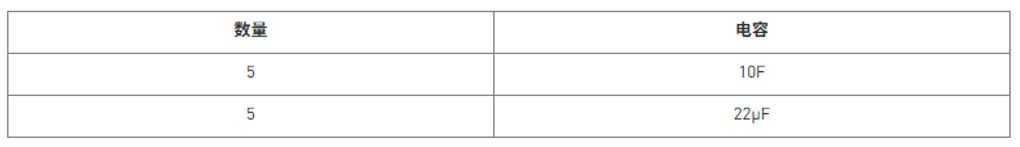

表2:最佳電容選型

圖6:電容優化后的最終阻抗

第三步:驗證結果,完美達標

優化后的 PDN 阻抗曲線,全頻段都符合容限要求!甚至在后續測試中,我們把 10MHz~40MHz 的阻抗容限要求降至 10mΩ,只需額外添加 10 個 0.1μF 電容,就能輕松滿足。

圖7:電容優化后的阻抗,可降低PDN容限要求

這充分說明:只要選對電容、布對位置,配合MPQ8785的高性能,就能在 “性能、成本、空間” 三者間找到完美平衡。

PDN 優化的核心,不是 “堆更多電容”,而是 “讓每個組件在對應頻段發揮最大作用”。通過三級低通濾波器法的結構化設計,再加上MPQ8785的高頻優勢,就能高效滿足阻抗容限要求,為電信設備提供穩定、可靠的電力傳輸。

如果你在 PDN 設計中遇到阻抗超標、電容選型糾結等問題,歡迎在評論區交流!

-

濾波器

+關注

關注

162文章

8411瀏覽量

185692 -

負載點

+關注

關注

1文章

20瀏覽量

8620 -

PDN

+關注

關注

0文章

86瀏覽量

23453

原文標題:PDN 阻抗不達標?用 MPQ8785 這樣優化,電信設備供電穩了!

文章出處:【微信號:MPS芯源系統,微信公眾號:MPS芯源系統】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

搞定電源完整性,不如先研究PDN!

PCB電源完整性的雙面視角,用一篇文章理清時域電源噪聲與頻域PDN阻抗的關系

PDN設計的目的

基于可分解的多目標進化算法的PDN阻抗的優化

PDN設計

PDN 環路電感對紋波和總阻抗有何影響?

MPS車規級三相門級驅動解決方案——MPQ6533

PDN 元件對阻抗的影響

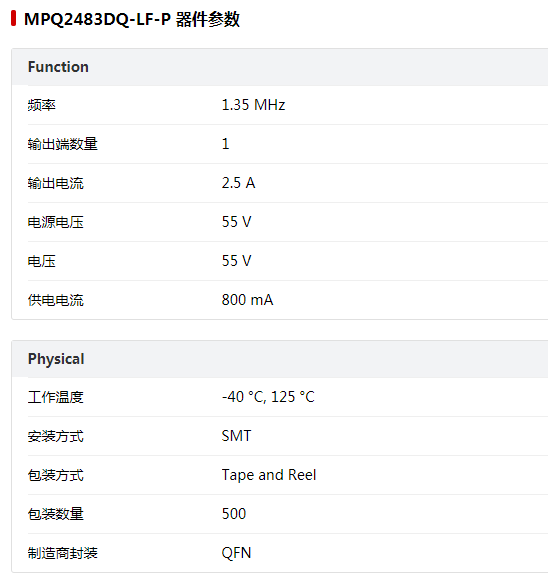

Monolithic Power Systems (MPS)MPQ2483DQ-LF-P PWM LED驅動IC的參數特性 EDA模型和數據手冊分享

NVSwitch芯片周圍MLCC陣列的PDN阻抗優化方案

使用MPS MPQ8785負載點器件實現PDN阻抗容限要求

使用MPS MPQ8785負載點器件實現PDN阻抗容限要求

評論