在PCB制造中,時(shí)間就是金錢(qián) - 但其中可能出現(xiàn)很多始料未及的突發(fā)狀況,一個(gè)沒(méi)有考慮可制造性的復(fù)雜電路設(shè)計(jì),可能導(dǎo)致整個(gè)產(chǎn)品上線計(jì)劃停滯。此外,可制造性設(shè)計(jì)(Design for Manufacturing)不良所帶來(lái)的隱性成本也極其高昂:延遲、失效、溝通成本、設(shè)計(jì)返工、反復(fù)測(cè)試。

如何降低隱性成本、縮短交期、確保設(shè)計(jì)可制造?

本文重點(diǎn)闡述了常見(jiàn)的DFM問(wèn)題如何延誤交期并增加成本,并提供了切實(shí)可行的建議,幫助設(shè)計(jì)和制造團(tuán)隊(duì)更高效地協(xié)作。

隱性成本:隱藏的預(yù)算殺手

當(dāng)生產(chǎn)停滯時(shí),問(wèn)題往往已經(jīng)不再單純,隱性成本 - 這些間接但常被忽略的費(fèi)用 - 會(huì)顯著推高PCB總成本。這些隱性成本包括:

為糾正DFM問(wèn)題而增加的EQ時(shí)間;

與制造商就模糊數(shù)據(jù)反復(fù)溝通;

因可測(cè)試性差導(dǎo)致的品質(zhì)不穩(wěn)定;

因非標(biāo)組件導(dǎo)致的采購(gòu)延誤;

因布局相關(guān)問(wèn)題導(dǎo)致的組裝返工

這些問(wèn)題不僅影響當(dāng)前生產(chǎn)批次,還會(huì)波及后續(xù)批次、保修索賠,甚至損害企業(yè)品牌聲譽(yù)。更關(guān)鍵的是,會(huì)耽誤產(chǎn)品上市,損失機(jī)會(huì)成本。

問(wèn)題#1 超制程能力和過(guò)高公差要求

超過(guò)制造商常規(guī)能力的線寬、間距或Via尺寸要求,不僅會(huì)增加成本,還會(huì)導(dǎo)致更長(zhǎng)的交期。

對(duì)制造的影響:

需要先進(jìn)的模具和工藝管控

過(guò)長(zhǎng)的設(shè)計(jì)評(píng)估時(shí)間,導(dǎo)致CAM延遲

可能觸發(fā)工程變更請(qǐng)求,導(dǎo)致更長(zhǎng)的EQ時(shí)間

如何降低影響:

非必要情況下,始終在制造商“最佳制程能力范圍”內(nèi)進(jìn)行設(shè)計(jì)。更嚴(yán)格的公差要求應(yīng)服務(wù)于產(chǎn)品性能需求,而非形式上的完美主義。

問(wèn)題#2 缺乏全局思維的復(fù)雜疊層和微孔結(jié)構(gòu)

高多層PCB和HDI板設(shè)計(jì)在當(dāng)今高密度應(yīng)用中極為常見(jiàn)。但若在未確認(rèn)可行性和交期情況下就貿(mào)然指定盲孔/埋孔結(jié)構(gòu)或特殊材料,可能導(dǎo)致交期延長(zhǎng)。

對(duì)成本的影響:

需要特殊層壓工藝管控

縮小了可選供應(yīng)商范圍

增加因?qū)娱g對(duì)位誤差導(dǎo)致的報(bào)廢風(fēng)險(xiǎn)

如何降低影響:

盡早與PCB制造商協(xié)調(diào),評(píng)估疊層設(shè)計(jì)的可行性;在布局階段就精準(zhǔn)模擬阻抗,并驗(yàn)證材料可行性,而非在布局完成后進(jìn)行。

問(wèn)題#3 不完整或不清晰的制造文件

Gerber、坐標(biāo)文件、鉆孔文件等生產(chǎn)資料中存在矛盾或缺失的信息,將導(dǎo)致項(xiàng)目延遲。

對(duì)制造的影響:

制造商暫停生產(chǎn),等待信息確認(rèn)

交期增加2-4天,來(lái)解決文件問(wèn)題

導(dǎo)致PCB按照錯(cuò)誤規(guī)格生產(chǎn)

如何降低影響:

仔細(xì)核對(duì)輸出的所有制造文件,包括:

清晰的網(wǎng)表名稱和鉆孔尺寸

包含材料和厚度的疊層圖

清晰的圖形/器件定義

標(biāo)注層功能(如信號(hào)層、電源層、接地層等)

問(wèn)題#4 組件布局與布向不當(dāng)

為便于放置而非組裝需求的密集排列,是常見(jiàn)的PCB布局問(wèn)題,包括組件極性對(duì)齊不當(dāng)、焊盤(pán)尺寸不規(guī)則及間距過(guò)小等問(wèn)題。

對(duì)成本的影響:

組裝效率低或失敗率高

出現(xiàn)立碑或橋接風(fēng)險(xiǎn)更高

需要人工檢查或返工

如何降低影響:

極性組件對(duì)齊一致;在BGA或高組件周?chē)舫鲎銐蚩臻g;在布局過(guò)程中檢查IPC-7351標(biāo)準(zhǔn)及SMT工廠的基準(zhǔn)要求。

問(wèn)題#5 忽視可測(cè)試性(DFT)

未進(jìn)行可測(cè)試性設(shè)計(jì),將導(dǎo)致更高的不良率和更長(zhǎng)的調(diào)試周期。

對(duì)成本的影響:

由于難以確定問(wèn)題根源,導(dǎo)致產(chǎn)線管控成本增加

更長(zhǎng)的功能測(cè)試和驗(yàn)證過(guò)程

難以對(duì)關(guān)鍵節(jié)點(diǎn)進(jìn)行ICT或JATG測(cè)試

如何降低影響:

為關(guān)鍵信號(hào)添加檢測(cè)點(diǎn);確保沒(méi)有部件阻礙探針測(cè)試;向您的EMS工廠明確測(cè)試范圍和預(yù)期。

問(wèn)題#6 使用過(guò)時(shí)或難采購(gòu)的元器件

性能上,該元器件可行,但若其已過(guò)時(shí)或采購(gòu)交期長(zhǎng)達(dá)52周,就會(huì)造成生產(chǎn)停滯。

對(duì)供應(yīng)鏈的影響:

設(shè)計(jì)需要緊急調(diào)整

二次采購(gòu)會(huì)增加風(fēng)險(xiǎn),且無(wú)法保證批次一致性

由于加急采購(gòu)導(dǎo)致產(chǎn)品整體成本上升

如何降低影響:

在原理圖階段與采購(gòu)團(tuán)隊(duì)或EMS工廠合作;盡可能使用AVL(批準(zhǔn)供應(yīng)商列表)中的器件,并在最終BOM確定前通過(guò)Octopart、SiliconExpert等工具驗(yàn)證器件的生命周期狀態(tài)。

問(wèn)題#7 忽略決策對(duì)交期的影響

DFM不僅關(guān)乎產(chǎn)品的可制造性,還關(guān)乎交期。將設(shè)計(jì)推至制造極限,會(huì)拖慢每個(gè)階段的進(jìn)度。

對(duì)交期的影響:

CAM團(tuán)隊(duì)因設(shè)計(jì)不符合制造規(guī)格提出改版請(qǐng)求

額外的質(zhì)量檢查

材料采購(gòu)周期過(guò)長(zhǎng)(如特殊材料)

如何降低影響:

在明確最終設(shè)計(jì)(如疊層結(jié)構(gòu)、過(guò)孔類型、表面處理、銅箔厚度等)時(shí),始終考慮其需耗費(fèi)的時(shí)間。如有疑問(wèn),請(qǐng)?jiān)诖_定設(shè)計(jì)前聯(lián)系代工廠或EMS廠商。

作為PCB設(shè)計(jì)工程師,很多人習(xí)慣在嚴(yán)格限制下進(jìn)行設(shè)計(jì)。但重要的是,工廠的技術(shù)能力表并非是可以隨意搭配的菜單目錄。我們經(jīng)常會(huì)看到這樣的設(shè)計(jì):客戶認(rèn)為可以將例如Type VI或Type VII過(guò)孔處理工藝與最緊湊的線寬/間距組合,結(jié)果最后得到一份沒(méi)有任何工廠能生產(chǎn)的PCB設(shè)計(jì)文件。

一個(gè)常見(jiàn)問(wèn)題:設(shè)計(jì)師在看到鍍通孔的最小間距后,開(kāi)始在電路板上密集布置過(guò)孔,導(dǎo)致過(guò)孔之間幾乎沒(méi)有絕緣區(qū)域。這使得層壓難度極高,因?yàn)檫^(guò)孔之間沒(méi)有足夠空間使得PP能夠?qū)⒏鲗诱澈显谝黄稹?/p>

另一個(gè)案例:客戶參考了我們的Ultra HDI設(shè)計(jì)指南,在電路板上布置了20um的平行走線來(lái)連接芯片,并指定了超細(xì)鍵合墊上使用硬金工藝。即便是最先進(jìn)的MSAP工藝也無(wú)法實(shí)現(xiàn)這種組合。事實(shí)上,硬金工藝與細(xì)線寬往往是互斥的。這與電鍍工藝極限有關(guān),也與尺寸公差有關(guān)。

核心要點(diǎn):工藝能力限制并非累加,您需要在工藝窗口內(nèi)設(shè)計(jì),而非在每個(gè)工藝的極限交匯點(diǎn)上設(shè)計(jì)。理解不同設(shè)計(jì)參數(shù)之間的相互作用-機(jī)械、化學(xué)和熱學(xué)方面 - 與了解參數(shù)各自的極限同樣重要。如有疑問(wèn),請(qǐng)盡早與制造商溝通,這將為您節(jié)省時(shí)間、成本,并避免重新設(shè)計(jì)。

實(shí)際案例:如何通過(guò)DFM大幅縮短交期

一家美國(guó)的初創(chuàng)企業(yè)設(shè)計(jì)了一款高密度的10L板,采用0.075mm微孔和盲孔/埋孔對(duì)。由于所選制造商無(wú)法滿足公差要求,該項(xiàng)目遭到6周延誤。在與EMS合作商咨詢并更改設(shè)計(jì)為標(biāo)準(zhǔn)堆疊微孔和0.10mm鉆孔尺寸后,生產(chǎn)在10天后恢復(fù),成本降低了15%.

如果您想要了解目前行業(yè)大部分PCB工廠可支持的制程能力,與部分先進(jìn)工廠的制程能力范圍,可以現(xiàn)在NCAB的PCB設(shè)計(jì)指南作為參考。

立即下載

審核編輯 黃宇

-

電路板

+關(guān)注

關(guān)注

140文章

5331瀏覽量

108576 -

DFM

+關(guān)注

關(guān)注

8文章

491瀏覽量

31555 -

PCB

+關(guān)注

關(guān)注

1文章

2325瀏覽量

13204

發(fā)布評(píng)論請(qǐng)先 登錄

PCBA良品率低?80%的問(wèn)題出在設(shè)計(jì)階段!一招DFM優(yōu)化幫你解決

華秋DFM軟件丨操作教程——菜單欄-文件板塊篇

華秋DFM軟件丨操作教程——工具菜單-比對(duì)功能篇

華秋DFM軟件丨操作教程——菜單欄-視圖功能篇

PCB絲印極性標(biāo)記的實(shí)用設(shè)計(jì)技巧

PCB疊層設(shè)計(jì)避坑指南

【重磅】企業(yè)版華秋DFM&華秋CAM正式發(fā)布!離線審查+定制開(kāi)發(fā)+專屬護(hù)航

一鍵下單+低至0元打板!華秋DFM帶你解鎖PCB制造新姿勢(shì)

一文讀懂:PCB鉆孔機(jī)主軸及常見(jiàn)型號(hào)大揭秘

一鍵下單+低至0元打板!華秋DFM帶你解鎖PCB制造新姿勢(shì)

PCB表面處理丨沉錫工藝深度解讀

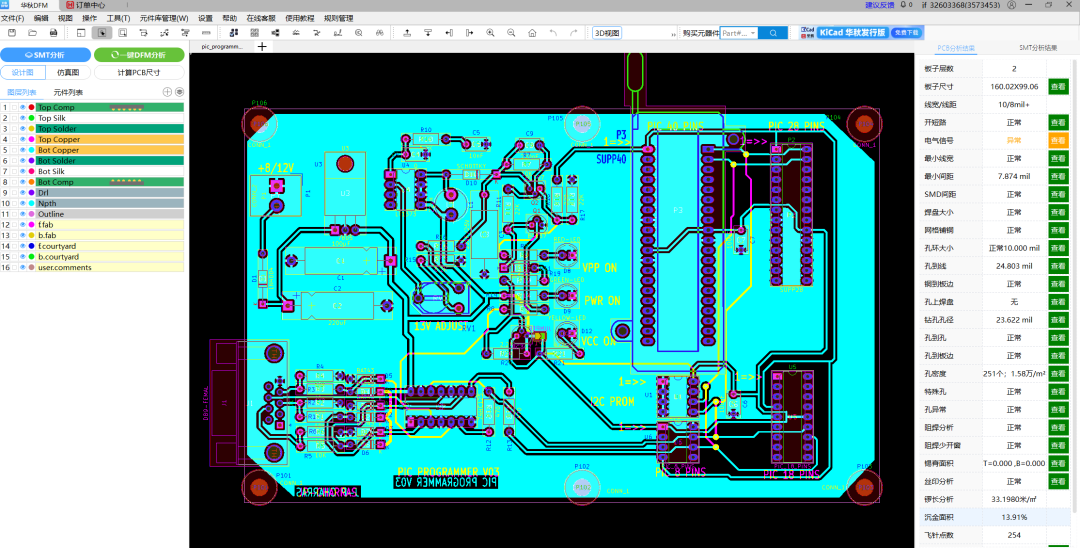

華秋DFM支持KiCad PCB了

【華秋DFM】V4.6正式上線:工程師的PCB設(shè)計(jì)“好搭子”來(lái)了!

【華秋DFM】V4.6正式上線:工程師的PCB設(shè)計(jì)“好搭子”來(lái)了!

7個(gè)常見(jiàn)的DFM問(wèn)題,及其對(duì)PCB制造的影響

7個(gè)常見(jiàn)的DFM問(wèn)題,及其對(duì)PCB制造的影響

評(píng)論