在電子系統測試與設計中,工程師常常使用功率放大器來驅動諸如CBB電容、MLCC電容或傳輸電纜等容性負載。當輸入信號為方波時,一個常見的困惑隨之產生:為何一個標稱功率充足的放大器,在實際驅動容性負載時會出現波形失真、振鈴,甚至觸發過流保護?

問題的根源往往不在于放大器的額定功率,而在于其帶寬與輸出電流能力在容性負載下的相互作用。

1

電容的電氣特性

ic(t) = C·dv(t)/dt

其中:ic(t)是瞬時電流、C 是電容值

dv(t)/dt 是電容兩端電壓的變化率

這個公式清晰地指出:要為電容建立快速變化的電壓,必須提供巨大的瞬時電流。

2

量化與帶寬、壓擺率的約束

實際方波的上升沿tr(從 10% Vm到 90%Vm的時間)是帶寬的直接體現,工程上常用經驗公式:BW≈0.35/tr, 其本質是帶寬對高頻細節的放大能力,轉化為電壓爬升的時間限制。

壓擺率的本質是放大器內部有限電流對補償電容充放電速度的物理限制。

當壓擺率≥帶寬所對應的dv/dt上限時,帶寬才是主導約束;若壓擺率更低,電流則由壓擺率決定,帶寬約束失效。

實際最大 dv/dt = min (帶寬對應的dv/dt上限,壓擺率),進而決定容性負載電流峰值。

3

從“方波邊沿”類比到“正弦波”

驅動容性負載時,最嚴峻的考驗發生在電壓變化最快的時刻,即方波的上升沿和下降沿。這個快速變化的邊沿,其高頻特性可以由一個等效頻率的正弦波來近似,正弦波在“峰值附近”是“電壓變化最快的時刻。這兩個“最快變化時刻”的 dv/dt,在工程上可近似相等。

時域看:當壓擺率占主導時,等效頻率f=fSR=SR/(πV_p)。當帶寬占主導時,電流峰值由ic(t) = C * dv/dt 決定,而實際的 dv/dt 被功放的帶寬所限制,即等效頻率f=帶寬頻率fBW。

頻域看:在頻率最大處,電容的阻抗 Xc = 1/(2πfC) 決定了電流的大小。

4

實際案例

功放型號:HAP-4001

功放帶寬及壓擺率:30kHz 40V/us

輸出電壓:輸出為2kHz頻率的40Vp方波

負載CBB電容:100nF

計算瞬時峰值電流:

40Vp下30kHz對應的dv/dt上限=V_pp·BW/0.35=6.8V/us

實際最大 dv/dt = min(6.8V/us,40V/us)=6.8V/us,

實際輸出帶寬占主導,即f=fBW

Xc =1/(2πf C) ≈50Ω

I_p = V_p / Xc = 40V /50Ω ≈ 800mAp

實際測量電流峰值為950mAp,在誤差范圍內

圖示黃色為電壓波形、藍色為電流波形

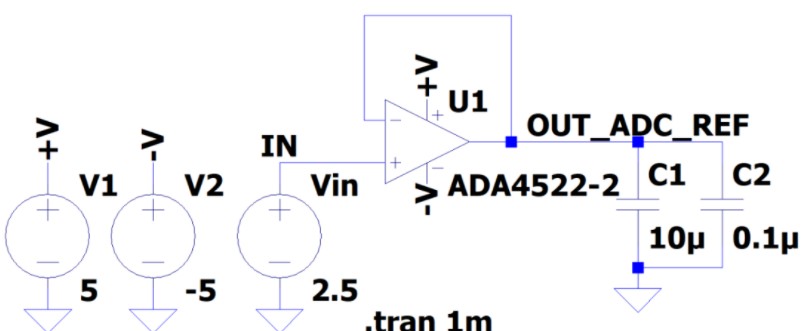

接線示意圖

5

總結

當功放驅動容性負載(如CBB電容)并輸入方波時,對方波上升/下降沿的響應需要非常大的瞬時電流。這個瞬時電流的需求程度,在壓擺率充足的情況下,取決于功放的帶寬。帶寬越低,方波邊沿越緩,瞬時電流需求越小,但波形失真越嚴重;帶寬越高,方波邊沿越陡,瞬時電流需求越大,但波形越保真。

在實際應用中,如果必須驅動大容性負載,除了選擇高壓擺率、大電流的功放外,還可以考慮在輸出端串聯一個小電阻來阻尼振蕩,但這會進一步限制可用帶寬和電流。

-

電流

+關注

關注

40文章

7212瀏覽量

141191 -

功率放大器

+關注

關注

104文章

4315瀏覽量

139982 -

帶寬

+關注

關注

3文章

1040瀏覽量

43352

發布評論請先 登錄

使用高側開關控制器解決驅動容性負載挑戰的各種方法

用tas5630驅動容性負載,經常出現損壞芯片的現象,怎么解決?

寬帶放大器驅動容性負載、感性負載,有哪些注意事項?

如何利用RISO及CL補償穩定驅動容性負載的運算放大器?

采用極少的元件 解決高速驅動容性負載比較困難測試

方波驅動容性負載:功放帶寬與電流需求詳解

方波驅動容性負載:功放帶寬與電流需求詳解

評論