以下文章來源于逍遙設計自動化;作者逍遙科技

引言

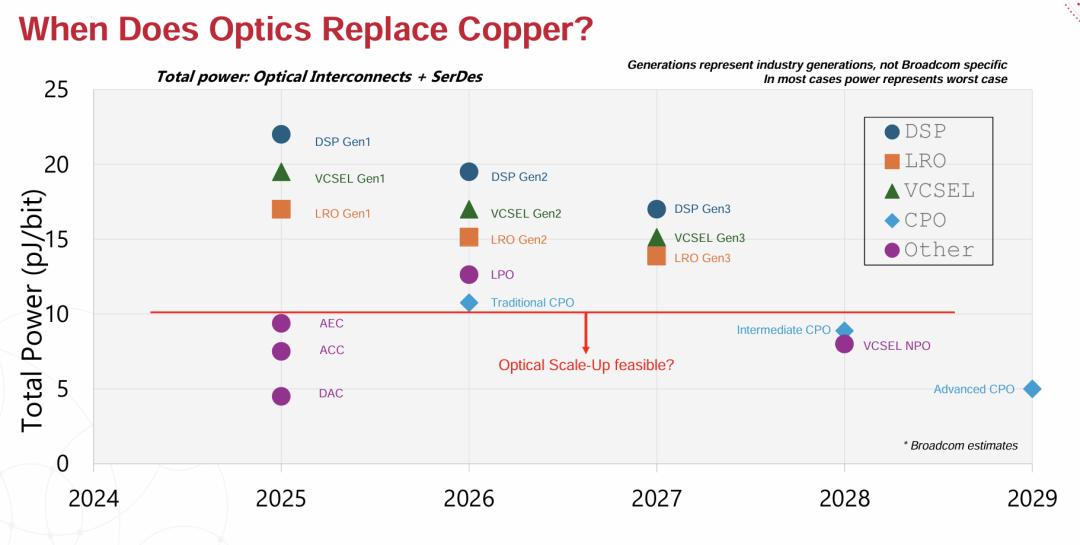

人工智能、云計算和高性能計算的快速發展對現代數據中心的數據傳輸帶寬和能源效率提出了更高的要求。傳統的可插拔光學模塊雖然在維護和升級方面具有便利性,但隨著網絡交換機容量超過12.8太比特每秒,這些模塊已經成為性能瓶頸。交換機ASIC與前面板光收發器之間的長電氣走線會引入顯著的插入損耗、串擾,功耗可達15到20皮焦耳每比特。光電共封裝技術和3D光電子集成技術為這些挑戰提供了新的解決方案,從根本上重新定義了光學組件和電子組件在單一封裝內的協同工作方式[1]。

01從可插拔模塊到光電共封裝技術的演進

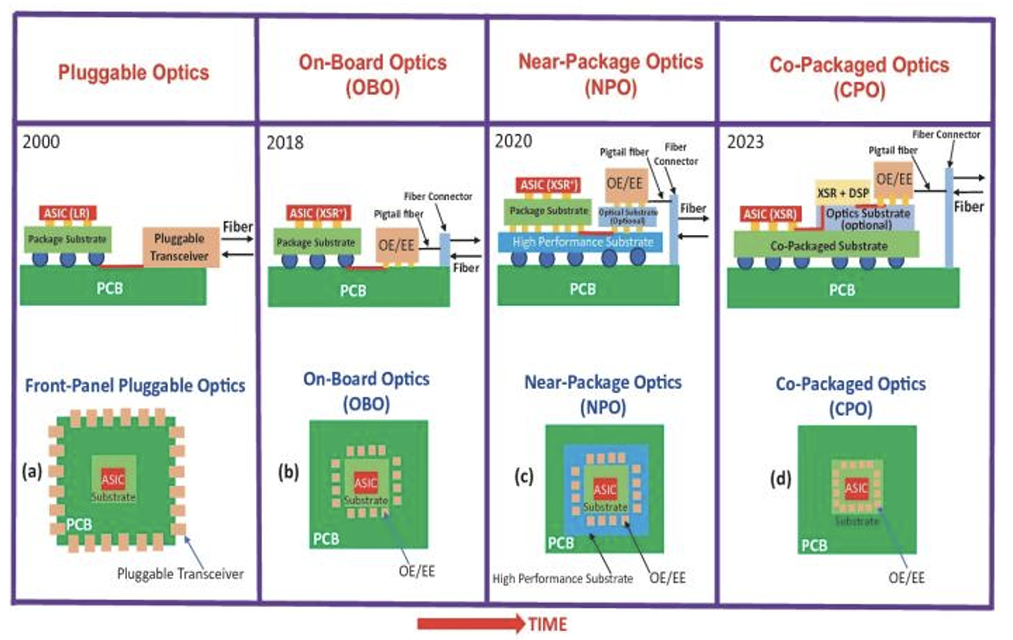

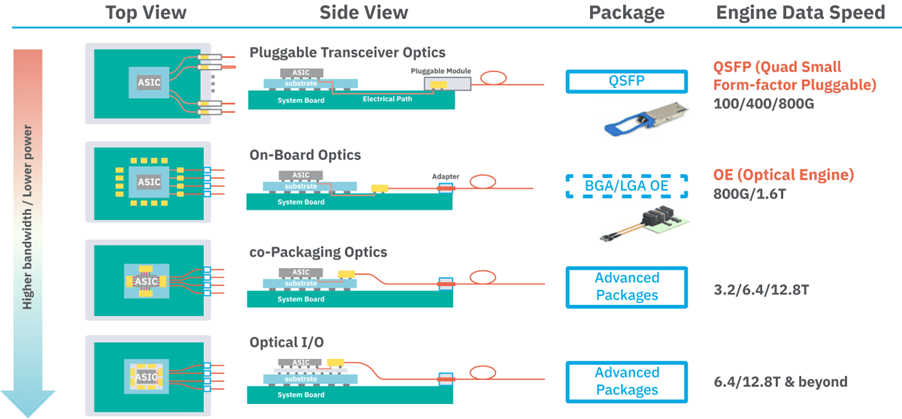

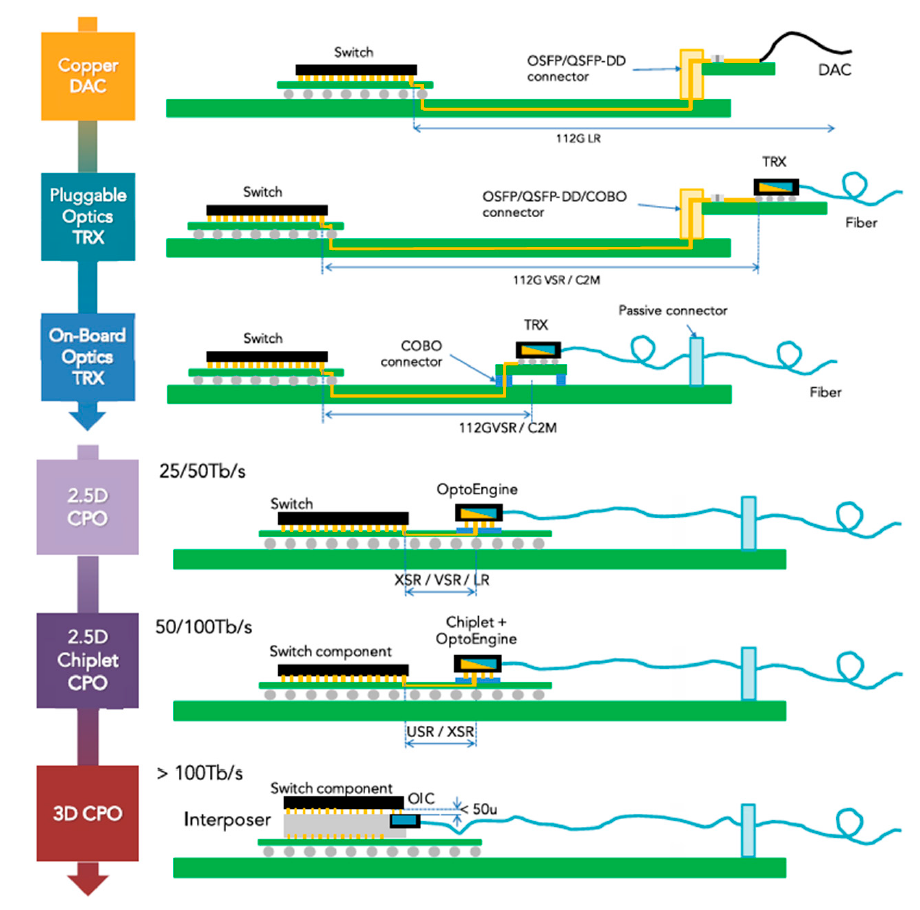

光電共封裝技術的發展歷程體現了對更高帶寬密度和更低功耗的持續追求。在2000年代初期,光收發器主要作為可插拔模塊存在于服務器板的外圍位置,遵循SFP和QSFP等標準,這些標準使得靈活部署和系統升級變得容易。然而,隨著總交換容量不斷攀升,ASIC與可插拔光模塊之間的電氣互連因為印刷電路板長走線上的插入損耗、串擾和高功耗而變得越來越成問題。

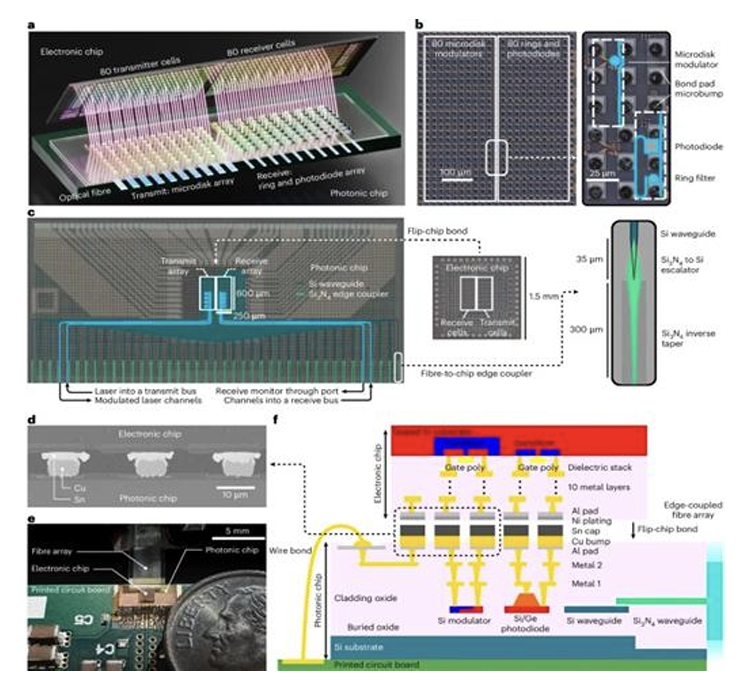

圖1:從可插拔收發器到光電共封裝技術的演進過程,顯示了光學和電氣組件如何隨時間逐步靠近ASIC,在每個階段都減少了互連長度并降低了功耗。

業界首先嘗試通過板上光學模塊來解決這些限制,將光引擎放置在與交換ASIC相同的電路板上,位置更靠近ASIC。這種方法縮短了電氣路徑長度,部分緩解了信號劣化問題,同時相比傳統可插拔模塊降低了能耗。盡管有這些改進,板上光學模塊設計仍然受到機械和熱約束的限制,這限制了其在需要多太比特總帶寬的下一代系統中的可擴展性。

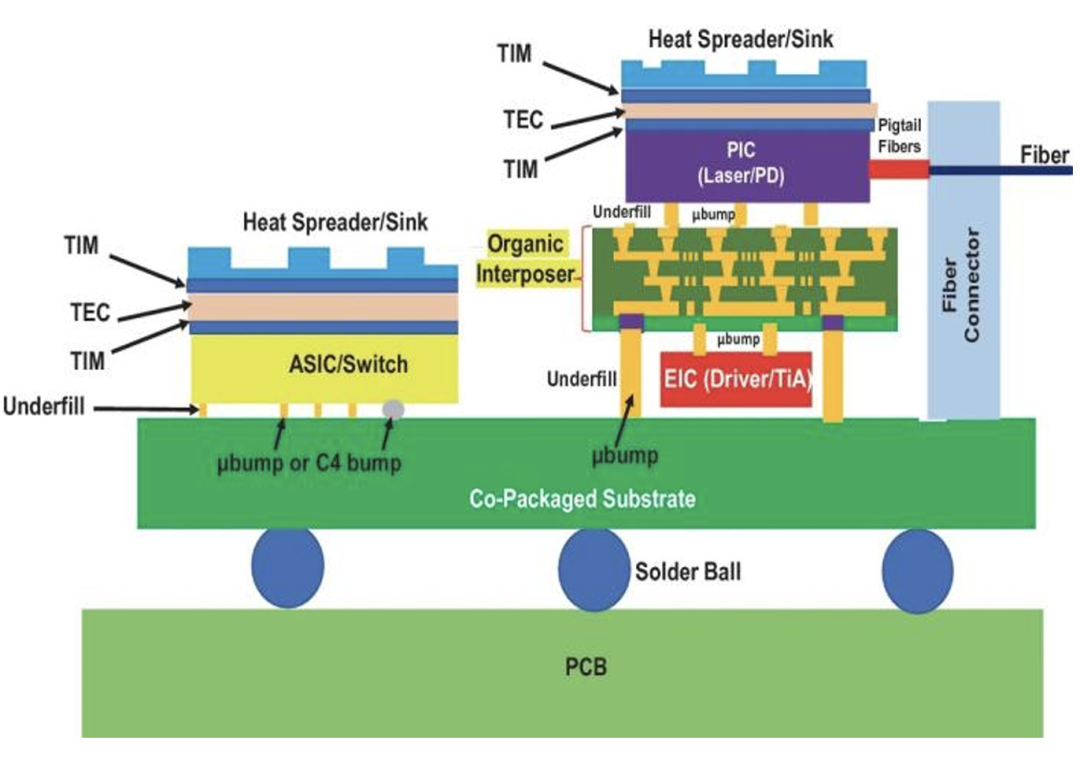

光電共封裝技術將集成推向了新的高度,通過使用硅interposer、硅通孔和異質集成方法,將光收發器直接安裝在與交換ASIC相同的封裝內。通過在共同基板上將光學和電子器件緊密放置,光電共封裝技術將電氣鏈路長度大幅縮短至僅幾毫米,將能耗降低到5至10皮焦耳每比特的范圍,同時增強信號完整性,實現25.6太比特每秒及更高的總帶寬。

02理解2.5D和3D集成策略

從傳統2D封裝到先進的2.5D和3D集成的轉變代表了光電子集成芯片和電子集成線路在物理排列和電氣連接方式上的基礎性轉變。在傳統2D封裝中,光電子集成芯片和電子集成線路并排放置在共享基板上,通過引線鍵合或倒裝芯片技術連接。雖然這種方法在制造角度相對簡單,但較長的橫向互連限制了性能并增加了寄生損耗。

圖2:從2D到3D集成的電子和光電子集成芯片集成選項演進,顯示了每種方法如何通過日益復雜的封裝架構減少互連長度并提高帶寬密度。

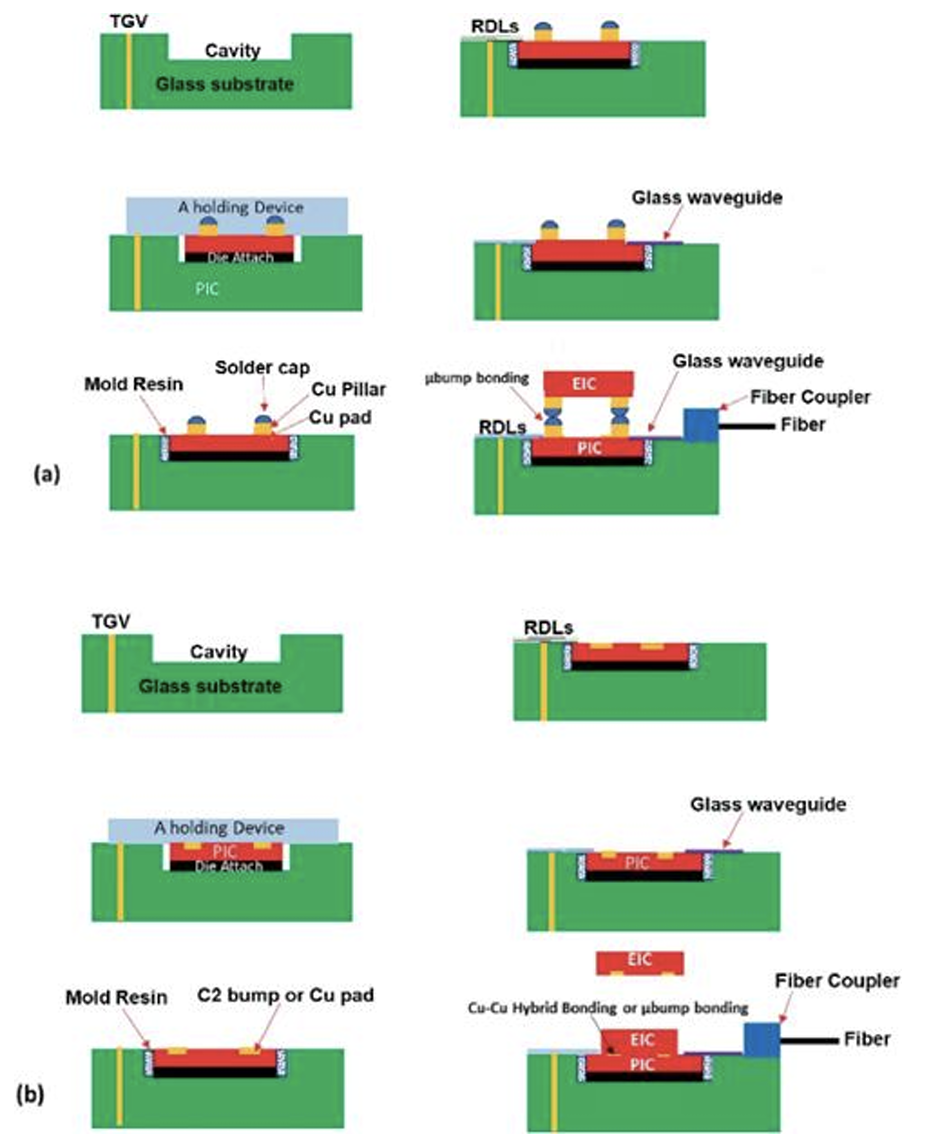

2.5D封裝在芯片和封裝基板之間引入了interposer層。這種interposer通常由硅或玻璃制成,包含硅通孔或玻璃通孔,在芯片之間實現高密度垂直連接和精細間距橫向布線。硅interposer提供出色的布線密度和精細間距連接,使其在高性能計算和GPU集成應用中得到廣泛部署。然而,硅interposer成本較高,并且由于體硅層的存在可能帶來散熱挑戰。帶有玻璃通孔的玻璃interposer已經成為有吸引力的替代方案,提供更低的射頻衰減、更好的機械性能,以及潛在的更低制造成本。

英特爾的嵌入式多芯片互連橋(EMIB)代表了另一種2.5D變體,將小型硅橋嵌入有機基板中,創建局部高帶寬互連,而無需在整個封裝上使用完整的interposer。這種方法在需要的地方提供出色的電氣性能,同時通過限制昂貴硅面積的使用來保持成本效益。在所有2.5D配置中,芯片保持在interposer表面上橫向放置,與標準2D方法相比最小化了互連長度,同時保持相對簡單的熱管理,因為芯片不會直接堆疊在彼此之上。

真正的3D集成采用根本不同的方法,通過垂直堆疊芯片,通過垂直互連創建直接的芯片到芯片連接。在這些系統中,光電子集成芯片可以作為具有類似硅通孔的垂直連接的interposer層,或者光電子芯片和驅動線路可以使用混合鍵合等先進技術直接正面對背面鍵合。這種架構實現了最短的互連長度和最低的插入損耗,直接轉化為能源效率和帶寬密度的改善。最近的3D堆疊CPO引擎演示已經實現了每秒多太比特的吞吐量,證明了垂直集成架構的技術可行性。

然而,3D集成引入了必須仔細管理的嚴重熱和機械挑戰。當高功率ASIC直接堆疊在熱敏感的光電子集成芯片上方時,來自ASIC的熱量會導致光學諧振器的波長漂移、激光器效率下降以及調制器性能不穩定。先進的熱管理策略變得必不可少,包括使用高導熱性的熱界面材料、金屬散熱片、熱電冷卻器,在某些情況下,還包括集成在interposer或基板內的微流體冷卻。

03硅基光電子與VCSEL方法的比較

CPO的實現沿著兩條不同的技術路線發展,每條路線在性能、成本和應用要求之間提供不同的權衡。基于硅基光電子的CPO利用成熟的互補金屬氧化物半導體制造基礎設施在硅基板上創建集成光子線路。這些系統通常在1310納米或1550納米附近的電信波長工作,與單模光纖接口,實現高達2公里的擴展傳輸距離。硅基光電子在需要密集波分復用的應用中表現出色,在密集波分復用中,不同波長的多個光通道共享同一根光纖,顯著增加總帶寬密度。

硅基光電子與現有CMOS代工廠的兼容性為在超大規模數據中心和電信互連中擴展到多太比特吞吐量提供了清晰的路徑。先進的硅光電子收發器在商業原型中已經證明了接近5到10皮焦耳每比特的能源效率,實驗室演示在優化條件下將這一范圍進一步降低。然而,硅基光電子在封裝成本和assembly公差方面面臨挑戰,特別是在與單模光纖的精確對準方面,即使是微米級的對準偏差也會導致顯著的耦合損耗。

基于垂直腔面發射激光器的CPO采用不同的方法,在850到1060納米之間的較短波長工作,通常與多模光纖接口。VCSEL陣列展示了卓越的能源效率,一些實現在短距離鏈路上達到1到2皮焦耳每比特。多模光纖的較大纖芯直徑大大放寬了與單模光纖耦合相比的對準公差,簡化了封裝并降低了制造成本。IBM和Coherent的MOTION項目等工業原型驗證了緊湊的玻璃基板VCSEL模塊,具有皮焦耳每比特級的能源效率和高集成密度。

圖3:用于51.2太比特每秒交換機的CPO模塊詳細結構,說明了ASIC、電子集成線路和光電子集成芯片在共同基板上的異質集成以及全面的熱管理系統。

基于VCSEL方法的主要限制是傳輸距離,在多模光纖上很少超過幾百米。單模VCSEL的最新發展旨在擴展可能的鏈路距離,可能會模糊短距離VCSEL和長距離硅基光電子之間的傳統界限。硅基光電子和基于VCSEL引擎之間的最終選擇在很大程度上取決于系統級因素,包括每通道所需的數據速率、現有光纖基礎設施、成本目標、熱預算,以及應用是優先考慮擴展傳輸距離還是在較短距離上最大化能源效率。

04制造和生產挑戰

要在商業規模上充分發揮CPO和3D光電子技術的潛力,需要克服幾個制造和生產方面的挑戰。硅基光電子和混合集成中的良率和工藝控制仍然是活躍的研究領域,特別是隨著III-V增益材料在硅上的芯片鍵合和晶圓級異質集成技術的成熟。光刻、沉積和鍵合步驟中的工藝變化會導致光學諧振器的波長偏移和耦合效率低下,從而導致大量良率損失。正在開發先進的工藝監控技術、統計建模方法和面向良率的設計方法,以最小化性能分散并實現可接受的生產良率。

圖4:使用玻璃interposer技術和微凸點鍵合在共封裝基板上ASIC、電子集成線路和光電子集成芯片的3D異質集成的制造工藝。

對準公差和耦合損耗在先進封裝中構成顯著障礙,其中光纖或波導之間輕微對準偏差導致的插入損耗會嚴重降低整體鏈路預算,特別是在更高數據速率下。為了應對這些挑戰,研究人員開發了無源對準結構、自對準耦合接口和3D打印波導,作為放寬assembly公差同時保持低損耗的方法。光纖連接和芯片到芯片互連的新方法,如光柵耦合器和帶有點尺寸轉換器的邊緣耦合,正在密集開發中,以降低成本并簡化制造復雜性。

圖5:來自APSUNY的硅基光電子PDK,顯示了基于玻璃的interposer集成的示意工藝,包括微凸點鍵合和銅到銅混合鍵合配置。

熱可靠性和功耗管理對于避免密集光電封裝中的性能漂移和過早失效非常關鍵。溫度波動會影響硅和其他材料的折射率,導致諧振偏移并隨時間增加插入損耗。新型封裝解決方案采用高導熱基板、先進散熱方法,以及熱敏感性降低的設計,如無熱波導和微諧振器。通過改進的器件設計(包括硅上量子點激光器和低電壓調制器)降低整體發熱量,有助于在高數據吞吐量條件下保持穩定運行。

大規模制造的可擴展性必須得到解決,以滿足數據中心和新興高速光鏈路的需求。從小眾研究規模制造過渡到標準化300毫米CMOS生產線涉及適配代工廠兼容設計、確保大晶圓上的工藝均勻性,以及實施多項目晶圓流片,使多個客戶能夠分擔制造成本。晶圓級鍵合、微轉印和基于chiplet的集成等技術正在獲得動力,用于實現大規模異質光電系統,具有更高的吞吐量和更低的每個芯片成本。

光子技術生態系統歷史上缺乏電子行業數十年來享有的組件庫、設計規則檢查和自動化布局的統一基礎設施。具有全面組件庫、緊湊模型和經過驗證的工藝配方的標準化工藝設計套件將加速CPO和3D光電子技術的產品開發周期并縮短上市時間。雖然考慮到不同代工廠的專有器件庫和設計規則,完全的跨代工廠統一性仍然不現實,但該行業正在朝著標準化建模方法和設計驗證流程邁進,以實現可移植性。在封裝和assembly層面,標準化的理由更加充分,新興的封裝和assembly設計套件定義了關鍵的接口規范,包括光學和電氣輸入輸出引腳排列、光纖連接幾何形狀、對準公差以及直接影響互操作性的熱和機械約束。

05從數據中心到量子網絡的應用

CPO和3D光電子集成的融合繼續通過增加的帶寬能力、降低的功耗和增強的可擴展性來改變多個行業。在超大規模數據中心和人工智能集群中,對能夠實時傳輸大量數據的高密度、低功耗互連的需求推動了集成光學技術的快速采用。通過將光收發器直接與網絡交換ASIC集成,CPO降低了傳輸損耗和功耗,同時降低了總擁有成本。新興方法利用3D光電子封裝將垂直腔面發射激光器和光電子chiplet集成到同一封裝中,隨著人工智能工作負載持續增加,實現了高比特率和改進的系統可靠性。

在高性能計算系統中,隨著計算能力向百億億次級擴展,帶寬瓶頸和熱約束構成了顯著挑戰。集成光子互連為傳統銅鏈路提供了有吸引力的替代方案,在大幅降低功耗預算的情況下提高了性能。3D光子集成已經成為開發可行的量子網絡和混合量子計算節點的核心,為光子產生、路由和檢測提供緊湊和穩定的架構。在封裝級別結合電子和光電子組件可實現下一代高性能計算和新興量子應用所需的超低延遲通信基礎設施。

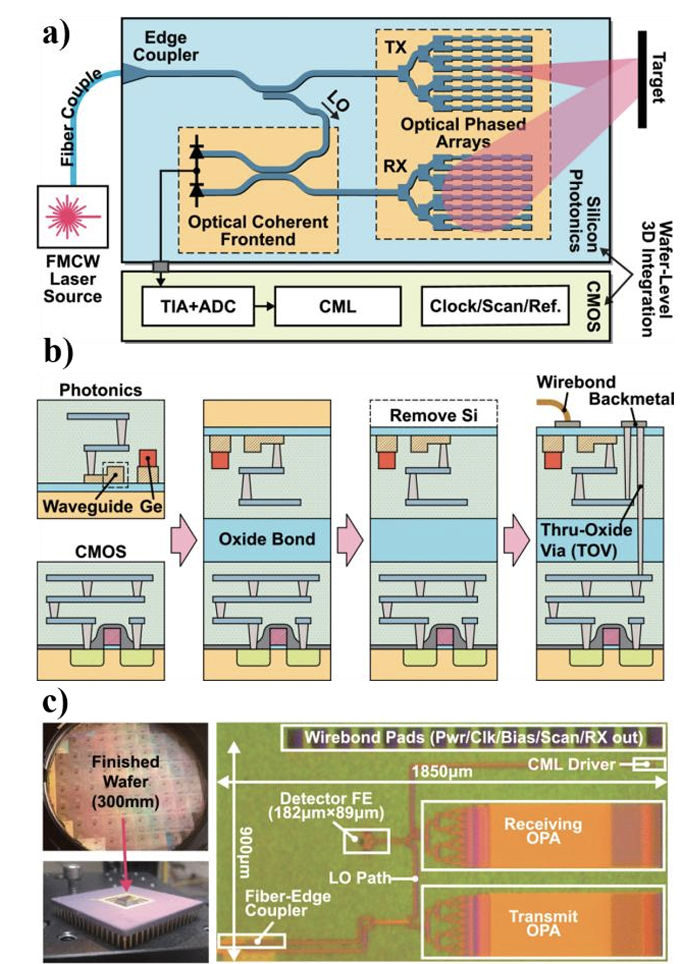

圖6:集成相干激光雷達系統的系統架構和芯片照片,展示了如何在緊湊的光電封裝中通過全雙工光鏈路連接處理器和存儲器。

未來的第五代和第六代移動網絡依賴于密集的前傳和回傳鏈路,這些鏈路需要高數據速率、靈活的部署能力和出色的信號完整性。CPO可以通過將光學接口與基帶處理ASIC共同定位來顯著降低集中式無線接入網絡中的功耗。3D光電子封裝促進了射頻和光電子組件的無縫集成,支持下一代模擬和數字前傳解決方案,這些解決方案提高了頻譜效率和網絡可擴展性,用于大規模連接器件和超低延遲通信。

圖7:用于相干激光雷達的硅基光電子與CMOS的晶圓級3D集成,包括制造細節以及帶有封裝器件的完整300毫米晶圓。

用于自動駕駛車輛的光學傳感和激光雷達系統將從集成光子技術的進步中大量受益,特別是隨著汽車行業向高分辨率固態解決方案發展。在單個3D光電子封裝中集成光學相控陣、相干檢測線路和信號處理模塊可以減小外形尺寸,同時提高性能。片上光子激光雷達架構旨在實現更緊湊和更節能的傳感器,這對于在苛刻的真實世界環境中實現穩健和安全的自主導航非常關鍵。

航空航天和國防部門需要用于衛星通信和雷達系統的安全、高帶寬且通常具有抗輻射能力的光鏈路。3D集成光電子技術可以通過在緊湊封裝中將光收發器與電子控制線路合并,減輕基于空間平臺的尺寸、重量和功率挑戰。微波光子技術和光波束成形技術同樣通過緊湊的共封裝模塊得到增強,在可靠性和性能至關重要的雷達、電子戰和安全通信系統中提供改進的靈活性和性能。

06未來方向和新興技術

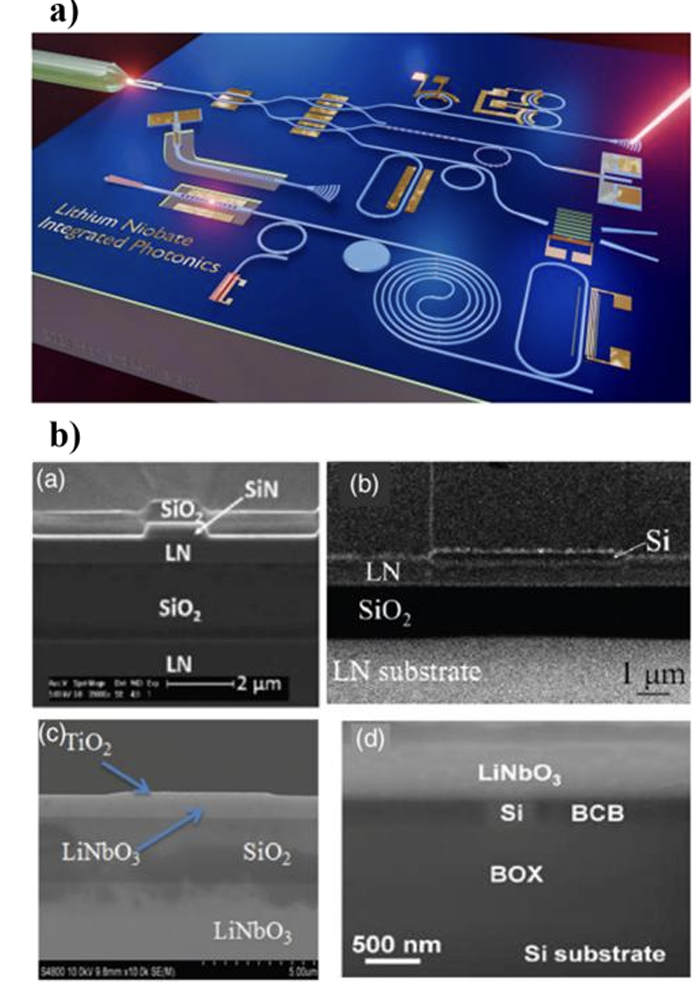

隨著CPO和3D光電子技術的持續發展,幾個前瞻性研究領域有望塑造集成光學技術的未來發展。下一代硅基光電子集成越來越多地探索純硅之外的異質材料平臺,特別是薄膜鈮酸鋰調制器,可提供超低驅動電壓和高線性度,用于實現高階調制格式。最近的工作已經證明使用基于鈮酸鋰的集成調制器進行320吉比特每秒相干傳輸,具有出色的插入損耗和帶寬特性。

圖8:薄膜鈮酸鋰上的集成光電子器件,顯示了器件結構和混合波導配置,可實現高性能調制。

與此同時,III-V材料在硅上的異質集成尋求克服硅平臺上的激光器集成挑戰。通過將鋁鎵銦砷增益區域鍵合到硅波導上,已經演示了混合III-V-硅激光器,而在300毫米晶圓上直接外延生長量子點激光器表明了真正單片解決方案的潛力。使用晶圓鍵合技術將超低噪聲激光器3D集成到硅基光電子上強調了先進封裝如何將性能推向遠超傳統2D方法的水平。

人工智能工作負載的快速增長引發了對光計算和光電子加速器的強烈興趣,這些加速器可以提供比純電子系統更高的吞吐量和更低的延遲。用于深度學習推理的相干納米光子線路的突破性演示說明了全光矩陣乘法的能源效率優勢。最近的光電子張量核心擴展了這種方法,在集成光子線路中顯示并行卷積操作。在2.5D或3D封裝中與電子器件共同集成的更大規模硅光電子加速器可以實現多吉赫茲操作,延遲僅為幾納秒,為邊緣和數據中心的人工智能開辟了新的可能性。

圖9:3D集成光電系統,將電子單元陣列與光電子器件陣列結合用于光計算應用。

量子信息科學已經轉向集成光子技術作為可擴展、穩定和高保真量子系統的關鍵推動者。開發量子互連以光學方式連接分布在多個節點上的量子比特已成為實現分布式量子計算和安全量子通信的核心挑戰。在金剛石和III-V半導體中的固態量子比特方面已經取得了顯著進展,其中片上光子線路在量子處理元件之間路由單光子或糾纏光子對。具有遠程糾纏的多節點量子網絡的演示強調了在集成平臺上構建多用戶量子通信系統的可行性。

單片集成與基于chiplet方法之間的基本辯論繼續塑造集成光子技術的未來軌跡。單片解決方案承諾在單一工藝流程中無縫共同制造電子和光電子器件,可能最小化寄生損耗并在規模上優化系統性能,盡管工藝復雜性和良率仍然是顯著障礙。基于chiplet的封裝通過允許在將光電子芯片和電子ASIC組裝到interposer上之前分別優化而提供設計靈活性,這種策略已經在一些高帶寬光學輸入輸出chiplet中商業化,可以與計算芯片共封裝以實現多太比特數據速率。最優的前進路徑可能最終結合兩種方法的優點,單片集成選定的光電子元件,同時將專用組件(如某些激光源)卸載到可以通過晶圓鍵合或倒裝芯片assembly無縫集成的chiplet上。

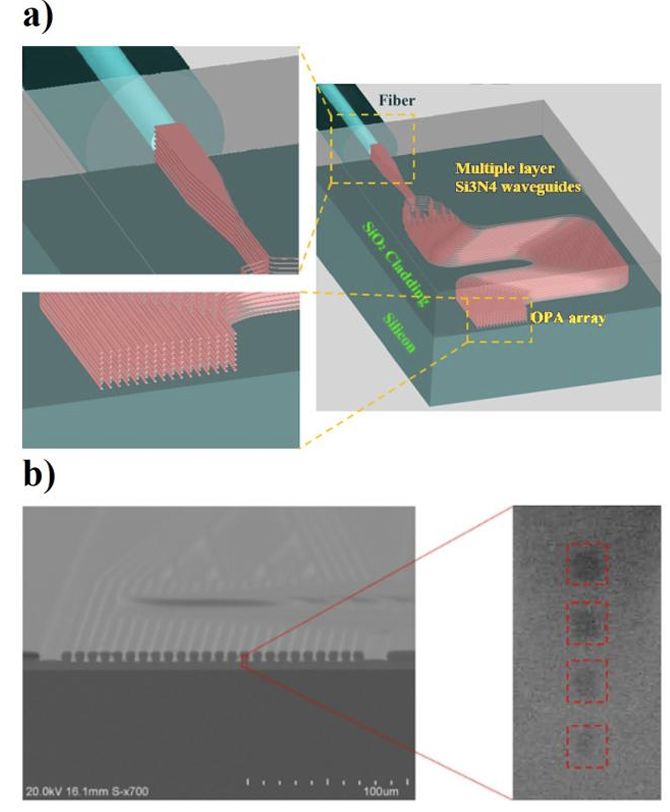

圖10:為單模光纖與芯片之間的高耦合效率而設計的多層氮化硅基3D光學相控陣,包括示意圖和掃描電子顯微鏡圖像。

隨著人工智能和云規模環境中的數據吞吐量繼續呈指數增長,CPO將成為未來交換機和加速器設計不可或缺的部分。先進封裝技術、異質集成技術和新型光電子材料的持續融合為實現長期追求的個位數甚至亞皮焦耳每比特互連目標創造了路徑。通過光子技術研究人員、封裝工程師、系統架構師和制造專家之間持續的多學科協作,CPO和3D光電子集成將塑造未來計算和網絡系統的性能、可擴展性和能源效率。

關于我們:

天府逍遙(成都)科技有限公司(Latitude Design Automation Inc.)是一家專注于半導體芯片設計自動化(EDA)的高科技軟件公司。我們自主開發特色工藝芯片設計和仿真軟件,提供成熟的設計解決方案如PIC Studio、MEMS Studio和Meta Studio,分別針對光電芯片、微機電系統、超透鏡的設計與仿真。我們提供特色工藝的半導體芯片集成電路版圖、IP和PDK工程服務,廣泛服務于光通訊、光計算、光量子通信和微納光子器件領域的頭部客戶。逍遙科技與國內外晶圓代工廠及硅光/MEMS中試線合作,推動特色工藝半導體產業鏈發展,致力于為客戶提供前沿技術與服務。

-

封裝技術

+關注

關注

12文章

599瀏覽量

69303 -

可插拔

+關注

關注

0文章

4瀏覽量

9359 -

光學模塊

+關注

關注

0文章

28瀏覽量

12187

原文標題:3D光電子技術與光電共封裝技術

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

CDMA演進技術綜合介紹

用于高速光電組件的光焊球陣列封裝技術

400G可插拔光模塊與相干DWDM結合實現長距離DCI

光電共封裝

LPO與CPO:光互連技術的轉折與協同發展

AI時代下光模塊的發展前景

光電共封裝技術的實現方案

從可插拔模塊到光電共封裝技術的演進

從可插拔模塊到光電共封裝技術的演進

評論