SiC碳化硅MOSFET串擾的本征機理與根本解法:基于器件層面電容分壓與足夠深的負壓關斷

碳化硅MOSFET的串擾問題并非不可戰勝的頑疾,其本質是器件寄生參數在高dV/dt激勵下的物理響應。市面上常見的有源米勒鉗位、外并電容等措施,受限于物理阻抗瓶頸和效率損耗,只能在應用層面做有限的補救,屬于“隔靴搔癢”。

真正的根本解決辦法在于回歸器件物理本源:

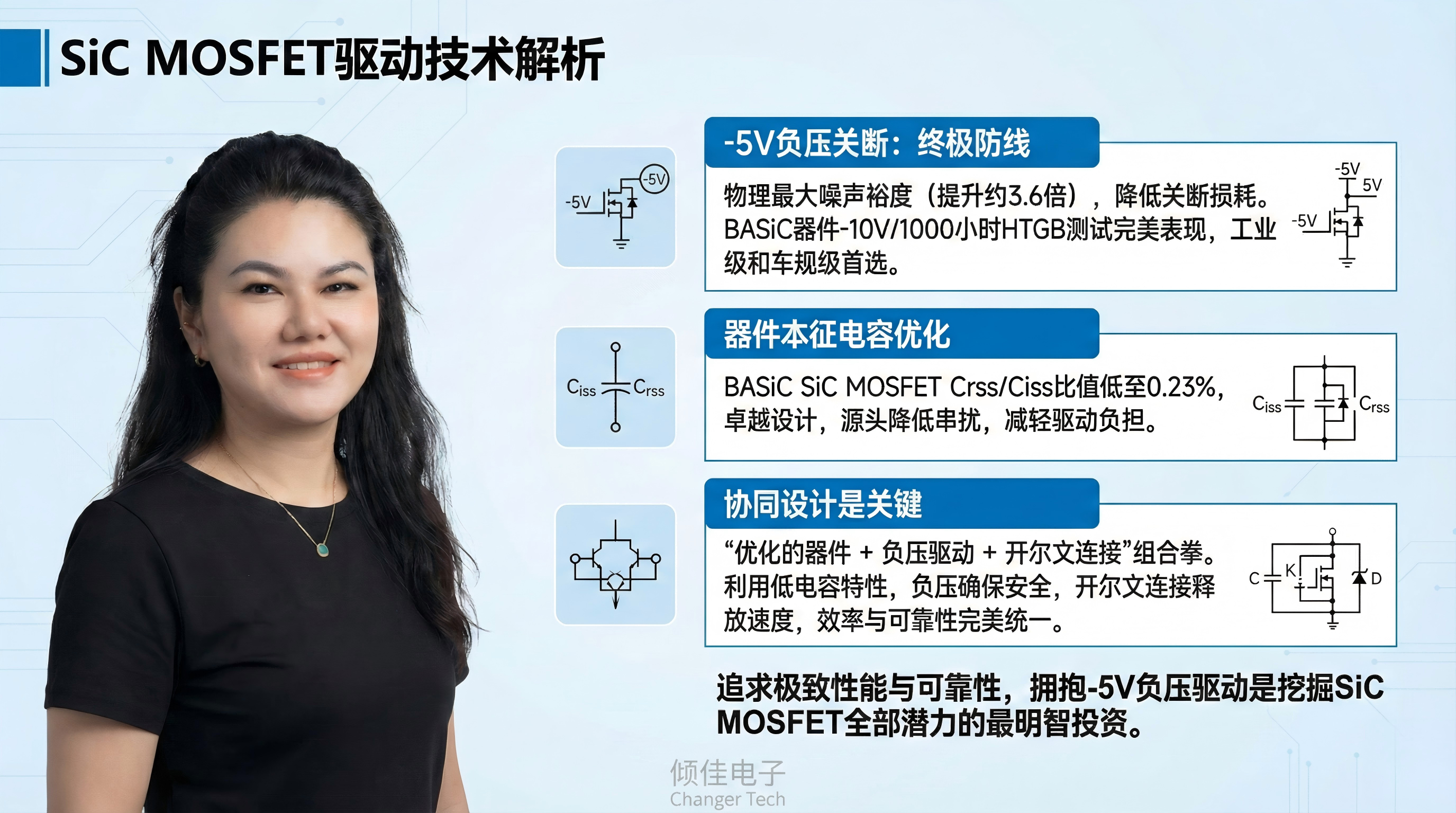

利用電容分壓原理:通過先進的芯片工藝將 Crss?/Ciss? 比率壓低至千分之二(0.002)量級,從源頭上將感應電壓“扼殺”在安全閾值之下。

構筑負壓防線:利用 -5V 的深負壓關斷,為高溫下降低的閾值電壓提供堅實的“護城河”,確保在任何瞬態干擾下器件都能死死鎖住在關斷狀態。

傾佳電子(Changer Tech)是一家專注于功率半導體和新能源汽車連接器的分銷商。主要服務于中國工業電源、電力電子設備和新能源汽車產業鏈。傾佳電子聚焦于新能源、交通電動化和數字化轉型三大方向,代理并力推BASiC基本半導體SiC碳化硅MOSFET單管,SiC碳化硅MOSFET功率模塊,SiC模塊驅動板等功率半導體器件以及新能源汽車連接器。?

傾佳電子楊茜致力于推動國產SiC碳化硅模塊在電力電子應用中全面取代進口IGBT模塊,助力電力電子行業自主可控和產業升級!

傾佳電子楊茜咬住SiC碳化硅MOSFET功率器件三個必然,勇立功率半導體器件變革潮頭:

傾佳電子楊茜咬住SiC碳化硅MOSFET模塊全面取代IGBT模塊和IPM模塊的必然趨勢!

傾佳電子楊茜咬住SiC碳化硅MOSFET單管全面取代IGBT單管和大于650V的高壓硅MOSFET的必然趨勢!

傾佳電子楊茜咬住650V SiC碳化硅MOSFET單管全面取代SJ超結MOSFET和高壓GaN 器件的必然趨勢!

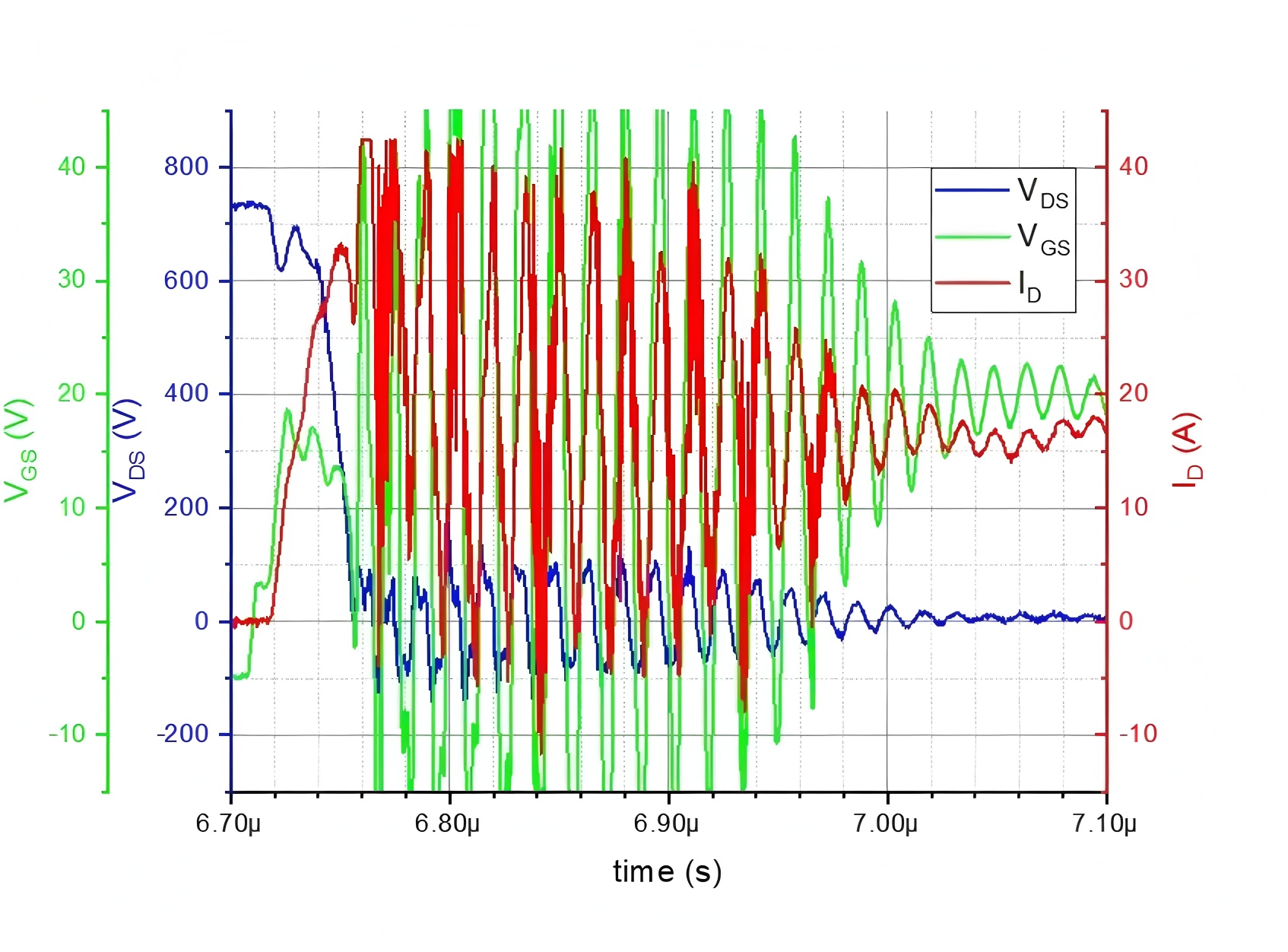

隨著以碳化硅(SiC)為代表的寬禁帶半導體技術在固態變壓器SST、儲能變流器PCS、Hybrid inverter混合逆變器、戶儲、工商業儲能PCS、構網型儲能PCS、集中式大儲PCS、商用車電驅動、礦卡電驅動、風電變流器、數據中心HVDC、AIDC儲能、服務器電源、重卡電驅動、大巴電驅動、中央空調變頻器、光伏儲能系統以及高密度電源轉換器中的大規模應用,功率電子行業正經歷著一場由開關速度(dV/dt)和功率密度驅動的革命。然而,SiC MOSFET器件特有的超高速開關特性——其漏源電壓變化率(dVDS?/dt)常超過50 V/ns甚至達到100 V/ns——引發了嚴峻的柵極串擾(Crosstalk)挑戰。串擾現象表現為在器件關斷狀態下,由于互補橋臂的高速動作而在柵極感應出寄生電壓尖峰,若處理不當,將導致器件誤導通(False Turn-on),進而引發直通短路(Shoot-through),不僅增加開關損耗,更嚴重威脅系統的長期可靠性。

當前行業內存在多種抑制串擾的工程手段,包括有源米勒鉗位(Active Miller Clamp, AMC)、外并聯柵源電容(Cgs,ext?)以及增加關斷柵極電阻等。然而,基于對半導體物理機制的深入剖析以及對基本半導體(BASIC Semiconductor)B3M/BMF系列與行業競品(Wolfspeed, Infineon, STMicroelectronics等)Datasheet數據的詳盡對比分析,有源米勒鉗位(Active Miller Clamp, AMC)、外并聯柵源電容(Cgs,ext?)以及增加關斷柵極電阻外部電路措施本質上均為“隔靴搔癢”式的補救手段,往往以犧牲器件的動態性能或增加系統復雜度為代價。

真正解決SiC MOSFET串擾問題的根本辦法(Fundamental Solution)在于器件層面的本征優化與驅動策略的深度結合:即通過微觀結構設計實現極低的反向傳輸電容與輸入電容之比(Crss?/Ciss?) ,構建具有極強衰減能力的內部分壓網絡;同時配合足夠深的負壓關斷余量(Deep Negative Bias, typically -5V) ,以抵消高溫下閾值電壓(Vth?)的漂移效應。唯有從這兩點入手,方能在保留SiC高速低損耗特性的前提下,實現本質上的抗串擾免疫。

第一章 高頻開關環境下串擾現象的物理本源

要理解為何外部抑制措施僅是“隔靴搔癢”,必須首先深入解構SiC MOSFET在納秒級開關瞬態下的物理行為。與傳統硅基IGBT不同,SiC MOSFET是單極性器件,且漂移層更薄、摻雜濃度更高,這賦予了其極低的結電容和極快的開關速度,但也使得其柵極對寄生參數的敏感度呈指數級上升。

1.1 米勒效應與位移電流的微觀機制

在典型的半橋(Half-Bridge)拓撲中,上下橋臂的SiC MOSFET交替導通。當上管(High-Side Device)接收到開通指令并開始導通時,其漏源電壓(VDS?)迅速下降。由于半橋中點的電位被強制拉高,處于關斷狀態的下管(Low-Side Device)將承受一個極高的正向電壓變化率(dVDS?/dt)。

此時,下管必須被視為一個由寄生電容構成的復雜網絡。其中,連接柵極(Gate)與漏極(Drain)的反向傳輸電容(Crss?,即Cgd?)扮演了關鍵的耦合通道角色。根據電容的電流-電壓微分關系 i=C?dtdV?,漏極電壓的劇烈變化將在Crss?上激發出瞬態位移電流(Displacement Current),即米勒電流(Miller Current, iM?):

iM?=Crss?(VDS?)?dtdVDS??

由于SiC器件的dV/dt能力極強(>50 V/ns),即便Crss?僅為幾十皮法(pF),所產生的瞬態電流也可高達數安培。例如,對于一個Crss?為20pF的器件,在100 V/ns的電壓跳變下,將產生2A的瞬態電流 。

這股電流必須從漏極流向柵極,并通過柵極回路流回源極(Source)。在這個過程中,柵極回路的總阻抗決定了最終疊加在柵極氧化層上的電壓幅值。然而,問題的核心在于,即便柵極驅動回路的阻抗為零,器件內部的物理結構依然構成了一個分壓網絡。

1.2 本征電容分壓器模型

為了剝離外部驅動電路的影響,透視問題的本質,我們可以將處于關斷狀態的SiC MOSFET等效為一個純粹的電容分壓網絡。在該模型中,柵極節點(Internal Gate Node)位于兩個電容之間:

上方電容:反向傳輸電容 Crss?(即Cgd?),連接漏極高壓端。

下方電容:輸入電容 Ciss? 的主要組成部分——柵源電容 Cgs?,連接源極低壓端。

當漏極電壓發生 ΔVDS? 的跳變時,根據電荷守恒原理,如果忽略外部泄漏和驅動回路的初始影響,感應到柵極內部的電壓變化量 ΔVGS? 由兩個電容的阻抗比決定。在高頻瞬態下,阻抗 Z=1/jωC,因此分壓關系與電容值成反比:

VGS,induced?≈VDS??Crss?+Cgs?Crss??=VDS??Ciss?Crss??

這個公式揭示了串擾問題的物理本質:感應電壓的大小直接取決于器件內部寄生電容的比值(Capacitance Ratio) 。這是一個純粹由器件晶圓設計(Die Design)決定的本征參數。

如果這個比值過大(例如 1:50),那么在800V的母線電壓沖擊下,柵極將本能地感應出16V的電壓。這種電壓水平不僅遠遠超過了SiC MOSFET通常2V-4V的開啟閾值(Vth?),甚至可能接近柵極氧化層的擊穿電壓(通常為-10V/+22V左右),導致器件的永久性失效或壽命劇減 3。

1.3 閾值電壓的溫度漂移特性

SiC MOSFET的物理特性決定了其閾值電壓具有負溫度系數(Negative Temperature Coefficient)。隨著結溫(Tj?)的升高,電子在溝道表面的遷移率特性發生變化,導致Vth?顯著降低。

依據基本半導體(BASIC Semiconductor)提供的B3M系列Datasheet數據 :

在室溫(25°C)下,典型閾值電壓約為 2.7V。

在高溫(175°C)下,典型閾值電壓降低至 1.9V。

這意味著在實際工況的高溫環境下,器件抵抗誤導通的“防線”被迫后撤了近0.8V-1.0V。對于一個僅僅依靠0V關斷的系統來說,1.9V的安全裕量在高達100 V/ns的dV/dt噪聲環境中顯得極其脆弱。任何微小的電感耦合或電容分壓效應,只要產生超過1.9V的電壓尖峰,就會導致上下橋臂直通,引發災難性的短路電流。

因此,串擾問題的根本機理可以概括為:在高頻高壓的開關動作下,SiC MOSFET固有的米勒電容將漏極電壓瞬變耦合至柵極,其幅值由器件的電容比率決定;而SiC材料較低且隨溫度下降的閾值電壓,使得這一耦合電壓極易突破安全界限,造成誤導通。

第二章 為什么外部抑制措施只是“隔靴搔癢”

在工程實踐中,為了應對串擾問題,設計人員往往采用多種外部電路方案。然而,通過對電路寄生參數的量化分析,可以證明這些方案都未能觸及問題的核心,且往往伴隨著嚴重的性能懲罰。

2.1 有源米勒鉗位(AMC)的局限性與阻抗瓶頸

有源米勒鉗位(Active Miller Clamp)是傳統硅基IGBT驅動中常用的技術。其原理是在檢測到柵極電壓低于某一閾值后,通過驅動芯片內部的一個輔助晶體管將柵極直接短接到負電源或地,試圖提供一個低阻抗通路來泄放米勒電流。

然而,在SiC MOSFET的應用場景中,AMC面臨著無法克服的物理障礙:內部柵極電阻(RG,int?) 。

SiC MOSFET芯片內部,從邦定點(Bonding Pad)到實際的MOS元胞(Cell)之間,存在著由多晶硅柵極材料和金屬互連線構成的分布電阻。

查閱基本半導體B3M011C120Y的規格書 4,其內部柵極電阻 RG,int? 典型值為 1.5Ω。

對于模塊產品如BMF120R12RB3 4,該值約為 0.7Ω。

當高速dV/dt產生巨大的米勒電流(例如3A - 5A)時,這股電流必須流經RG,int?才能到達外部的驅動器引腳。根據歐姆定律,僅在芯片內部就會產生壓降:

Vdrop?=IMiller??RG,int?≈3A?1.5Ω=4.5V

這意味著,即便外部的AMC電路反應速度無限快、阻抗為零,能夠將外部柵極引腳完美鉗位在-5V,芯片內部最核心的柵極氧化層電位依然會被抬升4.5V,達到-0.5V。如果外部關斷電壓僅為0V,那么內部柵極電位將直接飆升至4.5V,瞬間超過閾值電壓(1.9V),引發誤導通 。

此外,AMC電路本身存在動作延遲。SiC的開關過程往往在十幾個納秒內完成 7,而AMC電路的檢測和動作延時通常在幾十納秒量級,往往在鉗位電路起作用之前,第一波也是最危險的電壓尖峰已經發生。因此,依賴AMC來解決SiC串擾,如同在洪水爆發后才開始堆沙袋,無法從源頭消除隱患。

2.2 外并聯電容(Cgs,ext?)的效率懲罰

另一種常見的做法是在柵極和源極之間并聯一個外部電容,旨在人為增大Ciss?,從而優化分壓比:

Rationew?=Ciss?+Cext?Crss??

雖然這種方法在理論上降低了感應電壓的幅值,但它引入了巨大的副作用——開關損耗的激增。

柵極驅動電路必須在每個開關周期內對這個額外的電容進行充放電。這不僅增加了驅動功率損耗(Pdrv?=Qg??Vgs??fsw?),更嚴重的是,它顯著降低了柵極電壓的上升和下降斜率(Slew Rate)。

SiC MOSFET的核心優勢在于其極短的開關轉換時間(trise?,tfall?),這使得其開關過程中的電壓-電流重疊損耗(Overlap Loss)極低。人為增加Cgs?會直接延長這個重疊時間,導致開關損耗(Eon?,Eoff?)成倍增加 5。為了解決一個可靠性問題而犧牲掉SiC最核心的效率優勢,無疑是一種“因噎廢食”的策略。

2.3 增大關斷柵極電阻(Rg,off?)的妥協

增加關斷電阻可以降低dV/dt,從而減小米勒電流的幅值。但這同樣是一種以犧牲性能為代價的妥協。降低dV/dt直接意味著開關速度變慢,損耗增加。對于追求高功率密度和高效率的SiC應用而言,這違背了設計初衷 。

綜上所述,外部措施要么受限于物理連接(如內部電阻阻擋了AMC的效果),要么以犧牲核心性能指標為代價(如外接電容增加了損耗)。它們都未能解決“由于器件內部電容比例不佳而產生高感應電壓”這一根本矛盾,因此這些外部措施本質為“隔靴搔癢”。

第三章 根本解決辦法之一:器件本征電容分壓比的極致優化

既然外部電路無法觸及芯片內部的電位分布,那么解決問題的根本出路必然在于芯片本身的設計。這就引出了“根本解決辦法”的第一支柱:通過器件微觀結構的優化,構建具有天然抗干擾能力的電容分壓比(Crss?/Ciss? Ratio)。

3.1 黃金比率的物理意義

前文公式 VGS?≈VDS??(Crss?/Ciss?) 表明,如果能將Crss?做得極小,或者在保持Crss?較低的同時適當維持較大的Ciss?,就能將感應電壓限制在安全范圍內。

理想的目標是,即便在最惡劣的dV/dt條件下(例如800V母線電壓瞬間施加),通過分壓原理計算出的柵極感應電壓也應低于器件的最小閾值電壓。即:

800V?Ratio

這意味著電容比率應當小于 0.0025(即1/400)。

3.2 行業主流器件的電容比率基準測試

為了驗證這一理論,并探究基本半導體(BASIC Semiconductor)在此方面的技術路線,我們基于提供的Datasheet以及Wolfspeed、Infineon、ST等競品的數據 ,進行了詳細的參數對比。

表1:1200V級SiC MOSFET本征電容比率橫向評測

3.3 數據深度解析:BASIC的設計哲學

從上表數據中可以清晰地觀察到,基本半導體(BASIC)的B3M系列和Wolfspeed的C3M系列在電容比率控制上處于行業領先水平,其比率均被壓低至 0.002 - 0.003 區間。 相比之下,Infineon和ST的同類產品比率在 0.006 至 0.015 之間,高出2到6倍。

這種差異并非偶然,而是源于深層的器件結構設計哲學 :

極低的Crss?: 無論BASIC還是Wolfspeed,其Crss?均控制在10-20pF級別(針對分立器件)。這通常通過引入屏蔽柵(Shielded Gate)結構或優化的JFET區域設計來實現,利用源極電位屏蔽層將大部分漏極電場截斷,使其無法直接耦合至柵極,從而大幅削減Cgd?。

適當保留Ciss?: 注意到BASIC的Ciss?(6000 pF)顯著高于Infineon(1900 pF)。這看似增加了柵極驅動電荷(Qg?),但在解決串擾問題上卻是一個精妙的權衡。較高的Ciss?(主要是Cgs?)充當了一個巨大的天然電荷“蓄水池”。當米勒電流注入柵極時,由于Cgs?很大,產生的電壓升(ΔV=Q/Cgs?)就被顯著攤薄了。

實戰推演:

假設在800V母線電壓下發生硬開關,VDS?在極短時間內上升800V。

對于BASIC B3M011C120Y (Ratio 0.0023):

Vspike?≈800V×0.0023=1.84V

這個電壓低于其最小閾值電壓2.3V。這意味著,從物理層面上,該器件具有天然的免疫力。即便柵極完全懸空,它也不會誤導通。這就是所謂的“根本解決辦法”。

高達12V的感應電壓將瞬間擊穿任何安全防線,必須依賴極強的外部有源鉗位電路才能勉強工作。

因此,基本半導體通過工藝手段實現的極低電容比率,從源頭上消除了產生高幅值串擾電壓的物理基礎,使得外部抑制電路變得多余。

第四章 根本解決辦法之二:足夠深的負壓關斷余量

除了降低干擾電壓的幅值,另一個維度的解決思路是提高系統的抗干擾閾值。這就是“根本解決辦法”的第二支柱:使用足夠深的負壓(Deep Negative Bias)來關斷器件。

4.1 閾值電壓的“底線”保衛戰

如前所述,SiC MOSFET的閾值電壓Vth?隨溫度升高而降低。對于基本半導體的B3M011C120Y,其Vth?從常溫的2.7V降至高溫下的1.9V。如果采用0V關斷,意味著只要干擾電壓超過1.9V,器件就會誤導通。

考慮到PCB走線電感引起的振蕩,以及Crss?非線性變化帶來的瞬態效應,1.9V的噪聲容限(Noise Margin)在工業級應用中是極其危險的。

4.2 負壓關斷的數學邏輯

引入負壓關斷電壓(VGS(off)?=VEE?),實質上是人為拉低了柵極的基準電位,從而顯著提升了安全裕量。

安全裕量=Vth(min)?@Tj,max??(VEE?+Vspike?)

如果我們采用 -5V 作為關斷電壓:

基準電位變為 -5V。

高溫閾值電壓為 1.9V。

器件要發生誤導通,柵極電壓必須從 -5V 上升到 +1.9V,總跨度需要 6.9V。

相比于0V關斷時的1.9V裕量,-5V負壓將抗干擾能力提升了 3.6倍。即便前文提到的電容分壓效應產生了一個3V的尖峰,疊加在-5V的基礎上,柵極電壓也僅上升至-2V,依然處于絕對安全的深關斷區域。

4.3 行業推薦值的博弈:-5V vs 0V

通過對比各家廠商的Datasheet推薦值,我們可以看到基本半導體在這一策略上的堅定性。

表2:各廠商推薦關斷電壓與閾值裕量分析

分析:

Infineon推廣0V關斷(其CoolSiC系列的Vth?設計得較高,達3.5V-4.5V),這簡化了驅動電路,但犧牲了部分的抗干擾裕量。

Wolfspeed推薦-4V,保留了較好的裕量。

基本半導體(BASIC) 則明確推薦 -5V 。這一策略與其低電容比率的設計相得益彰:

低比率確保了產生的尖峰很小(例如<2V)。

-5V深負壓確保了即便有尖峰,也距離閾值(+1.9V)有巨大的安全距離(>6V)。

這種“雙保險”策略(物理層面的低感應 + 電路層面的高門檻)構成了抑制串擾的完整閉環,使得器件在極端惡劣的工況下也能由內而外地保持“冷靜”。

第五章 基本半導體方案的系統級優勢與實施建議

5.1 系統簡化與可靠性提升

采用“低電容比率 + 深負壓”這一根本方案,對系統設計帶來了顯著的正面連鎖反應:

驅動電路簡化:不再需要復雜的有源米勒鉗位電路,也不需要調試外并電容的大小。驅動器只需提供標準的+18V/-5V電平即可,PCB布局更加簡潔,寄生參數更易控制。

柵極氧化層壽命延長:雖然負壓增加了柵極氧化層的電場應力,但由于從源頭上抑制了正向尖峰,避免了柵極電壓反復沖擊正向極限值,減少了柵極振蕩帶來的疲勞損傷。基本半導體的可靠性測試(如HTGB)驗證了-5V長期工作的穩定性 。

EMI性能優化:由于不需要通過增大柵極電阻來抑制串擾,設計者可以放心地使用較小的Rg?來追求極高的開關速度,從而在不惡化EMI(因振蕩減少)的前提下,大幅降低開關損耗。

5.2 實施建議

基于本報告的分析,針對使用基本半導體SiC MOSFET的工程師提出以下建議:

選型階段:優先查閱Datasheet中的AC特性表,計算 Crss?/Ciss? 比率。優選比率小于0.003的器件(如B3M系列)。

驅動設計:嚴格遵循廠家推薦,設計能夠穩定輸出-5V關斷電壓的電源。避免使用單極性(0V)驅動,除非應用場景dV/dt極低。

PCB布局:雖然器件本身具有抗擾能力,但仍需最小化驅動回路的共源極電感(Common Source Inductance),建議采用凱爾文源極(Kelvin Source, 4-pin封裝)連接方式,以進一步剝離功率回路對驅動回路的磁耦合干擾。

結論

深圳市傾佳電子有限公司(簡稱“傾佳電子”)是聚焦新能源與電力電子變革的核心推動者:

綜上所述,碳化硅MOSFET的串擾問題并非不可戰勝的頑疾,其本質是器件寄生參數在高dV/dt激勵下的物理響應。市面上常見的有源米勒鉗位、外并電容等措施,受限于物理阻抗瓶頸和效率損耗,只能在應用層面做有限的補救,屬于“隔靴搔癢”。

真正的根本解決辦法在于回歸器件物理本源:

利用電容分壓原理:通過先進的芯片工藝將 Crss?/Ciss? 比率壓低至千分之二(0.002)量級,從源頭上將感應電壓“扼殺”在安全閾值之下。

構筑負壓防線:利用 -5V 的深負壓關斷,為高溫下降低的閾值電壓提供堅實的“護城河”,確保在任何瞬態干擾下器件都能死死鎖住在關斷狀態。

基本半導體(BASIC Semiconductor)的B3M/BMF系列產品正是這一“根本解法”的典型代表,通過極致的參數優化,為高頻功率變換器提供了無需額外復雜電路保護的魯棒性,釋放了寬禁帶半導體的全部潛能。

廠商

器件型號

Ciss? (Typ)

Crss? (Typ)

比率 (Crss?/Ciss?)

測試條件

BASIC

B3M011C120Y

6000 pF

14 pF

0.0023

800V, 100kHz

BASIC

B3M013C120Z

5200 pF

~14 pF*

~0.0027

800V, 100kHz

BASIC

BMF120R12RB3

7700 pF

20 pF

0.0026

800V, 100kHz

BASIC

BMF540R12KA3

33600 pF

70 pF

0.0021

800V, 100kHz

Wolfspeed

C3M0016120K

6085 pF

13 pF

0.0021

1000V, 1MHz

Infineon

IMZ120R045M1

1900 pF

13 pF

0.0068

800V, 1MHz

ROHM

SCT3022KL

2879 pF

14 pF

0.0049

800V, 1MHz

器件型號

推薦關斷電壓 VGS(off)?

VGS(th)? Min (25°C)

靜態安全裕量

BASIC B3M011C120Y

-5 V

2.3 V

7.3 V

BASIC BMF240R12KHB3

-5 V

2.7 V (Typ)

~7.7 V

Wolfspeed C3M0016120K

-4 V

1.8 V

5.8 V

Infineon IMZ120R045M1

0 V (允許 -5V)

3.5 V

3.5 V

傾佳電子成立于2018年,總部位于深圳福田區,定位于功率半導體與新能源汽車連接器的專業分銷商,業務聚焦三大方向:

新能源:覆蓋光伏、儲能、充電基礎設施;

交通電動化:服務新能源汽車三電系統(電控、電池、電機)及高壓平臺升級;

數字化轉型:支持AI算力電源、數據中心等新型電力電子應用。

公司以“推動國產SiC替代進口、加速能源低碳轉型”為使命,響應國家“雙碳”政策(碳達峰、碳中和),致力于降低電力電子系統能耗。代理并力推BASiC基本半導體SiC碳化硅MOSFET單管,BASiC基本半導體SiC碳化硅MOSFET功率模塊,BASiC基本半導體SiC模塊驅動板等功率半導體器件以及新能源汽車連接器。

-

MOSFET

+關注

關注

151文章

9674瀏覽量

233507 -

碳化硅

+關注

關注

26文章

3464瀏覽量

52338

發布評論請先 登錄

QDPAK封裝SiC碳化硅MOSFET安裝指南

SiC碳化硅MOSFET隔離驅動電源系統中負壓生成的物理機制與工程實現研究報告

SiC碳化硅MOSFET串擾抑制研究報告:基于電容分壓與負壓關斷機制全維解析

深度解析SiC碳化硅功率MOSFET米勒效應:物理機制、動態影響與橋式電路中的串擾抑制

碳化硅(SiC)MOSFET模塊硬并聯中環流產生的根本機理及綜合抑制策略

碳化硅 (SiC) MOSFET 分立器件與功率模塊規格書深度解析與應用指南

基本半導體碳化硅(SiC)MOSFET低關斷損耗(Eoff)特性的應用優勢

傾佳電子提供SiC碳化硅MOSFET正負壓驅動供電與米勒鉗位解決方案

SiC碳化硅MOSFET串擾的本征機理與根本解法:基于器件層面電容分壓與足夠深的負壓關斷

SiC碳化硅MOSFET串擾的本征機理與根本解法:基于器件層面電容分壓與足夠深的負壓關斷

評論