深度解析DS92LV1260:六路10位BLVDS解串器的卓越性能與設(shè)計要點(diǎn)

在當(dāng)今高速數(shù)據(jù)傳輸?shù)臅r代,解串器在保障數(shù)據(jù)高效、準(zhǔn)確傳輸方面發(fā)揮著至關(guān)重要的作用。今天,我們就來深入探討德州儀器(TI)的DS92LV1260六路10位BLVDS解串器,了解它的特性、工作模式以及設(shè)計中的關(guān)鍵要點(diǎn)。

文件下載:ds92lv1260.pdf

一、DS92LV1260概述

DS92LV1260將六個解串器集成到單芯片中,采用0.25μm CMOS工藝技術(shù)。它能夠同時對多達(dá)六路由德州儀器DS92LV1021或DS92LV1023總線LVDS串行器序列化后的數(shù)據(jù)流進(jìn)行解串操作。此外,該芯片還具備第七個串行輸入通道,可提供n + 1冗余功能。

特性亮點(diǎn)

- 多通道解串與冗余支持:可對一至六路帶有嵌入式時鐘的BusLVDS輸入串行數(shù)據(jù)流進(jìn)行解串,七個可選串行輸入支持解串流的n + 1冗余。

- 高性能時鐘與濾波:輸入并行時鐘速率高達(dá)40MHz,片上PLL濾波功能強(qiáng)大。

- 低功耗與寬溫運(yùn)行:單電源+3.3V供電,典型功耗在3.3V下為1.2W;工作溫度范圍為 -40°C至 +85°C,適用于工業(yè)環(huán)境。

- 高阻抗與安全設(shè)計:掉電時(Vcc = 0V)輸入呈高阻抗?fàn)顟B(tài);采用196引腳NFBGA封裝,內(nèi)置有限的ESD保護(hù)。

二、電氣特性與性能指標(biāo)

絕對最大額定值

| 了解器件的絕對最大額定值對于確保其安全運(yùn)行至關(guān)重要。DS92LV1260的主要絕對最大額定值如下: | 參數(shù) | 數(shù)值 |

|---|---|---|

| 電源電壓(Vcc) | -0.3至4V | |

| Bus LVDS輸入電壓(Rin +/-) | -0.3V至3.9V | |

| 最大封裝功耗(@25°C) | 3.7W | |

| 存儲溫度范圍 | -65°C至 +150°C | |

| 結(jié)溫 | +150°C | |

| 引腳溫度(焊接10秒) | +225°C | |

| ESD評級(人體模型) | >3KV | |

| ESD評級(機(jī)器模型) | >750V |

電氣特性參數(shù)

基本功能和每個解串器通道的規(guī)格與DS92LV1212A相似。以下是一些關(guān)鍵電氣特性參數(shù):

- LVCMOS/LVTTL直流規(guī)格:如高電平輸入電壓VIH、低電平輸入電壓VIL等,確保輸入信號的正確識別。

- 總線LVDS直流規(guī)格:包括差分閾值高電壓VTH、差分閾值低電壓VTL等,為數(shù)據(jù)傳輸提供穩(wěn)定的電氣環(huán)境。

- 時序要求:如REFCLK周期tRFCP、REFCLK占空比tRFDC等,保證時鐘信號的準(zhǔn)確性和穩(wěn)定性。

- 解串器開關(guān)特性:如RCLK周期tRCP、RCLK占空比tRDC等,影響數(shù)據(jù)的解串和輸出時序。

三、工作模式詳解

初始化

在DS92LV1260接收和解串?dāng)?shù)據(jù)之前,它與發(fā)送串行器設(shè)備必須對鏈路進(jìn)行初始化。具體步驟如下:

- 上電后,輸出保持在三態(tài),片上電源排序電路禁用內(nèi)部電路。當(dāng)Vcc達(dá)到Vcc OK(2.1V)時,每個解串器中的PLL開始鎖定到本地時鐘(REFCLK)。

- 解串器的PLL必須與串行器同步,以完成初始化。當(dāng)解串器的PLL鎖定到嵌入式時鐘時,LOCKn引腳變?yōu)榈碗娖剑行?shù)據(jù)出現(xiàn)在輸出端。

數(shù)據(jù)傳輸

初始化完成后,串行器將數(shù)據(jù)傳輸?shù)浇獯鳌4袛?shù)據(jù)流包括由串行器附加的起始位和停止位,用于對十個數(shù)據(jù)位進(jìn)行幀定界。串行器以12倍TCLK頻率傳輸數(shù)據(jù)和時鐘位,解串器鎖定到嵌入式時鐘,生成多個內(nèi)部數(shù)據(jù)選通信號,并將嵌入式時鐘驅(qū)動到RCLKn引腳。

重新同步

當(dāng)六個解串器中的任何一個失去鎖定時,它將自動嘗試重新同步。系統(tǒng)必須監(jiān)控LOCKn引腳,以確定數(shù)據(jù)何時有效。用戶可以選擇讓解串器重新同步到數(shù)據(jù)流,或者通過脈沖串行器的SYNC1或SYNC2引腳來強(qiáng)制同步。

掉電模式

掉電模式是一種低功耗睡眠模式,當(dāng)PWRDN引腳為低電平時,解串器進(jìn)入掉電模式。在掉電模式下,PLL停止工作,輸出進(jìn)入三態(tài),從而將電源電流降低到微安級別。退出掉電模式后,解串器進(jìn)入初始化狀態(tài)。

三態(tài)模式

當(dāng)系統(tǒng)將REN引腳驅(qū)動為低電平時,解串器進(jìn)入三態(tài)模式,此時所有輸出處于高阻態(tài)。當(dāng)REN引腳為高電平時,解串器恢復(fù)到之前的狀態(tài)。

四、設(shè)計考慮要點(diǎn)

電源管理

DS92LV1260的全CMOS設(shè)計使其本質(zhì)上是一種低功耗器件。在給解串器上電時,REFCLK輸入可以在解串器上電之前運(yùn)行,并且必須運(yùn)行才能使解串器鎖定到傳入數(shù)據(jù)。解串器輸出將保持在三態(tài),直到檢測到輸入數(shù)據(jù)傳輸并鎖定到傳入數(shù)據(jù)流。

信號傳輸與同步

為了實(shí)現(xiàn)數(shù)據(jù)傳輸,解串器必須與發(fā)射器進(jìn)行鎖相。可以通過解串器鎖定到傳入數(shù)據(jù)或串行器發(fā)送同步模式來實(shí)現(xiàn)鎖相。解串器的LOCKn輸出保持高電平,直到它鎖定到傳入數(shù)據(jù)流。

噪聲容限與抗干擾

解串器的噪聲容限是指它能夠容忍的輸入抖動(相位噪聲)量,以確保可靠地接收數(shù)據(jù)。各種環(huán)境和系統(tǒng)因素,如串行器的TCLK抖動、電源噪聲,以及傳輸介質(zhì)的ISI和VCM偏移等,都會影響噪聲容限。

熱插拔與傳輸介質(zhì)

所有BusLVDS設(shè)備都支持熱插拔,但需要遵循一定的規(guī)則。在插入時,確保接地引腳先接觸,然后是VCC引腳,最后是I/O引腳;在移除時,順序相反。DS92LV1260和解串器可以通過PCB走線或雙絞線電纜用于點(diǎn)對點(diǎn)配置,在點(diǎn)對點(diǎn)配置中,傳輸介質(zhì)只需在接收器端進(jìn)行端接。

PCB布局與電源系統(tǒng)

良好的PCB布局和電源系統(tǒng)設(shè)計對于DS92LV1260的性能至關(guān)重要。推薦的布局實(shí)踐包括:

- 使用至少四層PCB板,為電源系統(tǒng)提供低噪聲環(huán)境。

- 保持串行器和解串器靠近連接器,減少走線長度,確保信號完整性。

- 為每個BusLVDS設(shè)備添加旁路電容,提高電源濾波效果。

- 使用匹配傳輸線差分阻抗的端接電阻,減少反射和信號失真。

五、總結(jié)

DS92LV1260作為一款高性能的六路10位BLVDS解串器,具有多通道解串、冗余支持、低功耗等諸多優(yōu)點(diǎn)。在設(shè)計過程中,我們需要充分考慮電源管理、信號傳輸、噪聲容限、熱插拔、傳輸介質(zhì)以及PCB布局等方面的因素,以確保其在實(shí)際應(yīng)用中能夠穩(wěn)定、高效地工作。希望通過本文的介紹,能夠幫助電子工程師更好地理解和應(yīng)用DS92LV1260,為高速數(shù)據(jù)傳輸系統(tǒng)的設(shè)計提供有力支持。

你在使用DS92LV1260的過程中遇到過哪些問題?或者你對本文中的哪個部分有更深入的疑問?歡迎在評論區(qū)留言討論。

-

高速數(shù)據(jù)傳輸

+關(guān)注

關(guān)注

0文章

257瀏覽量

7188

發(fā)布評論請先 登錄

探索DS90LV110T:1到10 LVDS數(shù)據(jù)/時鐘分配器的卓越性能與應(yīng)用

探索DS92LV010A:高速低功耗總線收發(fā)器的卓越之選

探索DS92CK16:3V BLVDS 1到6時鐘緩沖/總線收發(fā)器的卓越性能與應(yīng)用

深入剖析DS92LV16:16位總線LVDS串行器/解串器的卓越性能與應(yīng)用

深入解析DS92LV8028 8通道10:1串行器

深入解析DS90LV001:800 Mbps LVDS緩沖器的卓越性能與應(yīng)用

解析DS92001:3.3V B/LVDS - BLVDS緩沖器的卓越性能與設(shè)計指南

深度解析DS25MB200:2.5 Gbps雙路CML復(fù)用器/緩沖器的卓越性能與應(yīng)用

DS92LV241x:5 - 50 MHz 24 位通道鏈路 II 串行器和解串器的深度解析

探索DS92LV0411/DS92LV0412:高速數(shù)據(jù)傳輸?shù)睦硐胫x

探索DS92LX2121/DS92LX2122:高性能通道鏈路III芯片組的深度解析

探索DS92LV242x:高速數(shù)據(jù)傳輸?shù)睦硐胫x

探索DS90UH940N-Q1:FPD-Link III轉(zhuǎn)CSI-2解串器的卓越性能與應(yīng)用

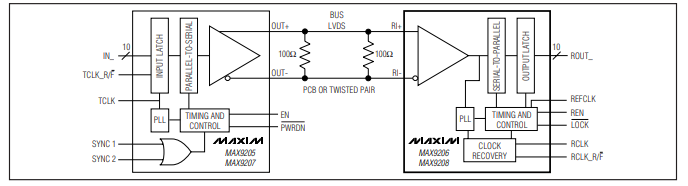

MAX9206/MAX9208 10位總線LVDS解串器技術(shù)手冊

深度解析DS92LV1260:六路10位BLVDS解串器的卓越性能與設(shè)計要點(diǎn)

深度解析DS92LV1260:六路10位BLVDS解串器的卓越性能與設(shè)計要點(diǎn)

評論