深入剖析DS125RT410低功耗多速率四通道重定時器

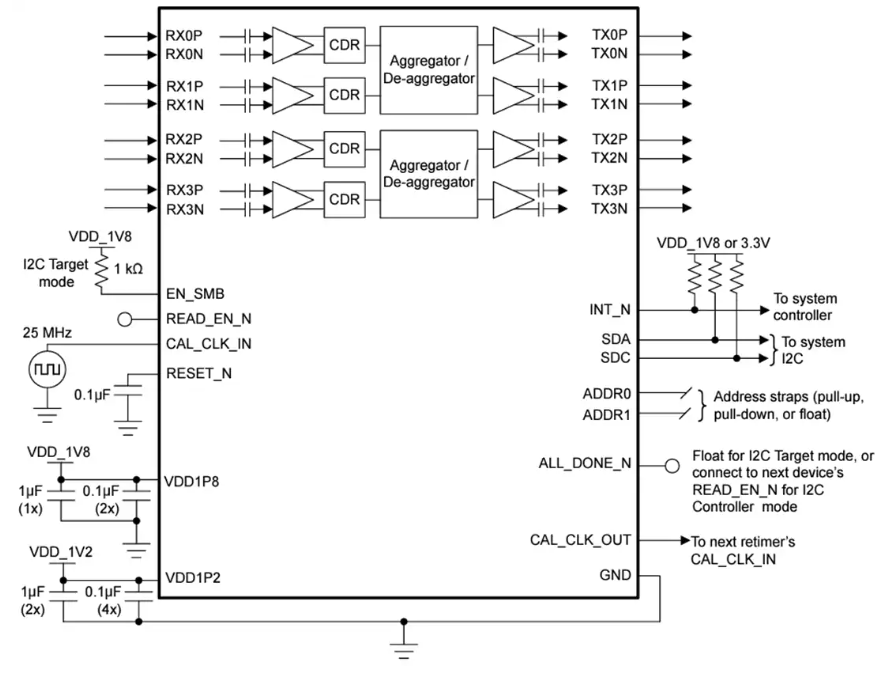

在高速通信領域,信號傳輸的質量和可靠性至關重要。DS125RT410作為一款低功耗多速率四通道重定時器,為解決長距離、有損和串擾嚴重的高速串行鏈路中的數據傳輸問題提供了有效的解決方案。今天,我就來和大家詳細探討一下這款芯片。

文件下載:ds125rt410.pdf

芯片概述及特性亮點

基礎信息與設計目標

DS125RT410是一款集成了信號調理功能的四通道重定時器,旨在實現高速串行鏈路中數據的可靠傳輸,達到 $BER <1 ×10^{-15}$ 的低誤碼率。它能夠適應從 9.8 到 12.5 Gbps 及相關子速率(2、4 和 8 分頻)的數據速率,支持多種通信協議。

特性一覽

- 高速數據處理能力:每個通道可獨立鎖定特定數據速率范圍,滿足多樣化的通信需求。

- 快速鎖定與低延遲:基于協議選擇模式實現快速鎖定操作,具備約 300 ps 的低延遲特性,確保數據傳輸的實時性。

- 自適應均衡與可調參數:自適應均衡功能在 5 GHz 時可提供高達 34 dB 的增益,同時支持可調的發射 $V_{OD}$(600 至 1300 mVp-p)和發射去加重(-15 dB),增加了設計的靈活性。

- 低功耗設計:典型的功耗(EQ + CDR + DE)為 150 mW/通道,有助于降低系統能耗。

- 可編程配置:通過 SMBus(I2C)接口或外部 EEPROM 實現可編程設置,方便用戶根據實際需求進行定制。

- 實時監測功能:片上眼圖監測器(EOM)和 PRBS 發生器可對高速串行數據進行實時測量,便于系統調試和現場優化。

引腳功能解析

| 芯片的引腳功能設計合理,涵蓋了高速差分輸入輸出、環路濾波器連接、參考時鐘輸入輸出、鎖定指示、SMBus 接口等多個方面,具體信息如下表所示: | PIN | V/O, TYPE(1) | DESCRIPTION | |

|---|---|---|---|---|

| NAME | NO. | |||

| HIGH - SPEED DIFFERENTIAL I/O | ||||

| RXPO RXNO | 1 2 | 1,CML | Inverting and non - inverting CML - compatible differential inputs to the equalizer. Nominal differential input impedance = 100 Q. | |

| RXP1 RXN1 | 4 5 | 1,CML | Inverting and non - inverting CML - compatible diferentia inputs to the equalizer. Nominal differential input impedance = 100 . | |

| RXP2 RXN2 | 8 9 | 1,CML | Inverting and non - invering CML - compatible differential inputs to the equalizer. Nominal differential input impedance = 100 Q. | |

| RXP3 RXN3 | 11 12 | 1,CML | Inverting and non - inverting CML - compatible differential inputs to the equalizer. Nominal differential input impedance = 100 Q. | |

| TXPO TXNO | 36 35 | O.CML | Inverting and non - inverting CML - compaible diferential outputs from the driver.Nominal differential output impedance =100Q. | |

| TXP1 TXN1 | 33 32 | O.CML | Inverting and non - inverting CML - compatible diferential outputs from the driver.Nominal differential output impedance = 100 Q2. | |

| TXP2 TXN2 | 29 28 | O,CML | Inverting and non - inverting CML - compatible differential outputs from the driver. Nominal differential output impedance=100Q. | |

| TXP3 TXN3 | 26 25 | O.CML | Inverting and non - inverting CML - compatible differential outputs from the driver. Nominal differential output impedance =100 Q. | |

| LOOP FILTER CONNECTION PINS | ||||

| LPF_CP_0 LPFREF_0 | 47 48 | VO,analog | Loop fiter connection Place a 22 nF +10% capacitor between LPF_CP_O and LPF_REF_0 | |

| LPF CP1 LPF REF1 | 38 37 | VO,analog | Loop fiter connection Place a 22 nF ±10% capacitor between LPF_CP_1 and LPF_REF_1 | |

| LPF_CP_2 LPF_REF2 | 23 24 | VO,analog | Loop filter connection Place a 22 nF +10% capacitor between LPF_CP_2 and LPF_REF_2 | |

| LPFCP3 LPF_REF_3 | 14 13 | VO,analog | Loop fiter connection Place a 22 nF+10% capacitor between LPF_CP_3 and LPF_REF_3 | |

| REFERENCE CLOCK I/O | ||||

| REFCLK_IN | 19 | 1,2.5 - V analog | Input is 2.5 V,25 MHz +100 - ppm reference clock from external oscillator | |

| No stringent phase noise requirement | ||||

| REFCLK_OUT | 42 | 0,2.5 - V analog | Output is 2.5 V,buffered replica of reference clock input for connecting multiple DS125RT410 devices on a board | |

| LOCK INDICATOR PINS | ||||

| LOCKO LOCK1 LOCK2 | 45 40 21 | 0.2.5 - V LVCMOS | Output is 2.5 V,the pin is high when CDR ock is attained on the corresponding channel. These pins are shared with SMBus address strap input functions read at start - up. | |

| LOCK3 | 16 | |||

| SMBus MASTER MODE PINS | ||||

| ALL_DONE | 41 | 0.2.5 - V LVCMOS | Output is 2.5 V, the pin goes low to indicate that the SMBus master EEPROM read has been completed. | |

| READ_EN | 44 | L.2.5 - V LVCMOS | Input is 2.5 V, a transition from high to low starts the load from the external EEPROM. The READ_EN pin must be tied low when in SMBus slave mode. | |

| INTERRUPT OUTPUT | ||||

| INT | 43 | O,3.3 - V LVCMOS, Open Drain | Used to signal horizontal or vertical eye opening out of tolerance, loss of signal detect,or CDR unlock External 2 - KQ to 5 - kQ pullup resistor is required. Pin is 3.3 - V LVCMOS tolerant. | |

| SERIAL MANAGEMENT BUS (SMBus) INTERFACE | ||||

| EN_SMB | 20 | 1,2.5 - V analog | Input is 2.5 V, selects SMBus master mode or SMBus slave mode. EN_SMB = High for slave mode EN SMB = Float for master mode Tie READ EN pin low for SMBus slave mode. See Table 4. | |

| SDA | 18 | VO,3.3 - V LVCMOS. Open Drain | Data Input and Open Drain Output External 2 - kQ to 5 - kQpullup resistor is required Pin is 3.3 - V LVCMOS tolerant. | |

| SDC | 17 | VO,3.3 - V LVCMOS, Open Drain | Clock Input and Open Drain Clock Output External 2 - k2 to 5 - k2 pullup resistor is required. Pin is 3.3 - V LVCMOS tolerant. | |

| ADDR_0 ADDR_1 ADDR_2 ADDR_3 | 45 40 21 | 1,2.5 - V LVCMOS | Input is 2.5 V, the ADDR [3:0] pins set the SMBus address for the retimer. These pins are strap inputs. Their state is read on power - up to set the SMBus address in SMBus control mode. High = 1kQ to VDD, Low =1kQ to GND These pins are shared with the lock indicator functions. See Table 1. | |

| POWER | ||||

| VoD | 3,6,7, 10,15, 46 | Power | VoD=2.5V+5% | |

| GND | 2 | Power | Ground reference. | |

| DAP | PAD | Power | Ground reference.The exposed pad at the center of the package must be connected to ground plane of the board with at least 4 vias to lower the ground impedance and improve the thermal performance of the package. |

在實際設計中,需要特別注意各個引腳的電氣特性和連接要求。例如,高速差分輸入輸出引腳需要確保良好的阻抗匹配,以減少信號反射和失真;參考時鐘輸入引腳 REFCLK_IN 要求輸入 2.5 V、25 MHz ±100 ppm 的參考時鐘,雖然對相位噪聲要求不嚴格,但也需保證時鐘的穩定性。

工作原理及功能模塊

數據路徑操作

DS125RT410 的數據路徑主要包括信號檢測、CTLE、CDR 和帶去加重的差分驅動器等功能模塊。信號檢測電路負責監測接收器輸入的能量水平,根據信號的有無自動開啟或關閉高速數據路徑的其余部分,也可通過 SMBus 通道寄存器進行手動控制。

CTLE 功能

CTLE 是一個全自適應均衡器,具有可選的限幅級。在鎖相過程中,CTLE 根據品質因數(FOM)計算進行自適應調整。一旦 CDR 鎖定且 CTLE 完成自適應,其增益水平將保持不變,直到收到手動重新自適應命令或 CDR 重新進入鎖相狀態。CTLE 由 4 級組成,每級具有 2 位增益控制,可提供 256 種不同的級增益組合,其中 32 種組合可用于自適應調整。

CDR 功能

CDR 通過檢測輸入數據流中的位轉換,并將內部 VCO 鎖定到這些位轉換的平均到達時間所代表的時鐘上,從而實現時鐘和數據的恢復。該過程可顯著降低數據流中的抖動,有效重置系統的抖動預算。DS125RT410 使用 25 MHz 參考時鐘來確定內部 VCO 的粗調設置,在加電、CDR 復位以及多次嘗試仍無法重新鎖定時,會利用該參考時鐘對 VCO 頻率進行校準。

輸出驅動器

輸出驅動器能夠提供可變的輸出電壓和模擬去加重。輸出電壓和去加重水平可通過 SMBus 寄存器進行配置,但芯片本身無法自動確定合適的參數,需要用戶根據實際情況進行設置。

設備功能模式

SMBus 主模式和從模式

在 SMBus 主模式下,DS125RT410 上電時從外部 EEPROM 讀取初始配置,完成后切換到從模式,可由外部控制器通過 SMBus 進一步配置。ALL_DONE 和 READ_EN 引腳在主模式下具有特殊功能,用于協調多個芯片在同一 SMBus 上的操作,避免總線沖突。在從模式下,READ_EN 引腳必須接地。

地址線設置

DS125RT410 在主模式和從模式下都需要分配唯一的 SMBus 地址,地址由 ADDR[3:0] 引腳在加電時的狀態確定。如果 READ_EN 引腳未正確設置,可能會導致地址鎖定異常,影響芯片的正常通信。

標準模式操作

DS125RT410 可自動適應多種多頻段數據標準。通過設置特定的寄存器,可限制 VCO 的粗調范圍和分頻比,從而加快鎖相速度。對于不同的標準,還需要設置預期的 PPM 計數和 PPM 計數容差,以確保準確檢測有效頻率鎖定。

編程與寄存器配置

配置模式選擇

DS125RT410 的配置模式由 SMBus 使能引腳(EN_SMB)在上電時的狀態決定,可選擇 SMBus 主模式或從模式。在主模式下,芯片從外部 EEPROM 讀取配置;在從模式下,由外部控制器通過 SMBus 進行配置。

寄存器操作

芯片的寄存器分為控制/共享寄存器和通道寄存器兩類。控制/共享寄存器用于控制或觀察影響所有通道的設置,同時也可選擇目標通道進行通道寄存器的讀寫操作;通道寄存器則用于設置每個通道的具體配置參數。在進行寄存器配置時,需要注意部分寄存器的位字段操作,避免誤操作影響芯片的正常工作。

應用與設計要點

應用場景

DS125RT410 適用于多種高速通信應用,如以太網(10 GbE、1 GbE)、CPRI、Interlaken、InfiniBand 等,可用于前端口 SFF 8431(SFP +)光模塊和直連銅纜、背板延伸和數據重定時等場景。

設計要求

在進行高速印刷電路板設計時,需要考慮以下關鍵因素:

- 使用 100 Ω 差分阻抗走線,確保信號傳輸的穩定性。

- 對連接器過孔和信號過孔進行背鉆處理,以減小過孔殘樁長度,降低信號損耗。

- 使用參考平面過孔,為回流電流提供低電感路徑,減少電磁干擾。

- 將發射鏈路的交流耦合電容放置在靠近接收端的位置,且電容最大尺寸為 0402。

- 為每個 VDD 引腳連接 0.1 μF 的旁路電容,并在電源旁路設計中加入 1 μF 至 10 μF 的電容,以提高電源的穩定性。

典型應用曲線

文檔中給出了不同數據速率下的典型輸出眼圖和 TX 去加重示例,這些曲線有助于工程師在設計過程中評估芯片的性能,并根據實際需求進行參數調整。例如,在 12.5 Gbps 和 10.3125 Gbps 數據速率下,分別展示了默認 $V_{OD}$ 為 600 mVp-p 和不同去加重設置時的輸出眼圖和去加重波形,為設計提供了直觀的參考。

總之,DS125RT410 是一款功能強大、性能優越的四通道重定時器,在高速通信領域具有廣泛的應用前景。但在實際設計中,工程師需要深入理解其特性、功能和設計要點,合理進行引腳連接、寄存器配置和電路板設計,才能充分發揮其性能優勢,實現高質量、可靠的高速數據傳輸。大家在使用過程中有什么問題或者新的發現,歡迎隨時交流。

-

高速通信

+關注

關注

0文章

56瀏覽量

11191

發布評論請先 登錄

DS125RT410 DS125RT410、DS125DF410 低功耗多速率四通道重定時器

DS125DF410 DS125RT410、DS125DF410 低功耗多速率四通道重定時器

DS250DF410 25Gbps多速率4通道重定時器數據表

深入剖析DS125RT410低功耗多速率四通道重定時器

深入剖析DS125RT410低功耗多速率四通道重定時器

評論