RISC-V 的發展背景與全球趨勢

RISC-V 作為新一代開放指令集架構(ISA),已經從學術界的概念研究快速走向全球產業化浪潮。在短短數年內,它從“開源替代方案”成長為全球半導體生態的重要力量,成為 CPU 架構演進中最具活力的選項之一。

1全球崛起:從開源實驗室到產業級生態

RISC-V 的核心優勢來自其開源、免費、可擴展、可裁剪的本質,使其迅速獲得產業界認可。

?RISC-V International(原RISC-V基金會)目前覆蓋70 多個國家、超過 4000 名成員

?生態成員包括:谷歌、英偉達、IBM、Qualcomm、阿里巴巴、三星、西部數據(WD)等全球科技巨頭,同時也吸引了大量初創企業與科研團隊加入。

2市場規模爆發:進入數十億級別的商業時代

過去十年中,RISC-V 從“驗證階段”進入“規模商用階段”,出貨量呈指數增長。

全球市場預測

?2025 年全球 RISC-V 芯片出貨量預計突破 20 億顆。2030 年有望達到數百億片規模,成為全球增長速度最快的 CPU 架構之一。其中約50% 的增長來自中國,包括 AIoT、智能終端、邊緣計算、車規 MCU 等廣泛場景。

AI 加速賽道成為增長引擎

?面向推理、訓練、AI 算子加速的RISC-V AI SoC 有望在未來 5–7 年內達到數十億顆級別的市場規模。由于 RISC-V 可讓企業自由擴展自定義指令(如矩陣運算、向量引擎等),非常適合構建輕量級、高能效比的 AI 加速芯片。

3技術競爭格局:向 “X86 + Arm + RISC-V” 三足鼎立演變

RISC-V 的開放性和可擴展性正在改變傳統 CPU 的競爭邏輯。全球 CPU 架構正步入新的競爭平衡點。隨著 RISC-V 的生態加速完善、工具鏈不斷成熟、商業化案例逐年增多,行業開始出現明確趨勢:CPU 架構體系正從“兩極格局”走向“X86 + Arm + RISC-V”三足鼎立的新階段。

RISC-V 時代的驗證挑戰

從測試的角度看,RISC-V 與 x86 / Arm 的驗證本質上并無“架構本身決定的難點差異”, 真正的差別在于:RISC-V 的靈活性遠高于傳統架構,但行業尚缺乏成熟的工具鏈、案例和 SOP,因此“驗證經驗不夠沉淀”。

因此,RISC-V 測試中普遍會遇到三個現實挑戰:

(1)缺少可復用的驗證流程

不同公司、不同項目、不同自定義 ISA 都有自己的驗證方法,沒有形成像 Arm/x86 那樣的標準化路徑。

(2)缺少全過程的一致性測試驗證

EDA 仿真一套語言,硅測一套語言,系統調試又是一套,結果常常無法連貫,一致性缺失。

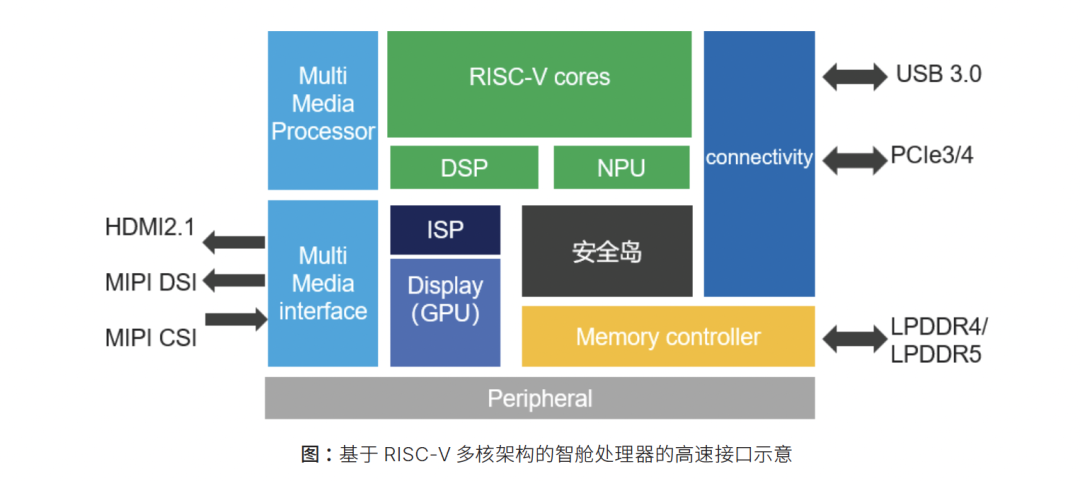

(3)缺少成熟的高速接口調試經驗

當 RISC-V 芯片開始進入 AI、汽車、數據中心等高端場景,高速接口(PCIe、DDR、CXL、Ethernet)成為真正的痛點來源。

綜上所述,RISC-V 的驗證難點不在于“架構難”,而在于生態仍缺乏一條真正完整、協同、連貫的End-to-End 驗證鏈路——從前仿真,到半實物平臺,再到硅測與系統級驗證。

是德科技的完整驗證方案

(從ADS仿真到后硅測試)

面對RISC-V芯片設計和驗證的多重挑戰,是德科技(Keysight)則是從仿真、半實物仿真、無源測試驗證、有源測試、功能和系統測試,以及用相同的算法拉通全過程來加速這一過程。其核心理念是在產品開發全流程中形成“閉環”驗證鏈路解決方案。下圖是PCB/Cable/Fixture設計和驗證的仿測閉環流程實例。

圖:是德科技的PLTS物理層測試方案和ADS仿真軟件形成仿測閉環驗證

在設計階段,是德科技的ADS (Advanced Design System) 等EDA仿真工具發揮關鍵作用。工程師可以利用ADS對高速接口電信道進行信號完整性(SI)仿真、對電源分配網絡進行電源完整性(PI)分析。例如,通過ADS的PIPro模塊可以仿真芯片/板級電源網絡的IR壓降和阻抗分布,預測不同去耦方案對電壓紋波的影響。對于PCIe、DDR、以太網等高速鏈路,則可在ADS中建立拓撲模型,進行時域與頻域仿真,評估插損、抖動、眼圖裕量是否滿足標準要求。這些仿真能夠在設計初期階段發現潛在信號/電源問題,指導硬件布局布線和IP參數選型,避免走線不良或電源噪聲過大導致后期整改。

進入產品實現階段后,是德科技提供一系列尖端測試測量設備,幫助工程師驗證實際芯片和系統與仿真預期一致,完成最終的硅后驗證。例如,使用超高帶寬實時示波器(如Keysight UXR系列)測量高速接口的發射信號眼圖和抖動,對比仿真得到的眼圖指標,驗證設計裕量;利用矢量網絡分析儀(VNA)對封裝、PCB走線和連接器的S參數進行測量,并通過去嵌技術除去治具影響,將實測信道特性與ADS仿真模型對應比對,從而校準模型精度。同時,是德科技的測試方案注重自動化和相關性:許多儀器配套軟件可自動執行標準一致性測試,用腳本一次性跑完整套用例并生成報告;仿真結果和測量數據可以在同一平臺下關聯分析,幫助快速定位差異原因,實現設計與測試的無縫銜接。

通過將前端設計仿真與后端硬件測試緊密耦合,是德科技構建了一個覆蓋RISC-V芯片全生命周期的驗證閉環。這種方案能夠在實驗室里重現復雜的場景,提早暴露問題并指導設計改進,避免流片后才發現紕漏而被迫修復。事實證明,借助仿真-實測閉環,可以顯著降低開發風險和成本——例如在高速接口設計中,仿真階段鎖定優化參數可減少一次PCB迭代。憑借深厚的技術積累,是德科技構筑的這一完整驗證鏈路,為RISC-V芯片從概念到落地保駕護航,幫助工程師大幅提升驗證信心和效率。

對于芯粒測試,ADS仿真、去嵌、和物理層測試方案的結合顯得更加必要,下圖是芯粒測試的流程實例。

圖:芯粒測試的流程

PCIe、DDR、CXL、Ethernet、

電源/信號完整性測試場景概覽

RISC-V芯片要在各種應用中可靠運行,離不開對其高速接口和板級性能的嚴格測試。是德科技的方案廣泛覆蓋了主流接口標準和完整性驗證需求,典型場景包括:

?PCI Express (PCIe):無論是在數據中心將RISC-V處理器與GPU加速卡相連,還是在嵌入式設備中擴展高速外設,總線接口PCIe都是關鍵紐帶。是德科技提供從PCIe 1.0到最新6.0的物理層和協議層一致性測試方案,可對發射端眼圖和抖動、信道插損和回損、接收端誤碼率等進行全面測量。配套的協議分析儀和協議發生器則用于驗證鏈路訓練狀態機(LTSSM)、錯誤處理等協議行為。借助如UXR系列示波器、M8000A系列誤碼儀、PNA/PNA-X/PNA-L矢量網絡分析儀及P5570A 和 P5573A PCIe 6.0 協議分析儀測試工具,工程師能夠高效完成PCIe鏈路的一致性認證和調試,確保RISC-V芯片與現有PCIe生態無縫互通。

?DDR內存接口:RISC-V處理器廣泛用于高性能計算和AI加速時,常需連接高速DDR/LPDDR內存。是德科技的解決方案覆蓋DDR3/4/5及LPDDR5/6等標準,從時鐘抖動、信號眼圖、命令總線時序到電壓噪聲均有針對性的測試項目。通過高帶寬示波器配合DDR一致性測試軟件,可自動化測量讀寫眼高/眼寬、時序參數(tDQSQ、tDQSCK等)是否達標;結合誤碼儀可以模擬加擾噪聲驗證數據可靠性。此外,是德科技還提供前仿真到后測量的一體化DDR分析工具:IBIS模型仿真布線拓撲,實測S參數比對仿真眼圖,幫助客戶在DDR接口設計中實現仿真-測試閉環,平滑升級到新一代存儲器。

?CXL高速互連:Compute Express Link (CXL)是新興的基于PCIe的緩存一致性互連,總線標準復雜且要求嚴格。針對采用CXL架構的RISC-V 芯片,是德科技的PCIe5.0/6.0測試平臺同樣適用:能夠測量CXL鏈路的物理層信號質量,并通過協議分析儀驗證CXL的一致性協議(如內存緩存一致性、設備內存映射)是否正確實現。利用Keysight提供的PCIe/CXL協議觸發和解碼工具,可以在鏈路訓練、讀寫事務中捕獲異常,確保RISC-V芯片在CXL互連下數據一致且延遲可控。

?高速以太網 (Ethernet):許多RISC-V應用(例如網絡處理器、物聯網網關等)需要支持千兆乃至更高速率的以太網通信。是德科技具備從1GbE到400GbE/800GbE以太網物理層的一體化測試能力。通過誤碼儀和示波器相結合,可測試高速SERDES鏈路的誤碼率、抖動容限和眼圖裕度;使用矢量網絡分析儀能評估高速差分線路的特性阻抗匹配和模式轉換。針對以太網標準,還支持自動一致性測試套件,覆蓋IEEE規范要求的電氣參數測試,幫助工程師快速判斷設計是否符合Ethernet標準。無論是板上走線還是光模塊接口,都可以在Keysight平臺上完成全面的物理層驗證,為RISC-V芯片的網絡通信功能提供信心保障。

?電源和信號完整性 (PI/SI):隨著芯片工藝和速率的提升,板級電源穩定與信號質量對系統性能的影響愈發突出。是德科技將PI/SI測試納入驗證鏈路中,提供專門工具監控和優化這些“看不見”的細節。例如,通過高速示波器配合電源軌探頭,可以測量芯片供電的瞬態紋波噪聲,并使用專用分析軟件評估電源噪聲對高速數據眼圖的影響。在信號完整性方面,利用矢量網絡分析儀獲取走線的S參數后,工程師可以在ADS里仿真不同補償方案(如預加重、均衡),再將其應用于實際電路驗證效果。此外,Keysight提供抖動/干擾注入工具,可在實驗室重現極端干擾場景,檢驗RISC-V芯片的抗擾裕度。通過這一系列軟硬件手段,電源和信號完整性問題能夠在設計早期就被發現并解決,確保最終產品在苛刻環境下依然穩定工作。

綜上,是德科技構建了覆蓋PCIe 1.0~6.0、DDR3~5/LPDDR6、Ethernet 400G/800G等各類高速接口,以及板級SI/PI性能的完整測試方案,涵蓋了從發送端、信道到接收端的全流程驗證。通過模塊化的軟硬件組合,該方案幾乎囊括了RISC-V芯片可能涉及的所有測試場景,真正做到一站式保障芯片各方面指標的符合性和可靠性。

從實驗室到落地現場

在與達摩院、知合計算等公司合作中,是德科技已幫助多個RISC-V芯片項目順利從設計走向商用。正是這些真實場景的驗證實踐,讓RISC-V項目得以大規模量產落地。

本次我們也特別邀請了達摩院、知合計算的專家來分享實踐經驗,歡迎點擊下方鏈接預約直播?

結語:從開放指令集到驗證閉環的落地路徑

開放的RISC-V指令集正為計算產業帶來創新活力,但要將這份潛力轉化為可靠的產品,完善的驗證閉環至關重要。針對RISC-V芯片設計彈性大、驗證難度高的特點,是德科技以其專業測試測量能力打造了從仿真到測試的全覆蓋解決方案,彌合了設計預期與實際性能之間的鴻溝。在這種閉環驗證思路的護航下,RISC-V芯片的開發風險大大降低,創新者們可以更大膽地探索定制化設計而無后顧之憂。

展望未來,RISC-V就像給算力生態開辟了一個“新接口”:它既能與現有的GPU、PCIe、以太網等體系協同合作,又能玩出指令級和架構級定制的新花樣。隨著軟硬件生態日趨成熟,有了從設計到測試的閉環保障,RISC-V的落地之路將更加穩健而快捷。或許再過幾年,我們日常使用的手機、電腦、智能汽車中都將出現RISC-V芯片的身影。是德科技將持續深耕測試測量技術,攜手產業伙伴完善這一開放架構的驗證體系,加速邁向一個開放創新、閉環可靠的RISC-V新時代。

關于是德科技

是德科技(NYSE:KEYS)啟迪并賦能創新者,助力他們將改變世界的技術帶入生活。作為一家標準普爾 500 指數公司,我們提供先進的設計、仿真和測試解決方案,旨在幫助工程師在整個產品生命周期中更快地完成開發和部署,同時控制好風險。我們的客戶遍及全球通信、工業自動化、航空航天與國防、汽車、半導體和通用電子等市場。我們與客戶攜手,加速創新,創造一個安全互聯的世界。

-

cpu

+關注

關注

68文章

11304瀏覽量

225472 -

仿真

+關注

關注

55文章

4505瀏覽量

138509 -

AI

+關注

關注

91文章

40384瀏覽量

301961 -

RISC-V

+關注

關注

49文章

2918瀏覽量

53254

原文標題:RISC-V芯片:如何打造仿真到測試的完整驗證閉環

文章出處:【微信號:是德科技KEYSIGHT,微信公眾號:是德科技KEYSIGHT】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

risc-v多核芯片在AI方面的應用

risc-v的mcu對RTOS兼容性如何

RISC-V 工具鏈簡介

risc-v芯片在電機領域的應用展望

RISC-V應用領域的拓展

RISC-V工具鏈簡介

RISC-V工具鏈簡介

我了解的RISC-V

RISC-V,正在擺脫低端

基于RISC-V開放架構的存算一體化芯片解決方案

SK hynix公司使用是德科技PCIe測試解決方案驗證計算快速鏈路技術

基于形式的高效 RISC-V 處理器驗證方法

是德科技RISC-V芯片完整驗證鏈路解決方案

是德科技RISC-V芯片完整驗證鏈路解決方案

評論